Изобретение относится к вычислительной технике и может быть использовано при построении устройств индикации цифровой информации.

Цель изобретения - расширение области применения путем обеспечения возможности индикации двух индицируемых сигналов.

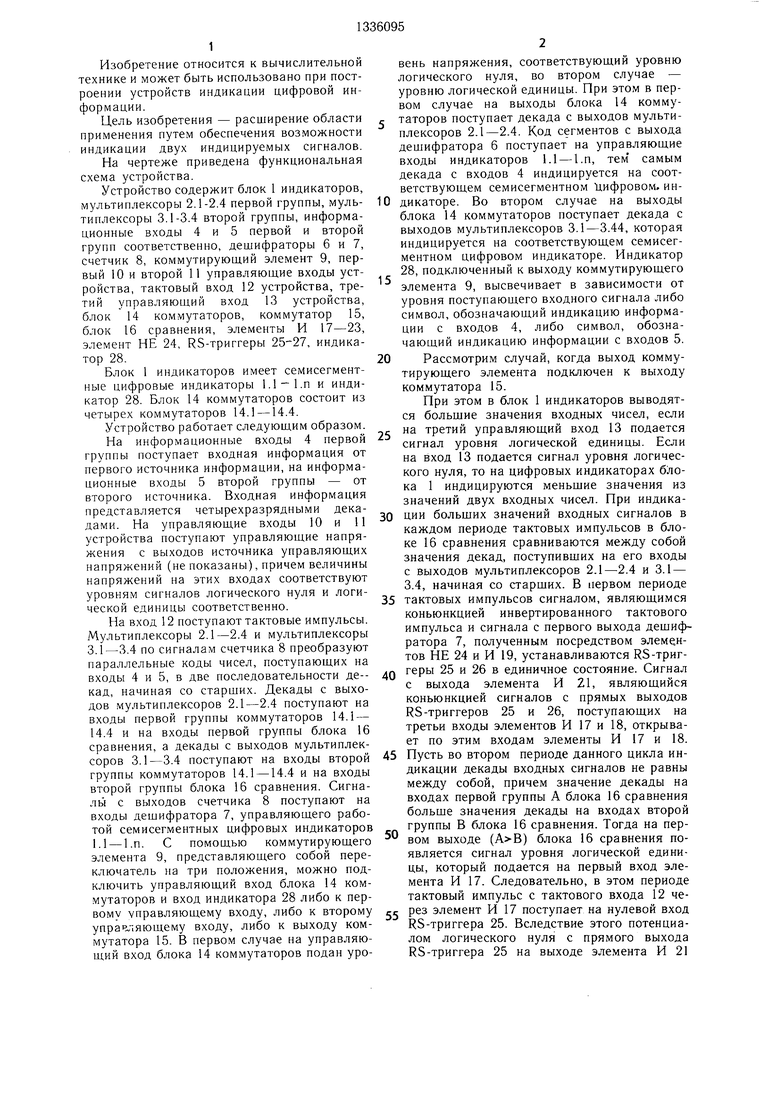

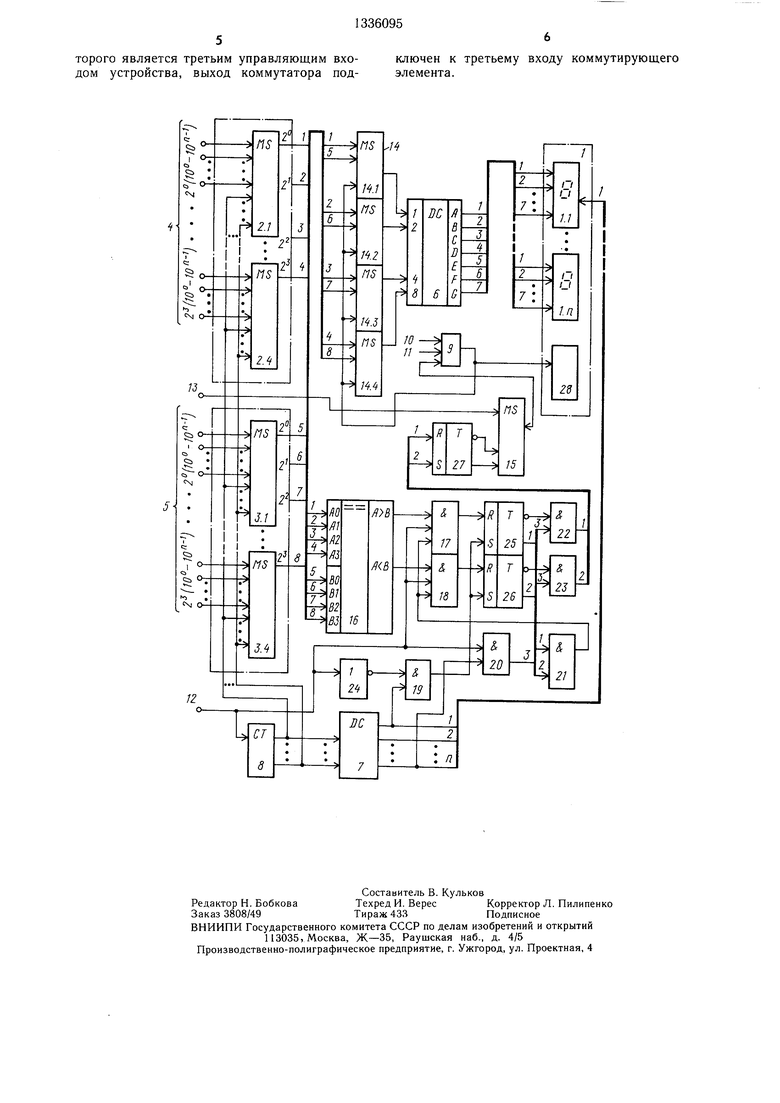

На чертеже приведена функциональная схема устройства.

Устройство содержит блок 1 индикаторов, мультиплексоры 2.1-2.4 первой группы, мультиплексоры 3.1-3.4 второй группы, информационные входы 4 и 5 первой и второй групп соответственно, дешифраторы б и 7, счетчик 8, коммутирующий элемент 9, первый 10 и второй 11 управляющие входы устройства, тактовый вход 12 устройства, третий управляющий вход 13 устройства, блок 14 коммутаторов, коммутатор 15, блок 16 сравнения, элементы И 17-23, элемент НЕ 24, RS-триггеры 25-27, индикатор 28.

Блок 1 индикаторов имеет семисегмент- ные цифровые индикаторы 1.1-l.n и индикатор 28. Блок 14 коммутаторов состоит из четырех коммутаторов 14.1 -14.4.

Устройство работает следующим образом.

На информационные входы 4 первой группы поступает входная информация от первого источника информации, на информационные входы 5 второй группы - от второго источника. Входная информация представляется четырехразрядными декадами. На управляющие входы 10 и 11 устройства поступают управляющие напряжения с выходов источника управляющих напряжений (не показаны), причем величины напряжений на этих входах соответствуют уровням сигналов логического нуля и логической единицы соответственно.

На вход 12 поступают тактовые импульсы. Мультиплексоры 2.1-2.4 и мультиплексоры 3.1-3.4 по сигналам счетчика 8 преобразуют параллельные коды чисел, поступающих на входы 4 и 5, в две последовательности де-- кад, начиная со старших. Декады с выходов мультиплексоров 2.1-2.4 поступают на входы первой группы коммутаторов 14.1 - 14.4 и на входы первой группы блока 16 сравнения, а декады с выходов мультиплексоров 3.1-3.4 поступают на входы второй группы коммутаторов 14.1 -14.4 и на входы второй группы блока 16 сравнения. Сигна- ль 1 с выходов счетчика 8 поступают на входы дешифратора 7, управляющего работой семисегментных цифровых индикаторов 1.1 - 1.П. С помощью коммутирующего элемента 9, представляющего собой переключатель на три положения, можно подключить управляющий вход блока 14 коммутаторов и вход индикатора 28 либо к первому управляющему входу, либо к второму управляющему входу, либо к выходу коммутатора 15. В первом случае на управляющий вход блока 14 коммутаторов подан уровень напряжения, соответствующий уровню логического нуля, во втором случае - уровню логической единицы. При этом в первом случае на выходы блока 14 коммутаторов поступает декада с выходов мультиплексоров 2.1-2.4. Код сегментов с выхода дещифратора 6 поступает на управляющие входы индикаторов 1.1 - l.n, тем самым декада с входов 4 индицируется на соответствующем семисегментном цифровом, ин0 дикаторе. Во втором случае на выходы блока 14 коммутаторов поступает декада с выходов мультиплексоров 3.1-3.44, которая индицируется на соответствующем семисегментном цифровом индикаторе. Индикатор 28, подключенный к выходу коммутирующего элемента 9, высвечивает в зависимости от уровня поступающего входного сигнала либо символ, обозначающий индикацию информации с входов 4, либо символ, обозначающий индикацию информации с входов 5.

0 Рассмотрим случай, когда выход коммутирующего элемента подключен к выходу коммутатора 15.

При этом в блок 1 индикаторов выводятся большие значения входных чисел, если

5 на третий управляющий вход 13 подается сигнал уровня логической единицы. Если на вход 13 подается сигнал уровня логического нуля, то на цифровых индикаторах блока 1 индицируются меньшие значения из значений двух входных чисел. При индика0 Ции больших значений входных сигналов в каждом периоде тактовых импульсов в блоке 16 сравнения сравниваются между собой значения декад, поступивщих на его входы с выходов мультиплексоров 2.1-2.4 и 3.1 - 3.4, начиная со старщих. В нервом периоде

5 тактовых импульсов сигналом, являющимся коньюнкцией инвертированного тактового импульса и сигнала с первого выхода дещифратора 7, полученным посредством элементов НЕ 24 и И 19, устанавливаются RS-тригQ геры 25 и 26 в единичное состояние. Сигнал с выхода элемента И 21, являющийся коньюнкцией сигналов с прямых выходов RS-триггеров 25 и 26, поступающих на третьи входы элементов И 17 и 18, открывает по этим входам элементы И 17 и 18.

5 Пусть во втором периоде данного цикла индикации декады входных сигналов не равны между собой, причем значение декады на входах первой группы А блока 16 сравнения больще значения декады на входах второй группы В блока 16 сравнения. Тогда на пер вом выходе () блока 16 сравнения появляется сигнал уровня логической единицы, который подается на первый вход элемента И 17. Следовательно, в этом периоде тактовый импульс с тактового входа 12 че5 рез элемент И 17 поступает на нулевой вход RS-триггера 25. Вследствие этого потенциалом логического нуля с прямого выхода RS-триггера 25 на выходе элемента И 21

устанавливается нулевой уровень сигнала, который закрывает элементы И 17 и 18 до первого такта следующего цикла индикации. В последнем такте данного цикла индикации сигнал, являющийся конъюнкцией тактового импульса и сигнала с последнего выхода дешифратора 7, формируемый элементом И 20, поступает с его выхода через открытый сигналом с инверсного выхода RS-триг- гера 25 (элемент И 22) на нулевой вход RS-триггера 27. Сигнал уровня логического нуля с прямого выхода этого триггера через коммутатор 15 и коммутирующий элемент 9 поступает на управляющие входы коммутаторов 14.1 -14.4. Поэтому в следующем цикле индикации через коммутаторы 14.1 - 14.4. на индикацию проходят декады входного числа с входов 4.

Рассмомтрим случай, когда сравниваемые декады равны между собой. Элементы И 17 и 18 остаются закрытыми. Ни один из триггеров 25 и 26 не устанавливается в нулевое состояние. Следовательно, элементы И 22 и 23 Б последнем такте также закрыты, вследствие чего RS-триггер 27 остается Б прежнем состоянии и Б данном цикле индицируется по-прежнему значение сигнала с входа 4. Пусть в рассматриваемом цикле в третьем такте значение декады с выходов мультиплексоров 2.1-2.4 меньще зн аче- ния декады с выходов мультиплексоров 3.1-3.4. Поэтому тактовый импульс через открытый элемент И 18 устанавливает в нулевое состояние RS-триггер 26, который сигналом со своего прямого выхода через элемент И 21 закрывает элементы И 17 и 18, а сигналом с инверсного выхода открывает элемент И 23. В последнем такте этого цикла импульс с выхода элемента И 20 через открытый элемент И 23 устанавливает iRS- триггер 17 в единичное состояние. Сигнал единичного уровня с прямого выхода этого триггера через коммутатор 15 и коммутирующий элемент 9 поступает на управляющие входы коммутаторов 14.1 -14.4 блока 14 коммутаторов. Следовательно, в следующем цикле на цифровых индикаторах 1.1 - l.n блока высвечивается значение числа с входов 5 устройства.

При индикации меньщего значения из значений двух входных чисел устройство работает аналогично, за исключением того, что сигнал с уровня логического нуля с входа переключения 13 пропускает на управляющие входы коммутаторов 14.1 -14.4 блока 14 коммутаторов сигналы не с прямого выхода RS-триггера 27, а с инверсного.

Таким образом, с помощью вновь введенных блоков и их связей с известными блоками предлагаемое устройство обеспечивает возможность индикации неравенства двух индицируемых сигналов, что расширяет область применения устройства.

0

5

0

5

0

5

0

5

0

5

Формула изобретения Устройство для цифровой индикации, содержащее мультиплексоры первой группы, информационные входы которых являются информационными входами первой группы устройства, мультиплексоры второй группы, информационные входы которых являются информационными входами второй группы устройства, управляющие входы мультиплексоров первой и второй групп соединены с выходами счетчика, счетный вход которого является тактовым входом устройства, первый дешифратор, выходы которого подключены к информационным входам группы блока индикаторов, управляющие входы которого соединены с выходами второго дешифратора, входы которого подключены к выходам счетчика, коммутирующий элемент, первый и второй входы которого являются соответственно первым и вторым управляюп1.ими входами устройства, отличающееся тем, что, с целью расщирения области применения устройства путем обеспечения возможности индикации неравенства двух индицируемых сигналов, в него введены три триггера, элемент НЕ, семь элементов И, коммутатор, блок сравнения и блок коммутаторов, управляющий вход которого подключен к информационному входу блока индикаторов и выходу коммутирующего элемента, информационные входы соединены с выходами мультиплексоров первой и второй групп, а выходы - с входами первого дешифратора, входы первой и второй групп блока сравнения подключены к выходам мультиплексоров первой и второй групп соответственно, а первый и второй выходы - к первым входам первого и второго элементов И, вторые входы которых соединены с входом элемента НЕ и счетным входом счетчика, выход элемента НЕ подключен к первому входу третьего элемента И, второй вход которого соединен с первым выходом второго дешифратора, первый вход четвертого элемента И подключен к входу элемента НЕ, а второй вход - к последнему выходу второго дешифратора, нулевые входы первого и второго триггеров соединены с выходами первого и второго элементов И соответственно, а единичные входы - с выходом третьего элемента И, входы пятого элемента И подключены к единичным выходам первого и второго триггеров, нулевые выходы которых соединены с первыми входами шестого и седьмого элементов И соответственно, вторые входы шестого и седьмого элементов И подключены к выходу четвертого элемента И, выход пятого элемента И соединен с третьими входами первого и второго элементов И, выходы шестого и седьмого элементов И подключены соответственно к нулевому и единичному входам третьего триггера, выходы которого соединены с информационными входами коммутатора, управляющий вход которого является третьим управляющим входом устройства, выход коммутатора подключен к третьему входу коммутирующего элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой индикации | 1986 |

|

SU1336094A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Устройство цифровой индикации положения сосуда шахтной подъемной машины | 1987 |

|

SU1474061A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 1995 |

|

RU2138910C1 |

| Устройство для индикации | 1982 |

|

SU1057982A1 |

| Программируемое устройство для вычисления логических функций | 1987 |

|

SU1444744A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении устройств для индикации цифровой информации. Целью изобретения является расширение области применения устройства за счет обеспечения возможности индикации неравенства двух индицируемых сигналов. Поставленная цель достигается тем, что в устройство, содержащее мультиплексоры первой и второй групп, информационные входы которых являются информационными входами первой и второй групп соответственно, а управляющие входы подключены к выходам счетчика, соединенным с входами второго дешифратора, выходы которого подключены к управляющим входам блока индикаторов, информационные входы группы которого соединены с выходами первого д.ещифратора, счетный вход счетчика является тактовым входом устройства, коммутационный элемент, входы которого являются управляющими входами устройства, введены три триггера, элемент НЕ, семь элементов И, коммутатор, блок сравнения и блок коммутаторов. Введение указанных функциональных блоков и их связей с известными блоками устройства позволяет расширить область его применения за счет возможности индикации неравенства информации, поступающей с выходов двух источников. 1 ил. S (Л оо со Oi со СП

| Устройство для цифровой индикации | 1981 |

|

SU1045226A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приборы и техника эксперимента, 1982, № 4, с | |||

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-01—Подача