iC

4 4

Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления логических функций п переменных.

Цель изобретения - повьшение быстродействия устройства за счет обеспечения возможности вычисления за один такт каждой конъюктивной группы функции, представленной в дизъюнктивной нормальной форме (ДНФ).

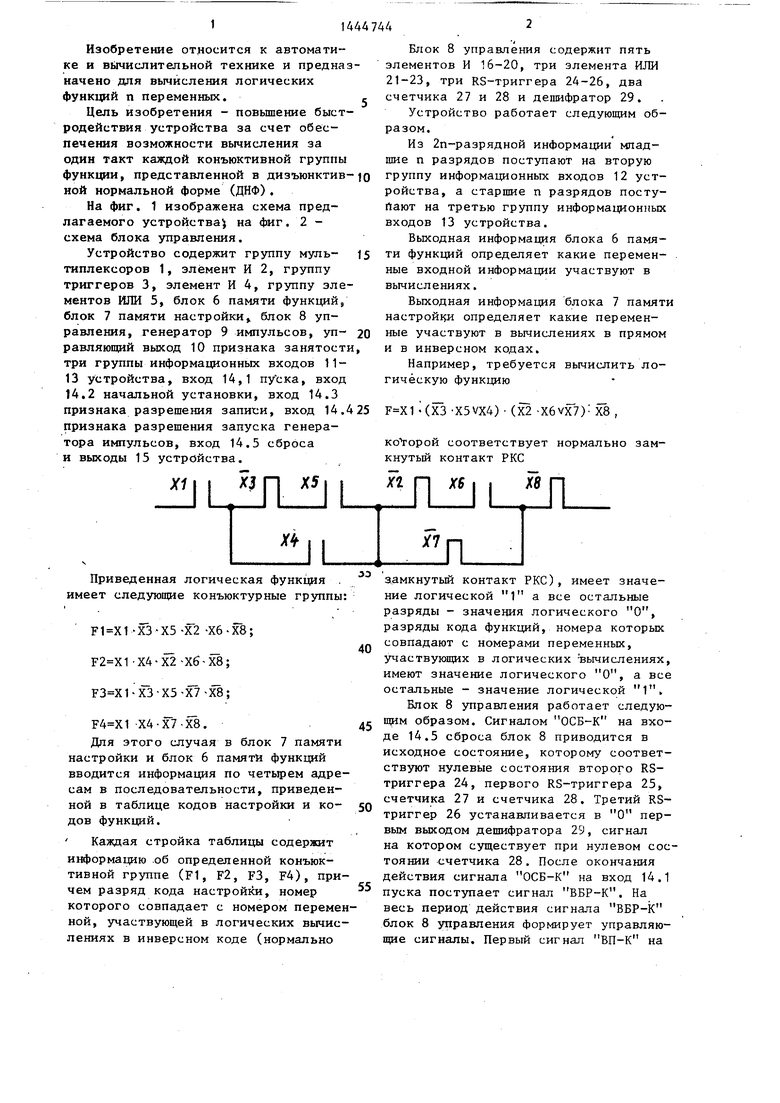

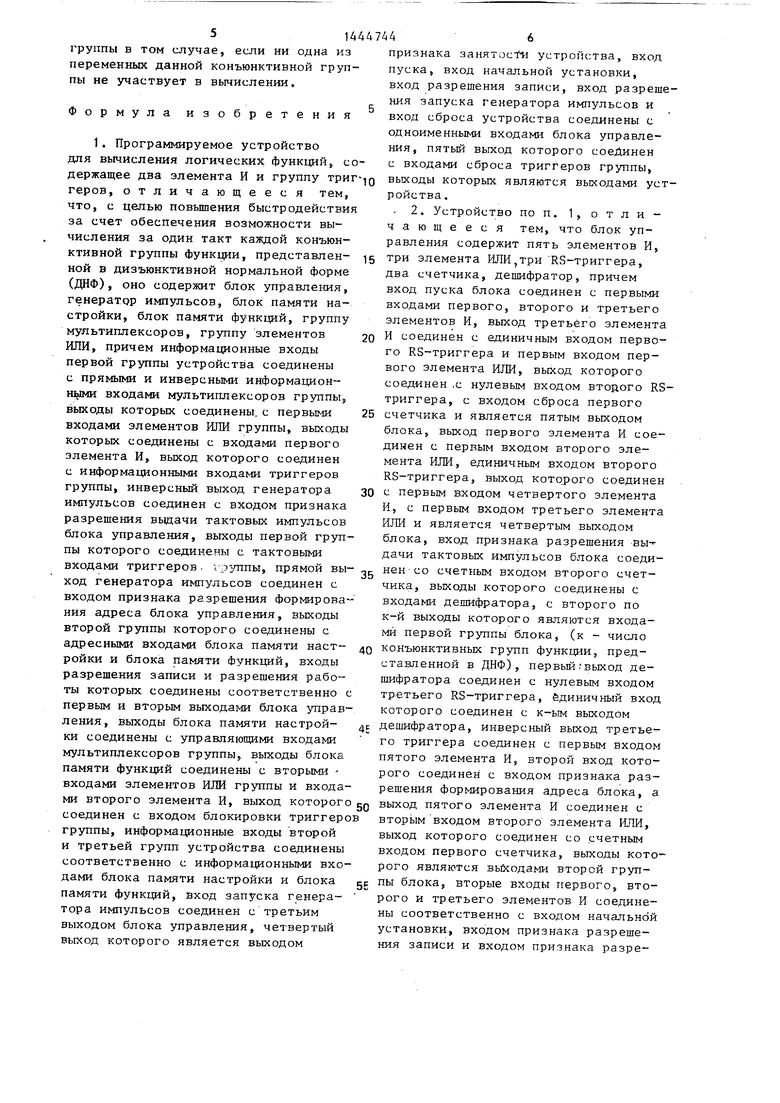

На фиг. 1 изображена схема предлагаемого устройства на фиг. 2 - схема блока управления.

Устройство содержит группу муль- типлексоров 1, элемент И 2, группу триггеров 3, элемент И 4, группу элементов ИЛИ 5, блок 6 памяти функций, блок 7 памяти настройки блок 8 управления, генератор 9 импульсов, уп- равляющий выход 10 признака занятости три группы информационных входов 11- 13 устройства, вход 14,1 пуска, вход 14.2 начальной установки, вход 14.3 признака разрешения записи, вход 14.4 признака разрешения запуска генератора импульсов, вход 14.5 сброса и выходы 15 устройства.

Блок 8 управления содержит пять элементов И 16-20, три элемента ИЛИ 21-23, три RS-триггера 24-26, два счетчика 27 и 28 и дешифратор 29.

Устройство работает следующим образом.

Из 2п-разрядной информации младшие п разрядов поступают на вторую группу информационных входов 12 устройства, а старшие п разрядов поступают на третью группу информационных входов 13 устройства.

Выходная информация блока 6 памяти функций определяет какие перемен- ные входной информации участвуют в вычислениях.

Выходная информация блока 7 памят настройки определяет какие переменные участвуют в вычислениях в прямом и в инверсном кодах.

Например, требуется вычислить логическую функцию

(ХЗ X5VX4)(Х2-X6VX7) Х8 ,

которой соответствует нормально зам- кнутьй контакт РКС

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| Устройство для определения значений булевых функций | 1987 |

|

SU1508204A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для формирования и передачи сообщения | 1990 |

|

SU1778767A1 |

| Устройство для ввода-вывода дискретных сигналов микроЭВМ | 1989 |

|

SU1681306A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2007751C1 |

| Микропрограммное устройство управления | 1985 |

|

SU1354192A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1987 |

|

SU1503043A1 |

Изобретение относится к области вычислительной техники и предназначено для вычисления логических функций п переменных. Целью изобретения является повышение быстродействия за счет возможности вычисления за один такт каждой конъюктивной группы функции, представленной в дизъюнктивной нормальной форме (ДНФ). Устройство содержит группу мультиплексоров 1, элемент И 2, группу триггеров 3, элемент И 4, группу элементов ИЛИ 5, блок 6 памяти функций, блок 7 памяти настройки, блок 8 управления, генератор 9 импульсов. На информационные входы первой группы подаются входные переменные, на информационные входы второй и третьей групп подается информация, преобразуемая в код настройки и код функции, которые формируют результат вычисления логической функции, представленной в ДНФ. 2 ил. 1 табл.,1 э.п. ф-лы. (Л

XI

ХЛП

Х5

Приведенная логическая функция . имеет следуюш ие конъюктурные группы:

ХЗ-Х5-Х2 -Хб-Хв;

F2 X1 X4-X2-X6-X8;

F3 X1-X3-X5-X7-X8;

Х4-Х7-Х8.

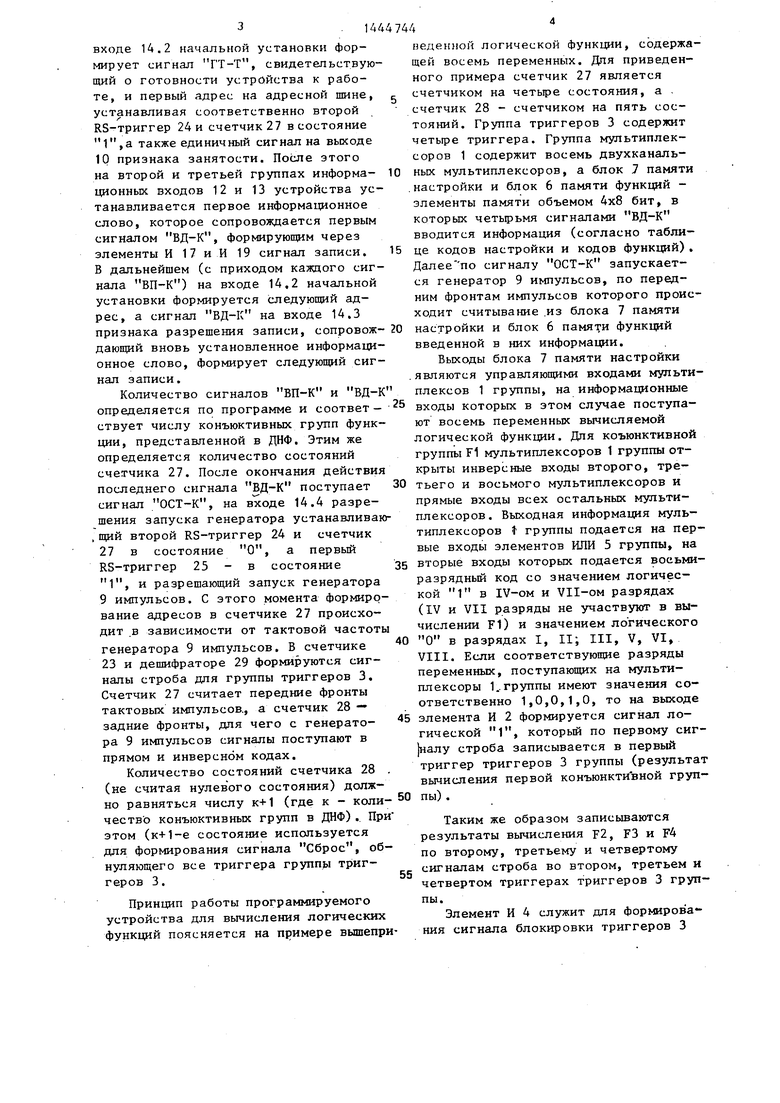

Для этого случая в блок 7 памяти настройки и блок 6 памяти функций вводится информация по четырем адресам в последовательности, приведенной в таблице кодов настройки и ко- дов функций.

Каждая стройка таблицы содержит информацию .об определенной конъюктивной группе (F1, F2, F3, F4), причем разряд кода настройки, номер которого совпадает с номером переменной, участвующей в логических вычислениях в инверсном коде (нормально

хг

Х6

Х8

замкнутый контакт РКС), имеет значение логической 1 а все остальные разряды - значения логического О, разряды кода функций, номера которых совпадают с номерами переменных, участвующих в логических - вычислениях, имеют значение логического О, а все остальные - значение логической 1.

Блок 8 управления работает следую- 1ЩМ образом. Сигналом ОСБ-К на входе 14.5 сброса блок 8 приводится в исходное состояние, которому соответствуют нулевые состояния второго RS- триггера 24, первого RS-триггера 25, счетчика 27 и счетчика 28. Третий RS- триггер 26 устанавливается в О первым выходом дешифратора 29, сигнал на котором существует при нулевом состоянии счетчика 28. После окончания действия сигнала ОСБ-К на вход 14.1 пуска поступает сигнал ВБР-К. На весь период действия сигнала ВБР-К блок 8 управления формирует управляющие сигналы. Первый сигнал ВП-К на

входе 14.2 начальной установки формирует сигнал ГТ-Т, свидетельствующий о готовности устройства к работе, и первый адрес на адресной шине, устанавливая соответственно второй RS-триггер 24 и счетчик 27 в состояние 1,а также единичный сигнал на выходе 10 признака занятости. После этого на второй и третьей группах информационных входов 12 и 13 устройства устанавливается первое информационное слово, которое сопровождается первым сигналом ВД-К, формирующим через элементы И 17 и И 19 сигнал записи. В дальнейшем (с приходом каждого сигнала ВП-К) на входе 14,2 начальной установки формируется следующий адрес, а сигнал ВД-К на входе 14.3

признака разрешения записи, сопровож- 20 настройки и блок 6 памяти функщй

дающий вновь установленное информационное слово, формирует следующий сигнал записи.

Количество сигналов ВП-К и ВД-К определяется по программе и соответ - ствует числу конъюктивных групп функции, представленной в ДНФ. Этим же определяется количество состояний счетчика 27. После окончания действия последнего сигнала ВД-К поступает сигнал ОСТ-К, на входе 14.4 разрешения запуска генератора устанавливаю- ,щий второй RS-триггер 24 и счетчик 27 в состояние О, а первый RS-триггер 25 - в состояние 1, и разрешающий запуск генератора 9 импульсов. С этого момента формирование адресов в счетчике 27 происходит .в зависимости от тактовой частоты генератора 9 импульсов. В счетчике 23 и дешифраторе 29 формируются сигналы строба для группы триггеров 3, Счетчик 27 считает передние фронты тактовых импульсов., а счетчик 28 - задние фронты, для чего с генератора 9 импульсов сигналы поступают в прямом и инверсном кодах.

Количество состояний счетчика 28 . (не считая нулевого состояния) долж25

30

введенной в них информации.

Выходы блока 7 памяти настрой являются управляющими входами мул плексов 1 группы, на информацион входы которых в этом случае пост ют восемь переменных вычисляемой логической функции. Для коъюнкти группы F1 мультиплексоров 1 группы крыты инверсные входы второго, тр тьего и восьмого мультиплексоров прямые входы всех остальных муль плексоров . Выходная информация м типлексоров t группы подается на вые входы элементов ИЛИ 5 группы вторые входы которых подается вос разрядный код со значением логич кой 1 в IV-OM и VII-OM разрядах (IV и VII разряды не участвуют в числении F1) и значением логическ О в разрядах I, II; III, V, VI VIII. Если соответствующие разряд переменных, поступающих на мульти плексоры 1..группы имеют значения ответственно 1,0,0,1,0, то на вы 45 элемента И 2 формируется сигнал л гической 1, который по первому )налу строба записывается в первый триггер триггеров 3 группы (резул вычисления первой конъюнктивной

35

40

но равняться числу к-ь1 (где к - коли- пы) . честно конъюктивных групп в ДНФ) .. При Таким же образом записываются этом (к+1-е состояние используется для формирования сигнала Сброс, обнуляющего все триггера группы триг3.55

г ер он

Принцип работы программируемого устройства для вычисления логических функций поясняется на примере вышеприрезультаты вычисления F2, F3 и F4 по второму, третьему и четвертому сигналам строба во втором, треть четвертом триггерах триггеров 3 пы.

Элемент И 4 служит дпя формир ния сигнала блокировки триггеров

рзеденной логической функции, содержащей восемь переменных. Для приведенного примера счетчик 27 является

счетчиком на четыре состояния, а , счетчик 28 - счетчиком на пять состояний. Группа триггеров 3 содержит четыре триггера. Группа мультиплексоров 1 содержит восемь двухканальных мультиплексоров, а блок 7 памяти .настройки и блок 6 памяти функций - элементы памяти объемом 4x8 бит, в которых четырьмя сигналами ВД-К вводится информация (согласно табли-

це кодов настройки и кодов функций). Далее по сигналу ОСТ-К запускается генератор 9 импульсов, по передним фронтам импульсов которого происходит считывание .из блока 7 памяти

5

0

введенной в них информации.

Выходы блока 7 памяти настройки являются управляющими входами мульти- плексов 1 группы, на информационные входы которых в этом случае поступают восемь переменных вычисляемой логической функции. Для коъюнктивной группы F1 мультиплексоров 1 группы открыты инверсные входы второго, третьего и восьмого мультиплексоров и прямые входы всех остальных мультиплексоров . Выходная информация мультиплексоров t группы подается на первые входы элементов ИЛИ 5 группы, на вторые входы которых подается восьмиразрядный код со значением логической 1 в IV-OM и VII-OM разрядах (IV и VII разряды не участвуют в вычислении F1) и значением логического О в разрядах I, II; III, V, VI, VIII. Если соответствующие разряды переменных, поступающих на мультиплексоры 1..группы имеют значения соответственно 1,0,0,1,0, то на выходе 5 элемента И 2 формируется сигнал логической 1, который по первому сиг- )налу строба записывается в первый триггер триггеров 3 группы (результат вычисления первой конъюнктивной груп5

0

пы) . Таким же образом записываются

результаты вычисления F2, F3 и F4 по второму, третьему и четвертому сигналам строба во втором, третьем и четвертом триггерах триггеров 3 группы.

Элемент И 4 служит дпя формирования сигнала блокировки триггеров 3

группы в том случае, если ни одна из переменных данной конъюнктивной группы не участвует в вычислении.

Формула изобретения

1, Программируемое устройство для вычисления логических функцийs содержащее два элемента И и группу триг геров, отличающееся тем, что, с целью повьппения быстродействия за счет обеспечения возможности вычисления за один такт каждой конъюнктивной группы функции, представлен- ной в дизъюнктивной нормальной форме (ДНФ), оно содержит блок управле1шя, генератор импульсов, блок памяти настройки, блок памяти функций, группу мультиплексоров, группу элементов

ИЛИ, причем информационные входы первой группы устройства соединены с прямыми и инверсными информационными входами мультиплексоров группы, выходы которых соединены, с первыми входами элементов ИЛИ группы, выходы которых соединены с входами первого элемента И, вькод которого соединен с информационными входами триггеров группы, инверсный выход генератора импульсов соединен с входом признака разрешения вьщачи тактовых импульсов блока управления, выходы первой группы которого соединены с тактовьпчи входами триггеров . группы, прямой вы ход генератора импульсов соединен с входом признака разрешения формирования адреса блока управления, выходы второй группы которого соединены с адресными входами блока памяти наст- ройки и блока памяти Функций, входы разрешения записи и разрешения работы которых соединены соответственно первым и вторым выходами блока управления, выходы блока памяти настрой- ки соединены с управляющими входами мультиплексоров группы, выходы блока памяти функций соединены с вторыми входами элементов ИЛИ группы и входами второго элемента И, выход которог соединен с входом блокировки триггер группы, информационные входы второй и третьей групп устройства соединены соответственно с информационными входами блока памяти настройки и блока памяти функ1ций, вход запуска генератора импульсов соединен с третьим выходом блока управления, четвертый выход которого является выходом

признака занятости устройства, вход пуска, вход начальной установки, вход разрешения записи, вход разрешения запуска генератора импульсов и вход сброса устройства соединены с одноименными входами блока управления, пятьп выход которого соединен с входами сброса триггеров группы, выходы которых являются выходами устройства .

шения запуска генератора импульсов блока, выход второго элемента И сое- инен с вторым входом четвертого элемента Hj выход которого является пер- ц вым выходом блока, вход сброса блока соединен с вторым входом первого элемента ИЛИ, с входом сброса второго счетчика и нулевым входом первого RS- триггера, вькод которого соединен с 10 третьим выходом блока и с вторым входом третьего элемента ИЛИ, выход которого является вторым выходом блока, (к+1)-й выход дешифратора соединен с третьим входом первого элемента ИЛИ. 15

iO

т

i4.1

От 9

К6и1

К5

К9

Зйлфг

0/п9

1}кз

.2

| Программируемый многофункциональныйлОгичЕСКий МОдуль | 1979 |

|

SU851399A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения значений булевых функций | 1984 |

|

SU1262475A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-29—Подача