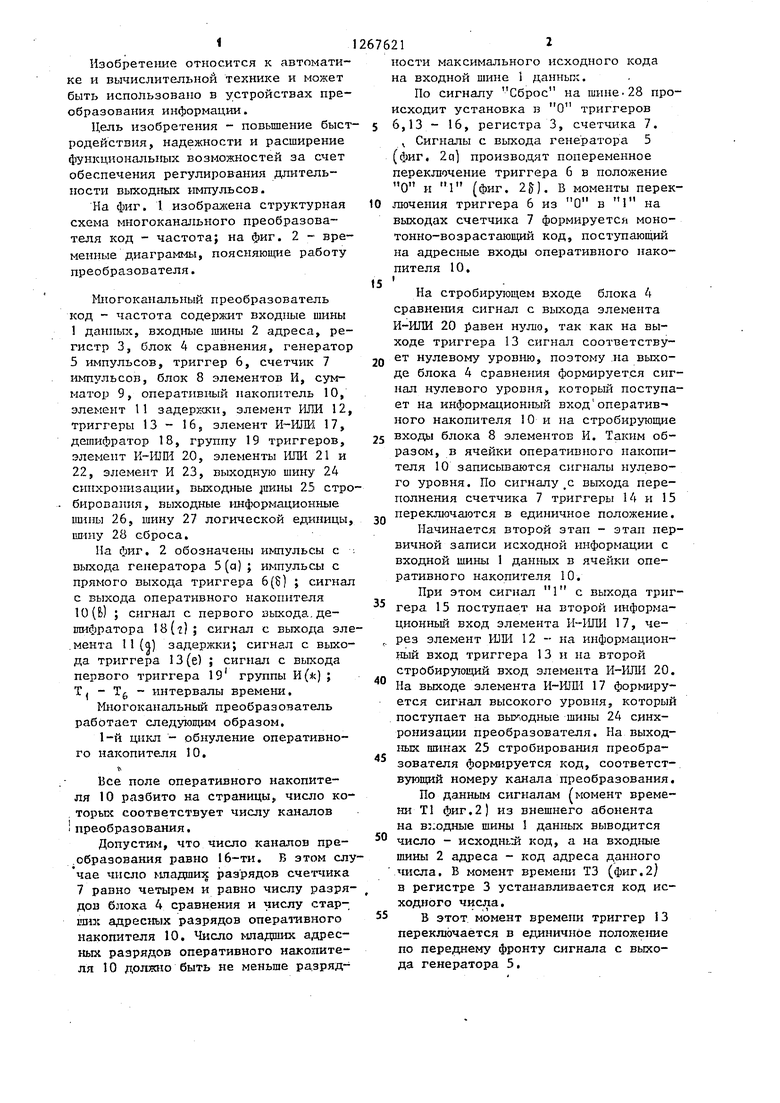

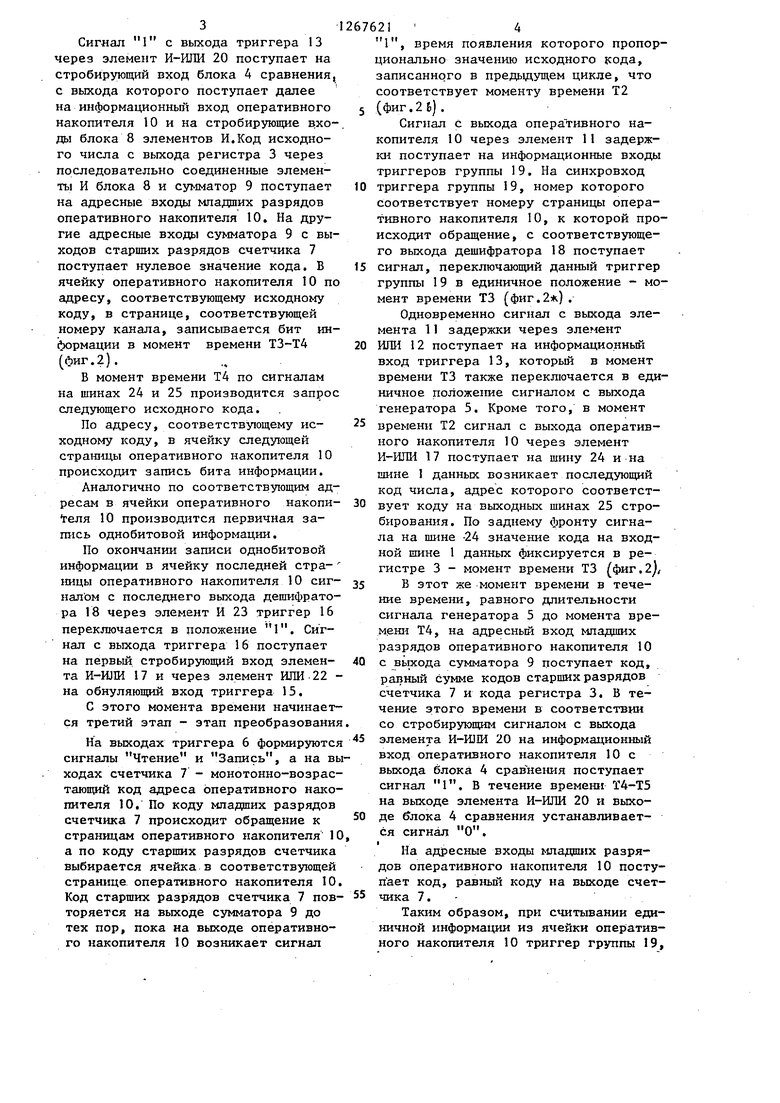

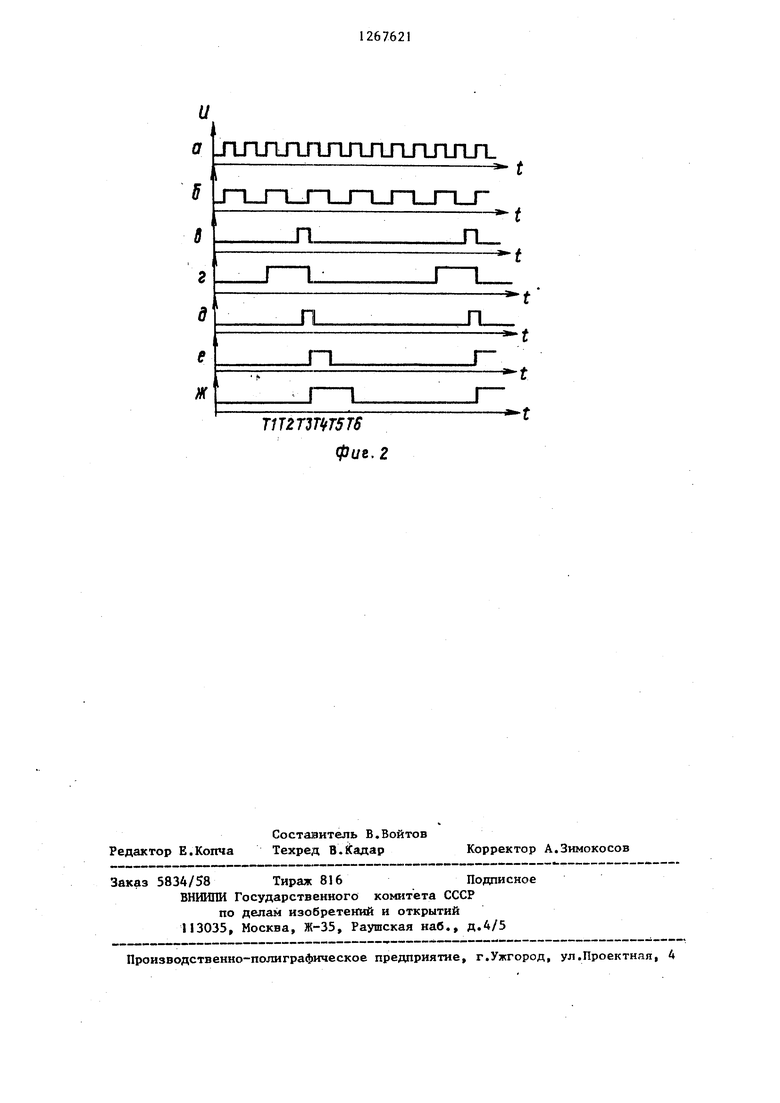

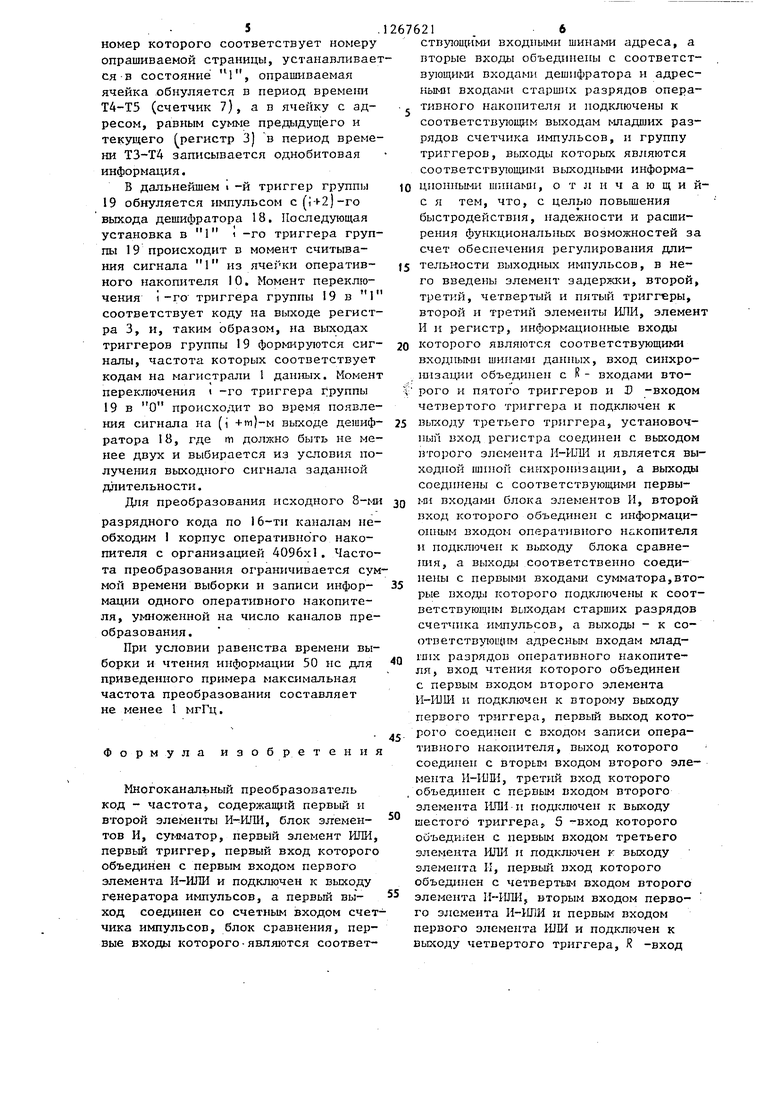

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах преобразования информации. Цель изобретения - повьшение быст родействия, надежности и расширение функциональных возможностей за счет обеспечения регулирования длительности выходных импульсов. На фиг. 1 изображена структурная схема многоканального преобразователя код - частота; на фиг. 2 - временные диаграммы, поясняющие работу преобразователя. Многоканальный преобразователь код - частота содержит входные шины 1 да1Н1ых, входные шины 2 адреса, регистр 3, блок 4 сравнения, генератор 5 импульсов, триггер 6, счетчик 7 импульсов, блок 8 элементов И, сумматор 9, оперативный накопитель 10, элемент И задержки, элемент ИЛИ 12 триггеры 13 - 16 5 элемент 17, дешифратор 18, группу 19 триггеров, элемент И-ШШ 20, элементы ИЛИ 21 и 22, элемент И 23, выходную шину 24 синхронизации, выходные ;иины 25 стро бировапия, выходные i-шформационные ишны 26, шину 27 логической единицы шииу 28 сброса. На фиг. 2 обозначены импульсы с выхода генератора 5(а) ; импульсл с прямого выхода триггера 6(5 ; сигнал с выхода оперативного накопителя 10(6) ; сигнал с первого аыходз., дешифратора ISlt); сигнал с выхода эл .мента И(а) задержки; сигнал с выхо да триггера 13 (е) ; сигнал с вьпсода первого триггера 19 группы И(;1с) ; Т( Tg - интервалы времени. Многоканальный преобразователь работает след тощим образом. 1-й цикл - обнуление оперативного накопителя 10, Все поле оперативного накопителя 10 разбито на страницы, число ко , торых соответствует числу каналов преобразования. Допустим, что число каналов пре.образования равно 16-ти. В этом сл чае число младших разрядов счетчика 7 равно четырем и равно числу разря дов блока 4 сравнения и числу стар-, ших адресных разрядов оперативного накопителя 10. Число младших адресных разрядов оперативного накопителя 10 должно быть не меньше ра.зряд212ности максимального исходного кода на входной шине 1 данньк. По сигналу Сброс на шине-28 происходит установка в О триггеров 6,13 - 16, регистра 3, счетчика 7. Сигналы с выхода генератора 5 (фиг. 2q производят попеременное переключение триггера 6 в положение О и 1 (фиг. 25). В моменты переключения триггера 6 нз О в 1 на выходах счетчика 7 формируется монотонно-возрастающий код, поступающий на адресные входы оперативного накопителя 10. На стробирующем входе блока 4 сравнеьшя сигнал с выхода элемента И-ИЛИ 20 15авен нулю, так как на выходе триггера 13 сигнал соответствует нулевому уровню, поэтому на выходе блока 4 сравнения формируется сигнал нулевого уровня, который поступает на информационный входоперативного накопителя 10 и на стробирующие входы блока 8 элементов И. Таким образом, в ячейки оперативного накопителя 10 записываются сигналы нулевого уровня. По сигналу с выхода переполнения счетчика 7 триггеры 14 и 15 переключаются в единичное положение. Начинается второй этап - этап нервичной записи исходной информации с входной шины 1 данных в ячейки оперативного накопителя 10. При этом сигнал 1 с выхода триггера 15 поступает на второй информационньй вход элемента И-ИЛИ 17, через элемент ИШ 12 - на информационный вход триггера 13 и на второй стробирующий вход элемента И-ИЛИ 20. На выходе элемента И-IfflIi 17 формируется сигнал высокого уровня, который поступает на вых,одные шины 24 синхронизации преобразователя. На выходных шинах 25 стробирования преобразователя формируется код, соответствующий номеру канала преобразования. По данным сигналам (момент времени Т1 фиг.2) из внешнего абонента на взюдные шины I данных выводится число - исходнь:й код, а на входные шины 2 адреса - код адреса данного числа. В момент времеш ТЗ (фиг.2) в регистре 3 устанавливается код исходного числа. в этот момент времени триггер 13 переключается в единичное положение по переднему фронту сигнала с выхода генератора 5.

Сигнал 1 с выхода триггера 13 через элемент И-ИЛИ 20 поступает на стробирующий вход блока 4 сравнения, с выхода которого поступает далее на информационный вход оперативного накопителя 10 и на стробирующие входы блока 8 элементов И.Код исходного числа с выхода регистра 3 через последовательно соединенные элементы И блока 8 и сумматор 9 поступает на адресные входы мпадших разрядов оперативного накопителя 10. На другие адресные входы сумматора 9 с выходов старших разрядов счетчика 7 поступает нулевое значение кода. В ячейку оперативного накопителя 10 по адресу, соответствующему исходному коду, в странице, соответствующей номеру канала, записывается бит информации в момент времени ТЗ-Т4 (Лиг.2).

В момент времени Т4 по сигналам на шинах 24 и 25 производится запрос следующего исходного кода.

По адресу, соответствующему исходному коду, в ячейку следующей страницы оперативного накопителя 10 происходит запись бита информации.

Аналогично по соответствующим адресам в ячейки оперативного накопигеля 10 производится первичная запись однобитовой информации.

По окончании записи однобитовой информации в ячейку последней страницы оперативного накопителя 10 сигналом с последнего выхода дешифратора 18 через элемент И 23 триггер 16 переключается в положение 1. Сигнал с выхода триггера 16 поступает на первый стробирующий вход элемента И-ИЛИ 17 и через элемент ИЛИ 22 на обнуляющий вход триггера 15.

С этого момента времени начинается третий этап - этап преобразования

На выходах триггера 6 формируются сигналы Чтение и Запись, а на выходах счетчика 7 - монотонно-возрастающий код адреса оперативного накопителя 10, По коду младших разрядов счетчика 7 происходит обращение к страницам оперативного накопителя 10 а по коду старших разрядов счетчика выбирается ячейка в соответствующей странице оперативного накопителя 10 Код старших разрядов счетчика 7 повторяется на выходе сумматора 9 до тех пор, пока на выходе оперативного накопителя 10 возникает сигнал

1, время появления которого пропорционально значению исходного кода, записанного в предыдущем цикле, что соответствует моменту времени Т2 (фиг .26).

Сигнал с выхода оперативного накопителя 10 через элемент 11 задержки поступает на информационные входы триггеров группы 19. На синхровход триггера группы 19, номер которого соответствует номеру страницы оперативного накопителя 10, к которой происходит обращение, с соответствующего выхода дешифратора 18 поступает сигнал, переключающий данный триггер группы 19 в единичное положение - момент времени ТЗ (фиг.2).

Одновременно сигнал с выхода элемента 11 задержки через элемент ИЛИ 12 поступает на информационный вход триггера 13, который в момент времени ТЗ также переключается в единичное положехше сигналом с выхода генератора 5. Кроме того, в момент времени Т2 сигнал с выхода оперативного накопителя 10 через элемент И-ИЛИ 17 поступает на шину 24 и на шине 1 данных возникает последующий код числа, адрес которого соответствует коду на выходных шинах 25 стробировання. По заднему фронту сигнала на шине -24 значение кода на входной шине 1 данных фиксируется в регистре 3 - момент времени ТЗ (фиг.2),

Б этот же момент времени в течение времени, равного длительности сигнала генератора 5 до момента времеш Т4, на адресный вход fflaдшиx разрядов оперативного накопителя 10 с вьрсода сумматора 9 поступает код, равный сумме кодов старших разрядов счетчика 7 и кода регистра 3. Б течение этого времени в соответствии со стробирующим сигналом с выхода элемента И-ШШ 20 на информационный вход оперативного накопителя 10 с выхода блока 4 срав не1шя поступает сигнал 1. Б течение времени Т4-Т5 на выходе элемента И-ИЛИ 20 и выходе блока 4 сравнения устанавливается сигнал О.

На адресные входы maдшиx разрядов оперативного накопителя 10 поступает код, равньй коду на выходе счетчика 7. Таким образом, при считывании единичной информации из ячейки оперативного накопителя 10 триггер группы 19, номер которого соответствует номеру опрашиваемой страницы, устанавливае ся -в состояние 1, опрашиваемая ячейка обнуляется в период времени Т4-Т5 (счетчик 7), а в ячейку с адресом, равным сумме пpeдыдyD eгo и текущего (регистр 3) в период време ни ТЗ-Т4 записывается однобитовая информация. В дальнейшем i -и триггер группы 19 обнуляется импульсом с(гь2)-го выкода дешифратора 18. Последующая установка в 1 i -го триггера группы 19 происходит в момент считывания сигнала 1 из ячейки оперативного накопителя 10. Момент переключения -го триггера группы 19 в I соответствует коду на выходе регистра 3, и, таким образом, на выходах триггеров группы 19 формируются сигналы, частота которых соответствует кодам на магистрали 1 данных. Момент переключения -го триггера Группы 19 в О происходит во время появления сигнала на (i +т)-м выходе дешифратора 18, где m должно быть не менее двух и выбирается из условия получения выходного сигнала заданной длительности. Для преобразования исходного 8-ми разрядного кода по 16-ти каналам необходим 1 корпус оперативного накопителя с организацией 4096x1. Частота преобразования ограничивается сум мой времени выборки и записи информадии одного оперативного накопителя, умноженной на число каналов преобразования. При условии равенства времени выборки и чтения инфор1-1ацш1 50 не для приведенного примера максимальная частота преобразования составляет не менее 1 мгГц. Формула изобретения Многоканальный преобразователь код - частота, содержащий первый и второй элементы , блок элементов И, сумматор, первый элемент ИЛИ, первый триггер, первый вход которого объединен с первым входом первого элемента И-ШТИ и подключен к выходу генератора импульсов, а первый выход соединен со счетным входом счет чика импульсов, блок сравнения, первые входы которогоявляются соответствующими входными шинами адреса, а вторые входы объединены с соответствующими входами дешифратора и адресными входами старших разрядов оперативного накопителя и подключены к соответству7ощим выходам младших разрядов счетчика импульсов, и группу триггеров, выходы которых являются соответствующиья выходными информационными шинаьп, отличающийс я тем, что, с целью повьшения быстродействия, надежности и расширения функциональных возможностей за счет обеспечения регулирования длительности выходных импульсов, в него введены элемент задерш-си, второй, третий, четвертый и пятый триггеры, второй и третий элементы ИЛИ, элемент И и регистр, информационные входы которого являются соответствующими ВХОДПЫМ1 шинам данных, вход синхроШ1за1 1д-1и объединен с R - входами второго и пятого триггеров и D -входом четвертого триггера и подключен к выходу третьего триггера, установочный вход регистра соединен с вькодом второго элемента И-ИЛ11 и является выходной шиной синхронизации, а выходы соединены с соответствующими первыг-ui входам блока элементов И, второй вход которого объединен с информационным входом оперативного накопителя У1 подключен к выходу блока сравне шя, а выходы соответственно соединены с первыми входами сумматора,вторые ВХОД111 которого подключены к соответствующим выходам старших разрядов счетчика импульсов, а выходы - к соответствующим адресным входам млад- разрядов оперативного накопителя, вход чтения которого объединен с первым входом второго элемента И-ШШ и подключен к второму выходу первого триггера, первый выход которого Соединен с входо1-1 записи оперативного накопителя, выход которого соединен с BTOpbiM входом второго элемента И-ШП1, третнй вход которого oбъeд пIeн с первым входом второго элемента ИЛИ и подгслючен к выходу шестого триггера5 5 -вход которого объединен с первым входом третьего элемента ШШ и подключен к выходу элемента К, нервьш вход которого объединен с четвертым входом второго элемента И-ШШу вторым входом первоо элемента И-ИЛИ и первым входом ервого элемента ШШ и подключен к ыходу четвертого триггера, R -вход

которого соединен с выходом второго элемента ШШ, а С-вход объединен с С-входом третьего триггера и подоотзо чен к выходу переполнения счетчика импульсов, вход сброса которого сое динен с выходом третьего элемента ШШ, второй вход которого объединен с вторыми входами первого триггера и второго элемента IDBi и R -входом третьего триггера и является шиной сброса, при этом третий вход блока сравнения соединен с выходом первого элемента И-1-ШИ, третий и четвертьй входы которого объединены и подключены к выходу второго триггера.

267621 .

С-вход которого соединен с выходом генератора импульсов, а D -вход - с выходом первого элемента ИЛИ, второй вход которого объединен cD-Bxo г группы триггеров и через элемент задержки подключен к выходу оперативного накопителя, причем 3) -вход третьего триггера является шиной логической едишщы, вторые входы блока to сравнения являются соответствующими выходныьш шинаш стробирования, а С-Бход и R-вход группы триггеров соответственно подключены к первым выходам дешифратора, второй выход которо15 го соёдинен с вторым входом элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля трассировки и воспроизведения информации о прокладке кабельной трассы | 1984 |

|

SU1238106A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1336239A1 |

| Генератор последовательности импульсов | 1983 |

|

SU1231583A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для контроля хода программ ЭВМ | 1987 |

|

SU1430960A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛОВ | 1993 |

|

RU2037270C1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Ассоциативное оперативное запоминающее устройство | 1981 |

|

SU978197A1 |

Изобретение относится к области автоматики и вычислительной тех1ШКИ и может быть использовано в устройствах преобразования информации. Целью изобретешь является повышеiffle быстродействия, надежности и расширение функциональных возможностей за счет обеспечения регулирования длительности выходных импульсов. Преобразователь работает в насколько циклов. В нервом щоше происходит обнуление оперативного накопителя путем формирования в счетчике импульсов монотонно-возрастающего кода с помощью генератора и myльcoв и триггера. На выходе блока сравнения формируется нулевой сигнал, который записывается в ячейки оперативного накопителя. На втором цикле происходит первичная запись исходной однобитовой информации с входной шины данных в ячейки оперативного накопителя по соответствующим адресам. На третьем этапе происходит непосредственно преобразование путем обращения к страницам и ячейкам оперативного накопителя по кодам счетчика. При считывао iS нии единичной информации из ячейки оперативного накопителя триггер групФ пы триггеров, номер которого опредеС ляется дешифратором, устанавливается в состояние 1, опрашиваемая ячейка обнуляется сигналом со счетчика, а в ячейку с адресом, определяемым сумматором и равным сумме предыдущего и текущего содержимого регистра, записывается однобитовая инN5 формации. 2 ил. 05 чЗ о ю

6 евро С

28 фие.1

JTJIJTJIJIJTJTJIJIJIJIJTJI.

л.

д

п

ттгтт5Тб

фи&. 2

Jl

Л

--t

| Гитис Э.И | |||

| Преобразователь информации для электрошгых цифровых вычислительных устройств | |||

| М,: Энергия, .1970, с.234-239, рис | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР № 1069559, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1985-03-11—Подача