Изобретение относится к вычислительной технике и может быть использовано для проверки отказоустойчивости функционирования комплекса программ ,

Цель изобретения - повышение быстродействия устройства.

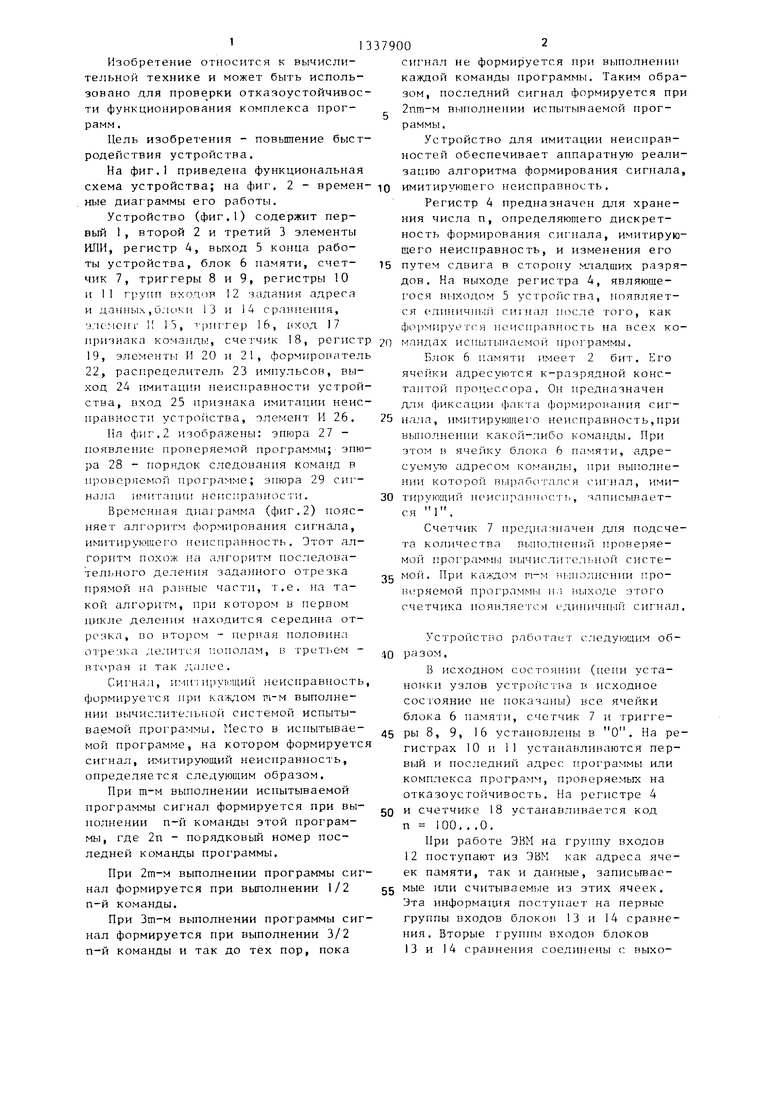

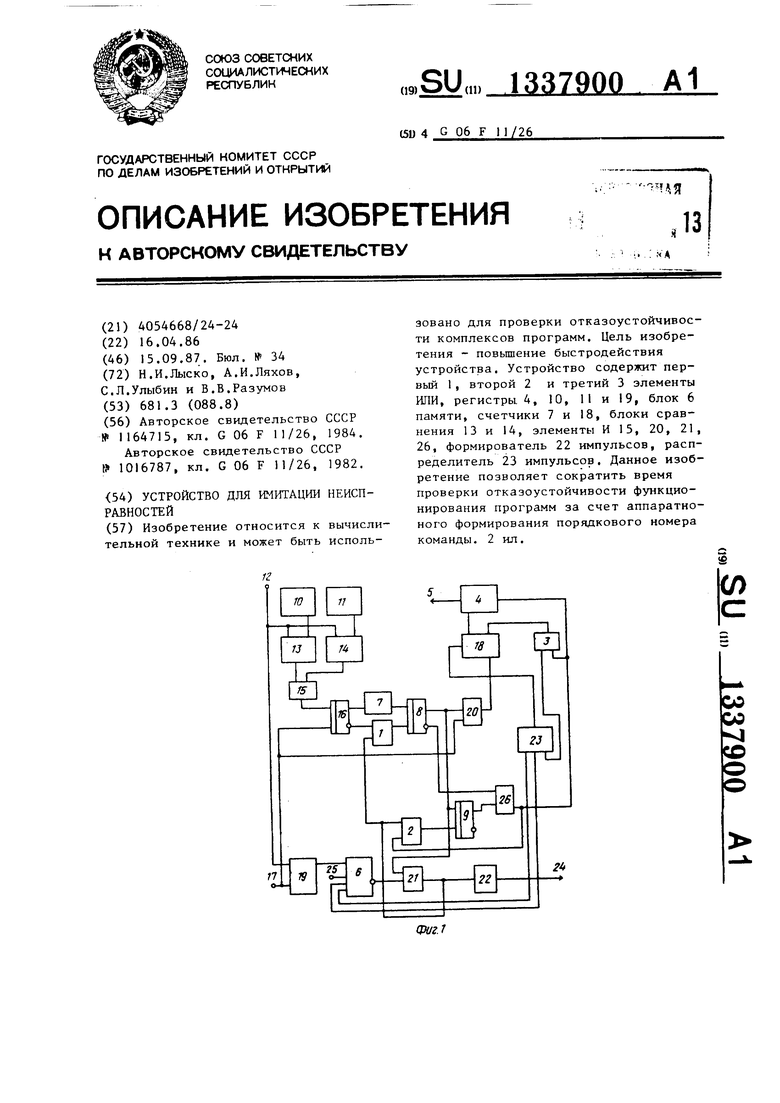

На фиг, приведена функциональная

схема устройства; на фиг, 2 - времен- имитирующего неисправность,

ные диаг раммы его работы.

Устройство (фиг,1) содержит первый 1, второй 2 и третий 3 элементы ИЛИ, регистр 4, выход 5 конца работы устройства, блок 6 памяти, счетчик 7, триггеры 8 и 9, регистры 10 и 11 rjiyiin входов 12 -задания адреса и данных,олукм 13 и 14 с ранпения, злсмси 1 И 15, тригг ер 16, нход 17

причнака команды, счетчик 18, регистр 20 мандах испытынаемо11 программы, 19, элементы И 20 и 21, формирователь 22, распределителтз 23 импульсов, выБлок 6 памяти имеет 2 бит ячеГжи адресуются к-разрядной к тантой процессора. Он предназна для фиксации факта формирования

ход 24 имитации 1еисправности устройства, вход 25 признака имитации неис- правностп устройства, элемент И 26,

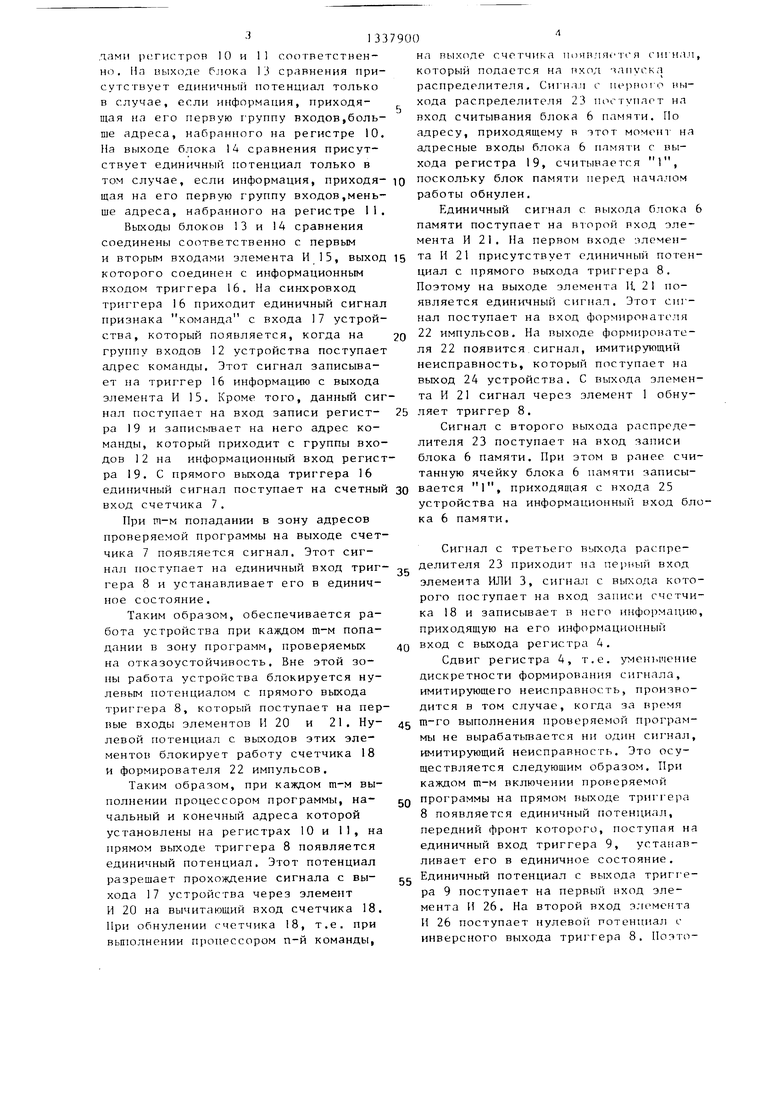

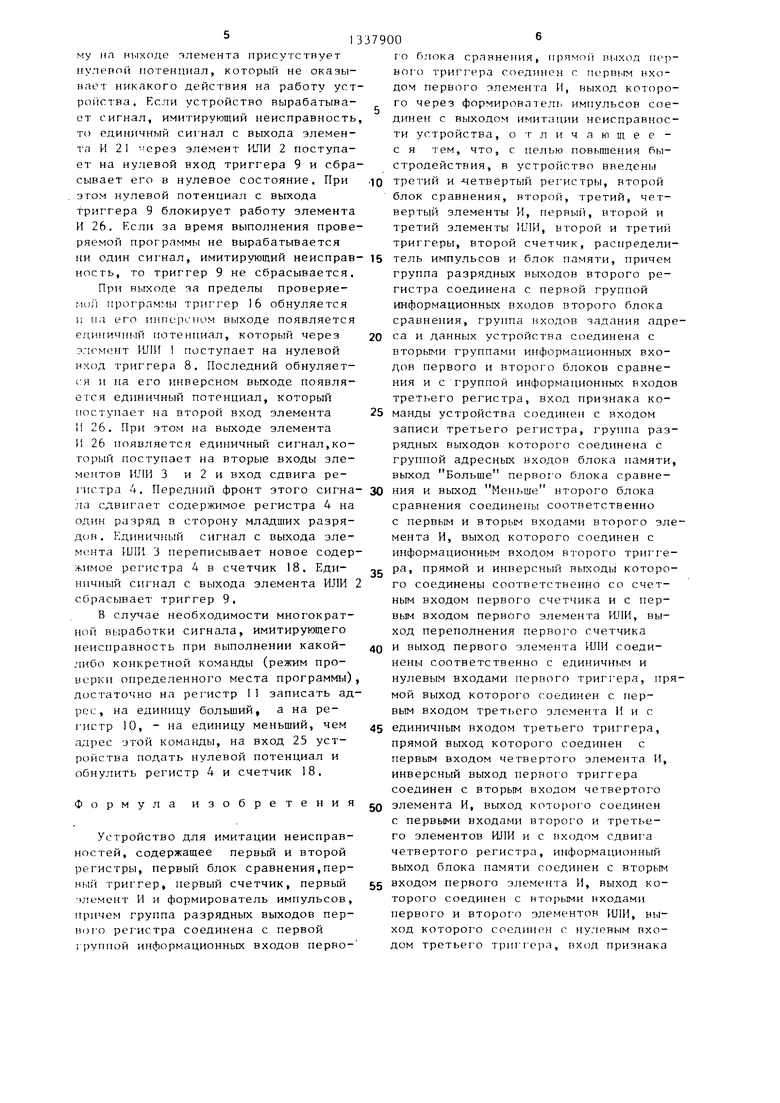

Па фиг,2 изображены: эпюра 27 - появление проверяемой программы; эпюра 28 - порядок следования команд в нровсряемой программе; эпюра 29 сигнала имитации HCticiipaijHOC i H.

Временная диа рамма (фиг,2) поясняет алгоритм формирования сиг нала, имитирующего неиспраршость, Этот алгоритм похож алгоритм пос.чедовг - тельного деления заданного отрезка прямой на равные части, т,е, на такой алгоритм, при котором и первом цикле деления находится середина отрезка, во втором - первая половина отрезка делится пополам, в третьем - вторая и так далее.

Сигнал, имп гпруи)щий }1еисг1равность, формируется при ni-м выполнении вычисли1 е:1ьно11 системой испытываемой программы. Место в испытываемой программе, на котором формируется сигнал, имитирующий неисправность, определяется следующим образом,

Нри т-м выполнении испытываемой программы сигнал формируется при выполнении п-й команды этой программы, где 2п - порядковый номер последней команды программы.

При 2т-м выполнении программы сигнал формируется при выполнении 1/2 п-й команды.

При Зт-м выполнении программы сигнал формируется при выполнении 3/2 п-й команды и так до тех пор, пока

сигнал не формируется при выполнении каждой команды программы. Таким образом, последний сигнал формируется при 2nm-M выполнении испытываемой программы.

Устройство для имитации неисправностей обеспечивает аппаратную реализацию алгоритма формирования сигнала,

Регистр 4 предназначен для хранения числа п, определяющего дискретность формирования сигнала, имитирующего неисправность, и изменения его путем сдвига в сторону младших разрядов. На выходе регистра 4, являющегося выходом 5 устройства, появляется елпиичиыГ сигнал поели тог о, как формирую тс-я неисправность на всех командах испытынаемо11 программы,

Блок 6 памяти имеет 2 бит. Его ячеГжи адресуются к-разрядной константой процессора. Он предназначен для фиксации факта формирования сигнала, имитирующего неисправность,при выцолне1П1и какой-либо команды. При этом в ячейку блока 6 памяти, адресуемою адресом команды, при выполнении которой В1,1рапотался с1П нал, имитирующий неиспр;1нпос 1 1, записывает- ся 1,

Счетчик 7 предназначеп для подсчета количества выполнений проверяемой программы вычислительной системой. При каждом п-м иь полнеьи1и про- перяемой программь. ил выходе этого счетчика появляется единичный сигнал,

YcTpoiicTBO работает следующим об- разом.

В исходном состоянии (пени установки узлов устр(.1Йства в исходное сое 1 ояние не моказашл) все ячейки блока 6 памяти, счетчик 7 и тригге- ры 8, 9, 16 установлены в О, На регистрах 10 и 11 устанавливаются первый и последний адрес программы или комцлекса nporpaM -i, проверяемых на отказоустойчивость. На регистре 4 и счетчике 18 устанавливается код п 100...0,

При работе ЭВМ на группу входов

12поступают из ЭВМ как адреса ячеек памяти, так и данные, записьгеаемые или считываемые из этих ячеек. Эта информащ1я поступает на первые группы входов блоков 13 и 14 сравнения. Вторые 1 руппы входов блоков

13и 14 сравнения соединены с выхо 1337900

дами ригистрон 10 и 11 соответстнен- но, На иыходе блока 13 сравнения присутствует единичный потенциал только в случае, если информация, приходящая яа его первую г руппу входов,больше адреса, набранного на регистре 10. На выходе блока 14 сравнения присутствует единичный потенциал только в

том случае, если информация, приходя- ю поскольку блок памяти перед началом

щая на его первую группу входов,мень- работы обнулен,

ше адреса, набранного на регистре 1 1 , Единичный сиг нал с выхода блока 6

Выходы блоков 13 и 14 сравнения памяти поступает на второй вход эле- соединены соответственно с первым мента И 21, На первом входе :элемен- и вторым входами элемента И 15, выход 15 та И 21 присутствует единичный потен- которого соединен с информационным входом триггера 16, На синхровход триггера 16 приходит единичный сигнал признака команда с входа 17 устройства, который появляется, когда на 20 группу входов 12 устройства поступает адрес команды. Этот сигнал записывает на триггер 16 информацию с выхода элемента И 15, Кроме того, данный сигнал поступает на вход записи регист- 25 ляет триггер 8,

ра 19 и записывает на него адрес ко- Сигнал с второго выхода распрсде- манды, который приходит с группы входов 12 на информационный вход регистра 19, С прямого выхода триггера 16

циал с прямого выхода триггера 8, Поэтому на выходе элемента 11 21 появляется единичный сигнал. Этот сигнал поступает на вход формирователя 22 импульсов. На выходе формиронате- ля 22 появится сигнал, имитирующий неисправность, который поступает на выход 24 устройства, С выхода элемента И 21 сигнал через элемент 1 обнулителя 23 поступает на вход записи блока 6 памяти. При этом в ранее считанную ячейку блока 6 памяти записыединичный сигнал поступает на счетный ЗО вается 1 , приходящая с входа 25 вход счетчика 7,устройства на информационный вход блоПри т-м попадании в зону адресов ка 6 памяти, проверяемой программы на выходе счетчика 7 появляется сигнал. Этот сигСигнал с третьего выхода распренал поступает на единичный вход триг- 5 Делителя 23 приходит па первый вход

гера 8 и устанавливает его в единичное состояние.

Таким образом, обеспечивается работа устройства при каждом т-м попадании в зону программ, проверяемых на отказоустойчивость. Вне этой зоны работа устройства блокируется нулевым потенциалом с прямого выхода триггера 8, который поступает на первые входы элементов И 20 и 21, Нулевой потенциал с выходов этих элементов блокирует работу счетчика 18 и формирователя 22 импульсов.

Таким образом, при каждом т-м выполнении процессором программы, начальный и конечный адреса которой установлены на регистрах 10 и И, на прямом выходе триггера 8 появляется единичный потенциал. Этот потенциал разрешает прохождение сигнала с выхода 17 устройства через элемент И 20 на вычитающий вход счетчика 18, Нри обнулении счетчика 18, т,е, при выполнении процессором п-й команды,

элемента ИЛИ 3, сигнал с выхода кото рого поступает на вход записи счетчи ка 18 и записывает в него информацию приходящую на его информационный

40 вход с выхода регистра 4,

Сдвиг регистра 4, т,е, уменьшение дискретности формирования сигнала, имитирующего неисправность, производится в том случае, когда за время

45 т-го выполнения проверяемой программы не вырабатывается ни один сиг-нал, имитирующий неисправность. Это осуществляется следующим образом. При каждом т-м включении проверяемой

gQ программы на прямом выходе триггера 8 появляется единичный потенциал, передний фронт которого, поступая на единичный вход триггера 9, устанавливает его в единичное состояние. Единичный потенциал с выхода тригг-е- ра 9 поступает на первый вход элемента И 26, На второй вход элемента И 26 поступает нулевой потенциал с инверсного выхода триггера 8, Ноэто55

на выходе счетчика поипл иет1 я сигнал, который подается на иход чапуска распределителя. Сигнал с перпого ны- хода распределителя 23 ш ступает на вход считывания блока 6 памяти. По адресу, приходящему в этот момент на адресные входы блока 6 памяти с выхода регистра 19, считывается 1,

памяти поступает на второй вход эле- мента И 21, На первом входе :элемен- та И 21 присутствует единичный потен- ляет триггер 8,

циал с прямого выхода триггера 8, Поэтому на выходе элемента 11 21 появляется единичный сигнал. Этот сигнал поступает на вход формирователя 22 импульсов. На выходе формиронате- ля 22 появится сигнал, имитирующий неисправность, который поступает на выход 24 устройства, С выхода элемента И 21 сигнал через элемент 1 обну Сигнал с второго выхода распрсде-

лителя 23 поступает на вход записи блока 6 памяти. При этом в ранее считанную ячейку блока 6 памяти записы6 памяти,

Сигнал с третьего выхода распреДелителя 23 приходит па первый вход

элемента ИЛИ 3, сигнал с выхода которого поступает на вход записи счетчика 18 и записывает в него информацию, приходящую на его информационный

вход с выхода регистра 4,

Сдвиг регистра 4, т,е, уменьшение дискретности формирования сигнала, имитирующего неисправность, производится в том случае, когда за время

т-го выполнения проверяемой программы не вырабатывается ни один сиг-нал, имитирующий неисправность. Это осуществляется следующим образом. При каждом т-м включении проверяемой

программы на прямом выходе триггера 8 появляется единичный потенциал, передний фронт которого, поступая на единичный вход триггера 9, устанавливает его в единичное состояние. Единичный потенциал с выхода тригг-е- ра 9 поступает на первый вход элемента И 26, На второй вход элемента И 26 поступает нулевой потенциал с инверсного выхода триггера 8, Ноэто

му ил ныходе элемента присутствует iiynenoii потенциал, который не оказывает никакого действия на работу уст роГютва, Если устройство вырабатывает сигнал, имитирующий неисправность то единичный сигнал с выхода элемента И 21 - Срез элемент ИЛИ 2 поступает на нулевой вход триггера 9 и сбрасывает его в нулевое состояние. При этом нулевой потенциал с выхода триггера 9 блокирует работу элемента И 26. Если за время выполнения проверяемой программы не вырабатывается ни один сигнал, имитирующий неисправ ность, то триггер 9 не сбрасывается. При выходе за пределы проверяе- Mufi программы триггер 16 обнуляется и па его ипперсиом выходе появляется единичный потенпиал, который через э. Ш1И 1 поступает на нулевой нход триггера 8. Последний обнуляется и на его инверсном выходе появля- ег ся единичный потенциал, который поступает на второй вход элемента И 26. При этом на выходе элемента И 26 появляется единичный сигнал,который поступает на вторые входы элементов ИЛИ 3 и 2 и вход сдвига ре35

гистра 4. Передний фронт этого сигна- 30 ния и выход Меньше второго блока ла сдвигает содержимое регистра 4 на один разряд в сторону младших разря- Д(Л(. Единичный сигнал с выхода эле- ИЛИ 3 переписывает новое содержимое регистра 4 в счетчик 18. Единичный сигнал с выхода элемента ИЛР1 2 сбрасывает триггер 9.

В случае необходимости многократной выработки сигнала, имитирующего неисправность при выполнении какой- либо конкретной команды (режим проверки определенного места программы), достаточно на регистр 11 записать адрес, на единицу больший, а на регистр 10, - на единицу меньший, чем а,црес этой , на вход 25 устройства подать нулевой потенциал и

40

45

сравнения соединены соответственно с первым и вторым входами второго э мента И, выход которого соединен с информационным входом второго тригг ра, прямой и инверсный выходь котор го соединены соответственно со счет ньпч входом первого счетчика и с пер вым входом первого элемента ИЛИ, вы ход переполнения первого счетчика и выход первого элемента ИЛИ соединены соответственно с единичным и нулевым входами первого триггера, п мой выход которого соединен с первым входом трет1 его элемента И и с единичным входом третьего триггера, прямой выход которого соединен с первым входом четвертого элемента И инверсный выход первого триггера соединен с вторым входом четвертого элемента И, выход которого соединен с первыми входами второго и третьего элементов ИЛИ и с входом сдвиг а четвертого регистра, информационный выход блока памяти соединен с вторы входом первого элемента И, выход ко торого соединен с вторыми входами первого и второг о элементов ИЛИ, вы ход которого соединен с нулевым вхо дом третьего тр1П гера, вход признак

обнулить регистр 4 и счетчик 18. Формула изобретения

Устройство для имитации неисправностей, содержащее первый и второй регистры, первый блок сравнения,пер- Hbiii триггер, первый счетчик, первый лемент И и формирователь импульсов, причем группа разрядных выходов первого регистра соединена с первой группой информационных входов перво37900

Г О

.IQ 1520 25

блока сравнения, прямоГ BI.IXOA пер- вог(5 триггера соединен с ,гм входом первого элемента И, выход которого через формирова ель импульсов соединен с выходом имитации неисправности устройства, отличающее- с я тем, что, с целью повышения быстродействия, в устройство введены третий и четвертый регистры, второй блок сравнения, второй, третий, чет- верть1Й элементы И, первый, второй и третий элементы ИЛИ, второй и третий триггеры, второй счетчик, распределитель импульсов и блок памяти, причем группа разрядных выходов второго регистра соединена с первой группой информационных входов второго блока сравнения, группа входов задания адреса и данных устройства соединена с вторыми группами информационных входов первого и второго блоков сравнения и с группой информационньк входов третьего регистра, вход признака команды устройства соединен с входом записи третьего регистра, группа разрядных выходов которого соединена с группой адресных входов блока памяти, выход Больше первого блока сравне5

0 ния и выход Меньше второго блока

0

5

0

5

сравнения соединены соответственно с первым и вторым входами второго элемента И, выход которого соединен с информационным входом второго триггера, прямой и инверсный выходь которого соединены соответственно со счет- ньпч входом первого счетчика и с первым входом первого элемента ИЛИ, выход переполнения первого счетчика и выход первого элемента ИЛИ соединены соответственно с единичным и нулевым входами первого триггера, прямой выход которого соединен с первым входом трет1 его элемента И и с единичным входом третьего триггера, прямой выход которого соединен с первым входом четвертого элемента И, инверсный выход первого триггера соединен с вторым входом четвертого элемента И, выход которого соединен с первыми входами второго и третьего элементов ИЛИ и с входом сдвиг а четвертого регистра, информационный выход блока памяти соединен с вторым входом первого элемента И, выход которого соединен с вторыми входами первого и второг о элементов ИЛИ, выход которого соединен с нулевым входом третьего тр1П гера, вход признака

команды устройства соединен с синхро- входом второго триггера и вторым входом третьего элемента И, выход которого соединен с вычитагацим входом второго счетчика, выход третьего элемента ИЛИ и группа информационных выходов четвертого регистра соединены соответственно с входом записи и группой информационных входов второго счетчика, выход переполнения которого соединен с входом запуска

2В

2п

1Г7 2ГГ

Редактор И.Касарда

Составитель И.Сигалов Техред М.Ходанич

Заказ 4133/48Тираж 672

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

распределителя импульсов, первьй, второй и третий выходы которого соединены соответственно с вторым входом третьего элемента ИЛИ, с входами записи и считывания блоки памяти, выход переполнения четвертого регистра и информационный вход блока памяти являются соответственно выходом конца работы устройства и входом признака имитации неисправности устройства.

п

п

t

/ jf //г

(pus .2

Корректор М.Пожо

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования признака команды | 1986 |

|

SU1387000A1 |

| Устройство для поиска перемежающихся неисправностей | 1985 |

|

SU1262502A1 |

| Устройство для контроля программ | 1984 |

|

SU1265776A1 |

| Устройство для имитации неисправностей | 1989 |

|

SU1619279A1 |

| Устройство для контроля памяти | 1984 |

|

SU1236558A1 |

| Устройство для поиска перемежающихся неисправностей | 1986 |

|

SU1381511A1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Устройство для сбора статистических данных о работе программ ЭВМ | 1987 |

|

SU1471202A1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Устройство для контроля программ | 1985 |

|

SU1251128A1 |

Изобретение относится к вычислительной технике и может быть испольfZ зовано для проверки отказоустойчивости комплексов программ. Цель изобретения - повьшение быстродействия устройства. Устройство содержит первый 1, второй 2 и третий 3 элементы ИЛИ, регистры 4, 10, 11 и 19, блок 6 памяти, счетчики 7 и 18, блоки сравнения 13 и 14, элементы И 15, 20, 21, 26, формирователь 22 импульсов, распределитель 23 импульсов. Данное изобретение позволяет сократить время проверки отказоустойчивости функционирования программ за счет аппаратно- ного формирования порядкового номера команды. 2 ил. (Л со со со

| Устройство для имитации неисправностей | 1984 |

|

SU1164715A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для имитации неисправностей цифровой вычислительной машины | 1982 |

|

SU1016787A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-09-15—Публикация

1986-04-16—Подача