Изобретение относится к вычислительной технике и может быть использовано для контроля полупроводниковых оперативных и постоянных запоминающих устройств.

Цель изобретения - расширение функциональных возможностей за счет контроля блоков оперативной и постоянной памяти и повышение надежности устройства.

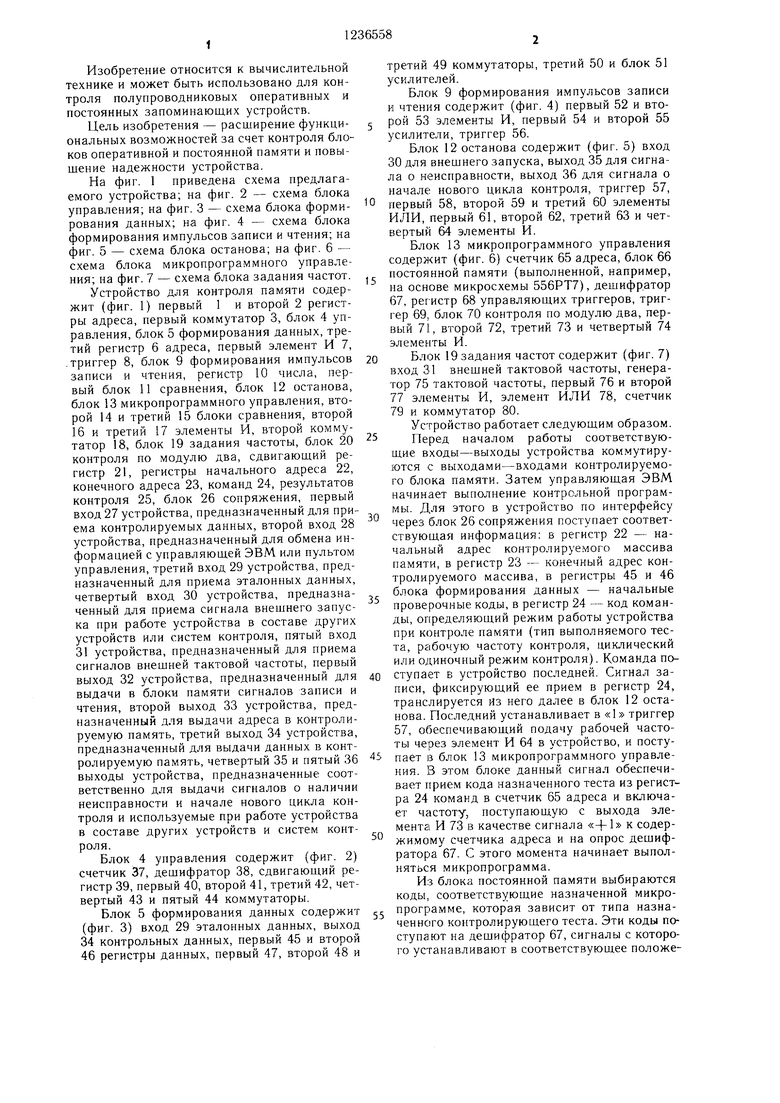

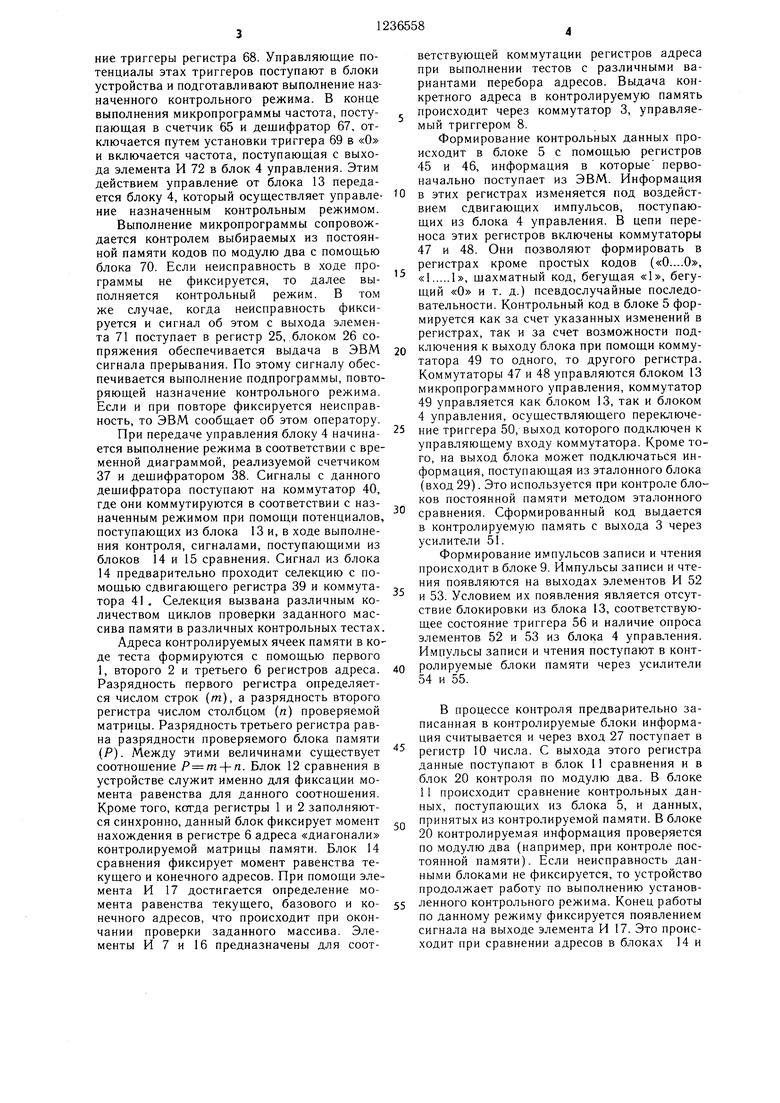

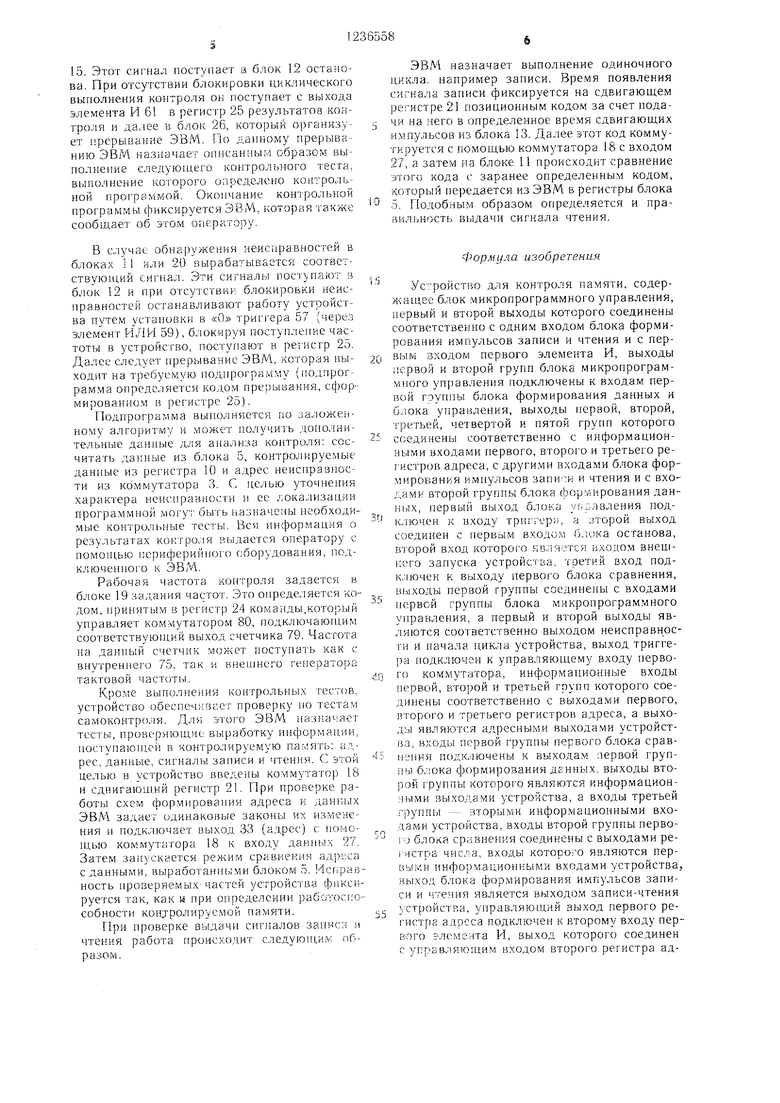

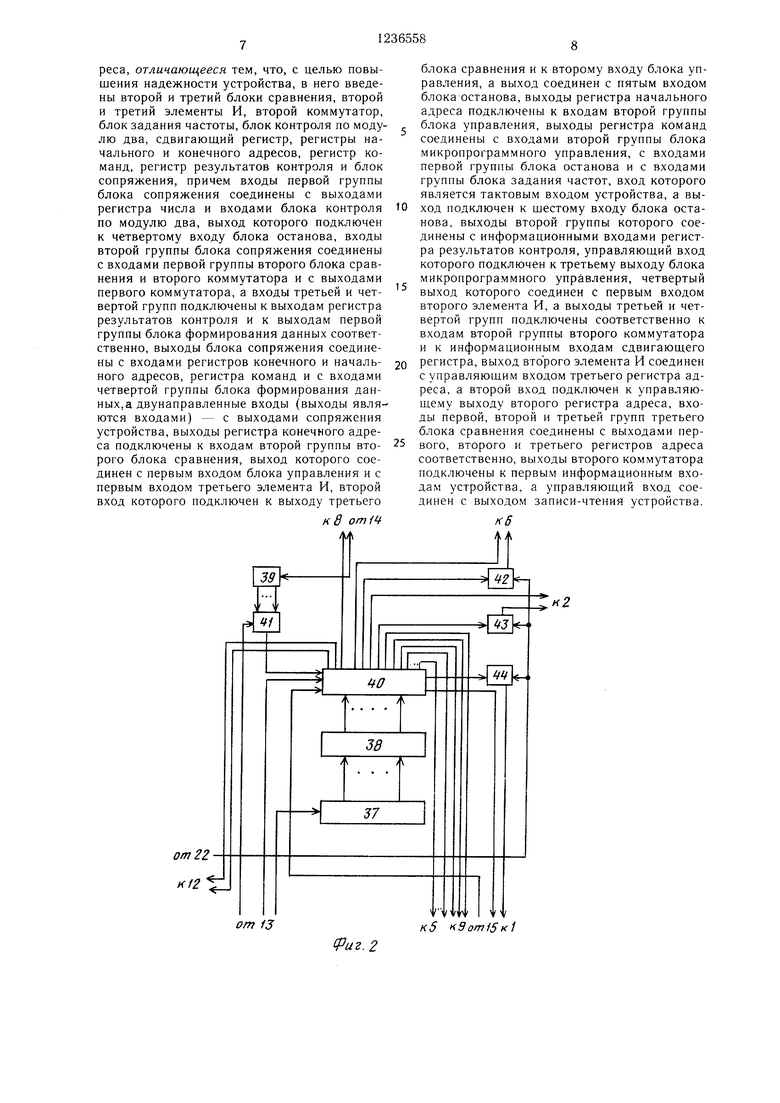

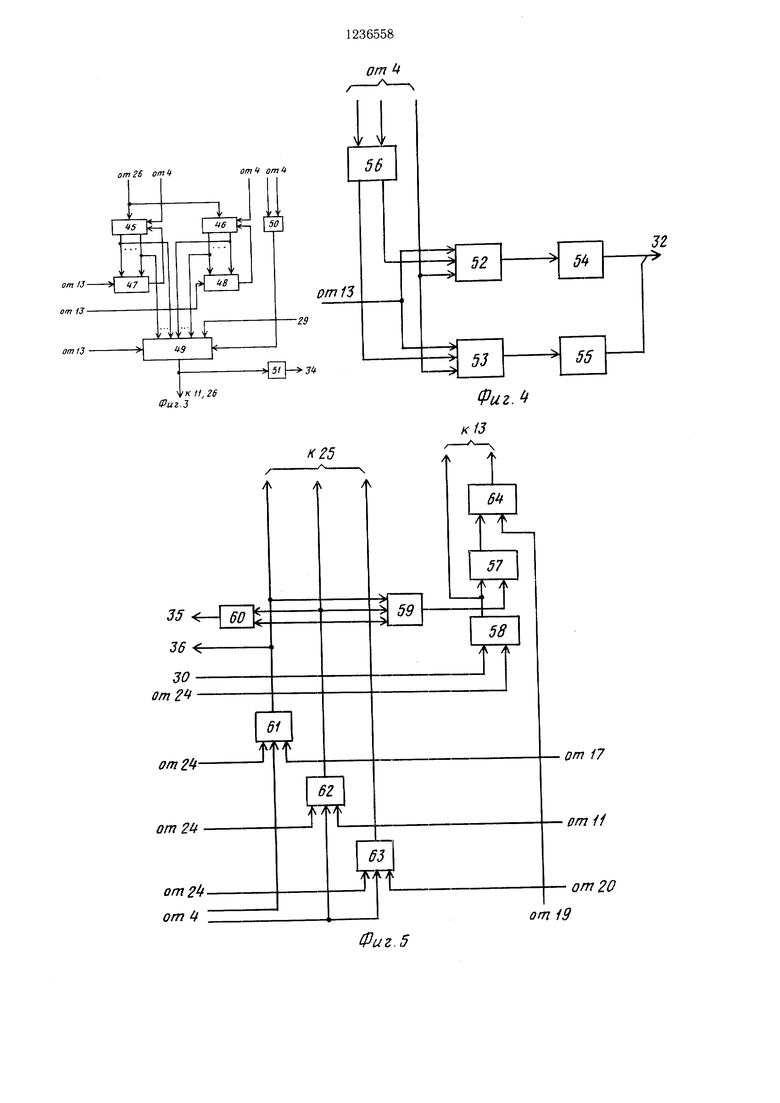

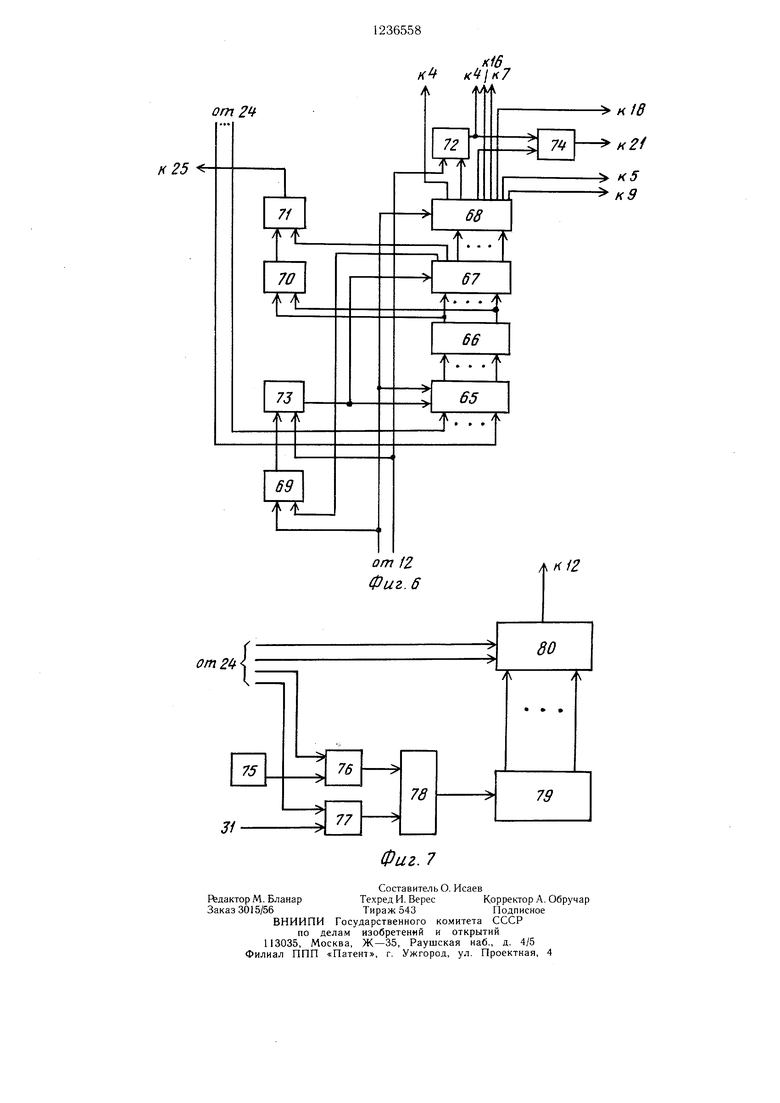

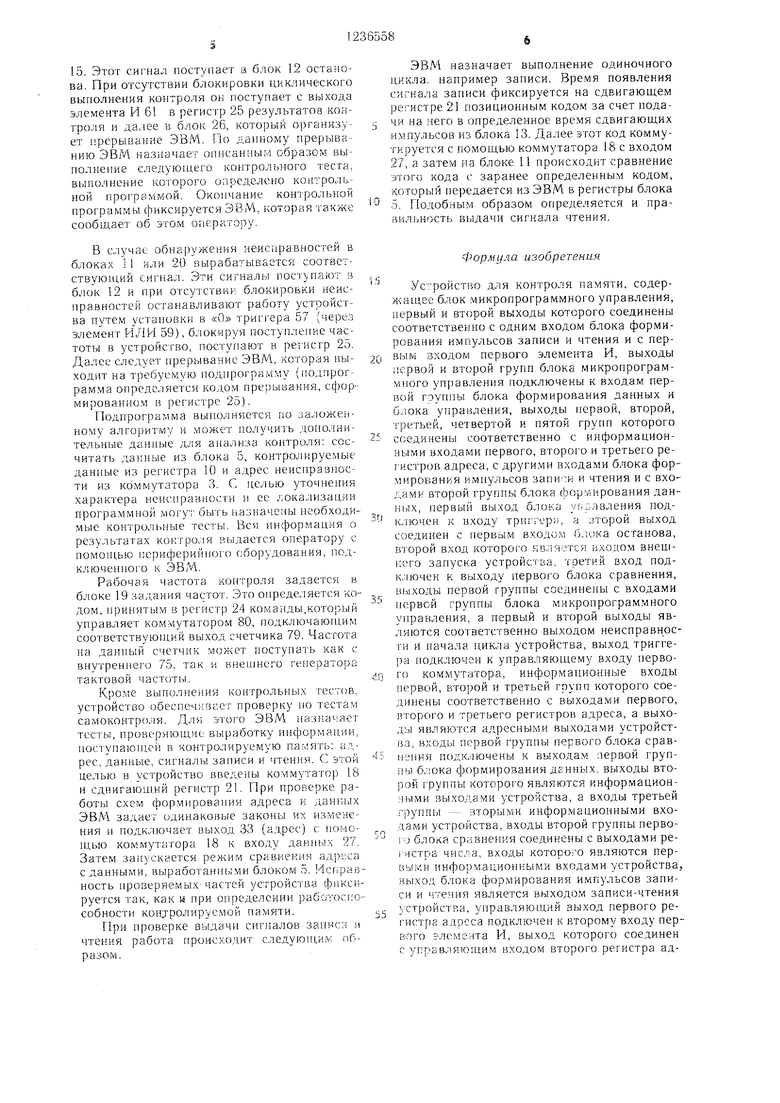

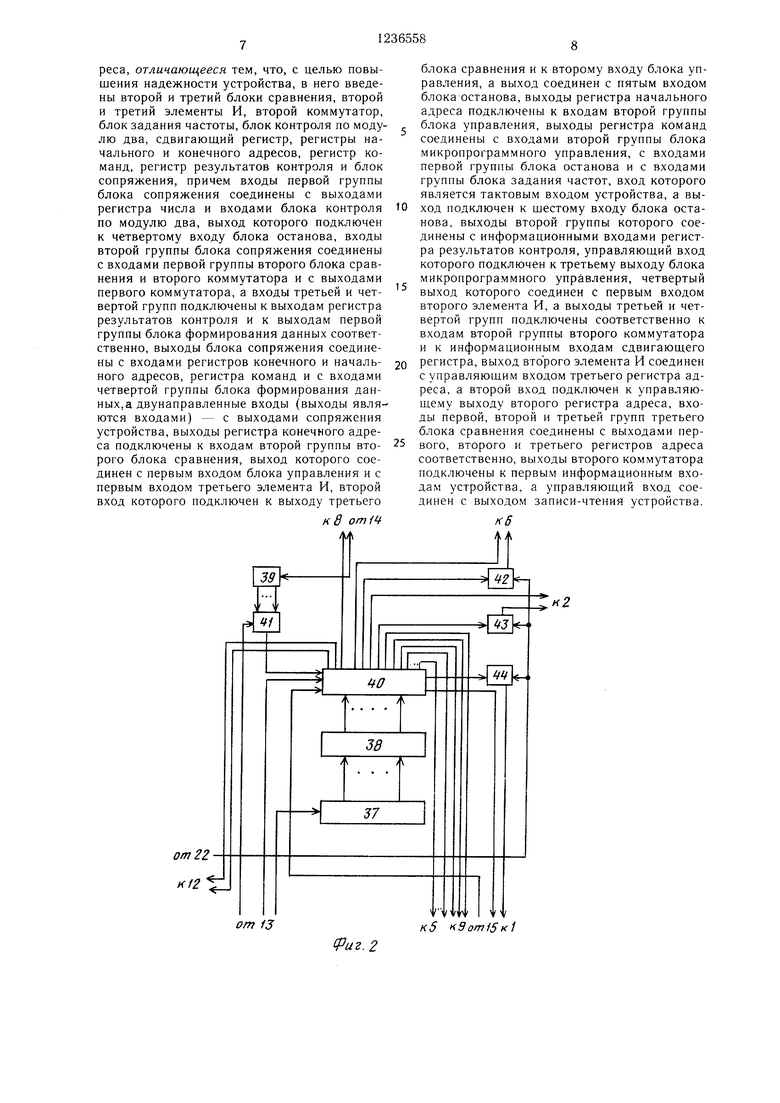

На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 - схема блока управления; на фиг. 3 - схема блока формирования данных; на фиг. 4 - схема блока формирования импульсов записи и чтения; на фиг. 5 - схема блока останова; на фиг. 6 - схема блока микропрограммного управления; на фиг. 7 - схема блока задания частот.

Устройство для контроля памяти содержит (фиг. 1) первый 1 и второй 2 регистры адреса, первый коммутатор 3, блок 4 управления, блок 5 формирования данных, третий регистр 6 адреса, первый элемент И 7, .триггер 8, блок 9 формирования импульсов записи и чтения, регистр 10 числа, первый блок И сравнения, блок 12 останова, блок 13 микропрограммного управления, второй 14 и третий 15 блоки сравнения, второй 16 и третий 17 элементы И, второй коммутатор 18, блок 19 задания частоты, блок 20 контроля по модулю два, сдвигаюш,ий регистр 21, регистры начального адреса 22, конечного адреса 23, команд 24, результатов контроля 25, блок 26 сопряжения, первый вход 27 устройства, предназначенный для приема контролируемых данных, второй вход 28 устройства, предназначенный для обмена информацией с управляющей ЭВМ или пультом управления, третий вход 29 устройства, предназначенный для приема эталонных данных, четвертый вход 30 устройства, предназначенный для приема сигнала внешнего запуска при работе устройства в составе других устройств или систем контроля, пятый вход 31 устройства, предназначенный для приема сигналов внешней тактовой частоты, первый выход 32 устройства, предназначенный для выдачи в блоки памяти сигналов записи и чтения, второй выход 33 устройства, пред- пазначенный для выдачи адреса в контролируемую память, третий выход 34 устройства, предназначенный для выдачи данных в контролируемую память, четвертый 35 и пятый 36 выходы устройства, предназначенные соответственно для выдачи сигналов о наличии неисправности и начале нового цикла контроля и используемые при работе устройства в составе других устройств и систем контроля.

Блок 4 управления содержит (фиг. 2) счетчик 37, дешифратор 38, сдвигающий регистр 39, первый 40, второй 41, третий 42, четвертый 43 и пятый 44 коммутаторы.

Блок 5 формирования данных содержит (фиг. 3) вход 29 эталонных данных, выход 34 контрольных данных, первый 45 и второй 46 регистры данных, первый 47, второй 48 и

третий 49 коммутаторы, третий 50 и блок 51 усилителей.

Блок 9 формирования импульсов записи и чтения содержит (фиг. 4) первый 52 и вто- рой 53 элементы И, первый 54 и второй 55 усилители, триггер 56.

Блок 12 останова содержит (фиг. 5) вход 30 для внешнего запуска, выход 35 для сигнала о неисправности, выход 36 для сигнала о начале нового цикла контроля, триггер 57, 0 первый 58, второй 59 и третий 60 элементы ИЛИ, первый 61, второй 62, третий 63 и четвертый 64 элементы И.

Блок 13 микропрограммного управления содержит (фиг. 6) счетчик 65 адреса, блок 66 постоянной памяти (выполненной, например, на основе микросхемы 556РТ7), дешифратор 67, регистр 68 управляющих триггеров, триггер 69, блок 70 контроля по модулю два, первый 71, второй 72, третий 73 и четвертый 74 элементы И.

0 Блок 19 задания частот содержит (фиг. 7) вход 31 внешней тактовой частоты, генератор 75 тактовой частоты, первый 76 и второй 77 элементы И, элемент ИЛИ 78, счетчик 79 и коммутатор 80.

Устройство работает следующим образом. 5Перед началом работы соответствующие входы-выходы устройства коммутируются с выходами-входами контролируемого блока памяти. Затем управляющая ЭВМ начинает выполнение контрольной программы. Для этого в устройство по интерфейсу через блок 26 сопряжения поступает соответствующая информация: в регистр 22 - начальный адрес контролируемого массива памяти, в регистр 23 - конечный адрес контролируемого массива, в регистры 45 и 46 блока формирования данных - начальные проверочные коды, в регистр 24 - код команды, определяющий режим работы устройства при контроле памяти (тип выполняемого теста, рабочую частоту контроля, циклический или одиночный режим контроля). Команда поо ступает в устройство последней. Сигнал записи, фиксирующий ее прием в регистр 24, транслируется из него далее в блок 12 останова. Последний устанавливает в «1 триггер 57, обеспечивающий подачу рабочей частоты через элемент И 64 в устройство, и посту- 5 пает в блок 13 микропрограммного управления. В этом блоке данный сигнал обеспечивает прием кода назначенного теста из регистра 24 команд в счетчик 65 адреса и включает частоту, поступающую с выхода элемента И 73 в качестве сигнала «-|-1 к содержимому счетчика адреса и на опрос дешифратора 67. С этого момента начинает выполняться микропрограмма.

Из блока постоянной памяти выбираются коды, соответствующие назначенной микро- j программе, которая зависит от типа назначенного контролирующего теста. Эти коды поступают на дещифратор 67, сигналы с которого устанавливают в соответствующее положе0

5

0

ние триггеры регистра 68. Управляющие потенциалы этах триггеров поступают в блоки устройства и подготавливают выполнение назначенного контрольного режима. В конце выполнения микропрограммы частота, поступающая в счетчик 65 и дещифратор 67, отключается путем установки триггера 69 в «О и включается частота, поступаюш,ая с выхода элемента И 72 в блок 4 управления. Этим действием управление от блока 13 передается блоку 4, который осуществляет управление назначенным контрольным режимом.

Выполнение микропрограммы сопровождается контролем выбираемых из постоянной памяти кодов по модулю два с помощью блока 70. Если неисправность в ходе программы не фиксируется, то далее выполняется контрольный режим. В том же случае, когда неисправность фиксируется и сигнал об этом с выхода элемента 71 поступает в регистр 25, блоком 26 сопряжения обеспечивается выдача в ЭВМ сигнала прерывания. По этому сигналу обеспечивается выполнение подпрограммы, повторяющей назначение контрольного режима. Если и при повторе фиксируется неисправность, то ЭВМ сообщает об этом оператору.

При передаче управления блоку 4 начинается выполнение режима в соответствии с временной диаграммой, реализуемой счетчиком 37 и дешифратором 38. Сигналы с данного дещифратора поступают на коммутатор 40, где они коммутируются в соответствии с назначенным режимом при помощи потенциалов, поступающих из блока 13 и, в ходе выполнения контроля, сигналами, поступающими из блоков 14 и 15 сравнения. Сигнал из блока 14 предварительно проходит селекцию с помощью сдвигающего регистра 39 и коммутатора 41, Селекция вызвана различным количеством циклов проверки заданного массива памяти в различных контрольных тестах.

Адреса контролируемых ячеек памяти в коде теста формируются с помощью первого 1, второго 2 и третьего 6 регистров адреса. Разрядность первого регистра определяется числом строк (т), а разрядность второго регистра числом столбцом (п) проверяемой матрицы. Разрядность третьего регистра равна разрядности проверяемого блока памяти (Р). Между этими величинами существует соотношение Р . Блок 12 сравнения в устройстве служит именно для фиксации момента равенства для данного соотношения. Кроме того, когда регистры 1 и 2 заполняются синхронно, данный блок фиксирует момент нахождения в регистре 6 адреса «диагонали контролируемой матрицы памяти. Блок 14 сравнения фиксирует момент равенства текущего и конечного адресов. При помощи элемента И 17 достигается определение момента равенства текущего, базового и конечного адресов, что происходит при окончании проверки заданного массива. Элементы И 7 и 16 предназначены для соответствующей коммутации регистров адреса при выполнении тестов с различными вариантами перебора адресов. Выдача конкретного адреса в контролируемую память , происходит через коммутатор 3, управляемый триггером 8.

Формирование контрольных данных происходит в блоке 5 с помощью регистров 45 и 46, информация в которые первоначально поступает из ЭВМ. Информация

0 в этих регистрах изменяется под воздействием сдвигающих импульсов, поступающих из блока 4 управления. В цепи переноса этих регистров включены коммутаторы 47 и 48. Они позволяют формировать в регистрах кроме простых кодов («О-.-.О,

«11, щахматный код, бегущая «1, бегущий «О и т. д.) псевдослучайные последовательности. Контрольный код в блоке 5 формируется как за счет указанных изменений в регистрах, так и за счет возможности под0 ключения к выходу блока при помощи коммутатора 49 то одного, то другого регистра. Коммутаторы 47 и 48 управляются блоком 13 микропрограммного управления, коммутатор 49 управляется как блоком 13, так и блоком 4 управления, осуществляющего переключе5 ние триггера 50, выход которого подключен к управляющему входу коммутатора. Кроме того, на выход блока может подключаться информация, поступающая из эталонного блока (вход 29). Это используется при контроле блоков постоянной памяти методом эталонного

° сравнения. Сформированный код выдается в контролируемую память с выхода 3 через усилители 51.

Формирование импульсов записи и чтения происходит в блоке 9. Импульсы записи и чтения появляются на выходах элементов И 52

и 53. Условием их появления является отсутствие блокировки из блока 13, соответствующее состояние триггера 56 и наличие опроса элементов 52 и 53 из блока 4 управления. Импульсы записи и чтения поступают в конт0 ролируемые блоки памяти через усилители 54 и 55.

В процессе контроля предварительно записанная в контролируемые блоки информация считывается и через вход 27 поступает в

регистр 10 числа. С выхода этого регистра данные поступают в блок 11 сравнения и в блок 20 контроля по модулю два. В блоке 11 происходит сравнение контрольных данных, поступающих из блока 5, и данных,

Q принятых из контролируемой памяти. В блоке 20 контролируемая информация проверяется по модулю два (например, при контроле постоянной памяти). Если неисправность данными блоками не фиксируется, то устройство продолжает работу по выполнению установ5 ленного контрольного режима. Конец работы по данному режиму фиксируется появлением сигнала на выходе элемента И 17. Это происходит при сравнении адресов в блоках 14 и

15. Этот сигнал поступает в блок 12 останова. При отсутствии блокировки циклического выполнения контроля ок поступает с выхода элемента И 61 в регистр 25 результатов контроля и далее в блок 26, который организует прерывание ЭВМ. По дапному прерыванию ЭВМ назначает описан н м образом выполнение следующего контрольного теста, выполнение fiOTOporo определено конгроль- ной про1 раммой. Окончание контрольной программы фиксируется ЭВМ. которая также сооби.1ает об этом оператору.

В случае обнаружения неисправностей в блоках 1 1 или 20 вырабатывается соответствующий сигнал. Эти сигналы поступают и блок 12 и при отсутствии блокировки неисправностей останавливают работу устройства путем устаповки в «О триггера 57 (через элемент ИЛИ 59), блокируя поступление частоты в устройство, поступают в регистр 25. Далее следует прерывание ЭВМ, которая выходит на требуемую подпрО1-рамму (подпрог- определяется кодом прерывания, cq)op- мированном в регистре 2о).

Подпрограмма выполняется по за;1ожен- ному алго1) и .может получить . дополнительные данные для анализа контроля: сосчитать данные из блока 5, контролируемые данные из регистра 10 и адрес неисправности из коммутатора 3. С целью уточнения характера неисправности и ее локализации программной могут быть назначены необходи- .мые контрольные тесты. Вся информация о результатах контроля выдается оператору с помон1,ью нериферийного оборудования, подключенного к ЭВ/ Л.

Рабочая частота контроля задается в блоке 19 зал.ания час тот. Это онределяется кодом, принятым в ре истр 24 команды,который управляет коммутатором 80, подключаюпгим соответствуюп1,ий выход счетчика 79. Частота на данный счетчик может поступать как с внутреннего 75. так и генератора тактовой частоты.

Кроме выполнения контрольных тестов, устройство обеспечивает проверку но тестам самоконтроля. Для этого ЭВМ назначает тесты, проверяющие выработку информации, поступающей в контролируемую па.мять: адрес, данные,сигналы записи и чтения. С этой целью в устройство введены коммутатор 18 и сд,вигаюш,ий регистр 21. При проверке работы схем формирования адреса и данных ЭВМ задает одинаковые законы их изменения и подключает выход 33 (адрес) с iiorvio- 11{ыо коммутатора 18 к входу данным 27. Затем запускается режим сравнения с данными, выработаннь ми блоком 5. Исправность проверяемых- частей устройства фиксируется так, как и при оп.ределенип работос1;о- собности контролируемой памяти.

При проверке выдачи сигналов запис:-; и чтения работа происходит следуюп1,им образом.

ЭВМ назначает выполнение одиночного цикла, например записи. Время появления сигнала записи фиксируется на сдвигающем регистре 21 позиционным кодом за счет подачи на него в определенное время сдвигающих импульсов из блока 13. Далее этот код коммутируется с помощью коммутатора 18 с входом 27, а затем па блоке 11 происходит сравнение этого кода с заранее определенным кодом, который передается из ЭВМ в регистры блока

5, По.аобным образом определяется и пра- вильж сть выдачи сигнала чтения.

Формула изобретения

Усгройстр.о для контроля памяти, содержащее блок микропрограммного управления, первый и второй выходы которого соединены соответственно с одним входом блока формирования импульсов записи и чтения и с первым входом первого элемента И, выходы первой и второй групп блока мккропрограм- .viHoro управления подключены к входам первой гоуппы блока формирования данных и блока управления, выходы первой, второй, третьей, четвертой и пятой групп которого соединены соответственно с информационными входами первого, второго и третьего регистров адреса, с другими входами блока формирования импульсов записи и чтения и с вхо- ;;,ами второй группы блока (Ьорулрования данных, первый выход блока ;. Гг-;.;1вления подключен к входу триггера, а второй выход соединен с первым входом блока останова, второй вход которого является входом внещ- него запуска устройства, третий вход под- к.:1ючен к выходу первого блока сравнения, выходы первой группы соединены с входами первой группы блока микропрограммного управления, а первый и второй выходы являются соответственно выходом неисправнос- ги и начала цикла устройства, выход триггера подключен к управляющему входу первого коммутатора, информационные входы нервой, второй и третьей групп которого соединены соответственно с выходами первого, irroporo и третьего регистров адреса, а выходы являются адресными выходами устройства, входы первой группы первого блока срав- 1Г :;11Ия подключены к выхолТ,ам первой группы блока формирования денных, выходы второй группы которого являются информационными выходами устройства, а входы третьей групгпз -- вторыми информационными вхо- .аами устройства, входы второй группы перво- I о блока сравнения соединены с выходами ре- | истра числа, входы KOTOpoi являются первыми информационными входами устройства, выход б„тока формирования импульсов записи и чтения является выходом записи-чтения устройства, управляющий выход первого регистра а.цреса подключен к второму входу первого элемента И, выход которого соединен с управляю:цим входом второго регистра адреса, отличающееся тем, что, с целью повышения надежности устройства, в него введены второй и третий блоки сравнения, второй и третий элементы И, второй коммутатор, блок задания частоты, блок контроля по модулю два, сдвигающий регистр, регистры начального и конечного адресов, регистр команд, регистр результатов контроля и блок сопряжения, причем входы первой группы блока сопряжения соединены с выходами регистра числа и входами блока контроля по модулю два, выход которого подключен к четвертому входу блока останова, входы второй группы блока сопряжения соединены с входами первой группы второго блока сравнения и второго коммутатора и с выходами первого коммутатора, а входы третьей и четвертой групп подключены к выходам регистра результатов контроля и к выходам первой группы блока формирования данных соответственно, выходы блока сопряжения соединены с входами регистров конечного и начального адресов, регистра команд и с входами четвертой группы блока формирования данных,а двунаправленные входы (выходы являются входами) - с выходами сопряжения устройства, выходы регистра конечного адреса подключены к входам второй группы второго блока сравнения, выход которого соединен с первым входом блока управления и с первым входом третьего элемента И, второй вход которого подключен к выходу третьего

к 8 omi4

о т 22 к12

от 13

ipuz.Z

0

5

0

5

блока сравнения и к второму входу блока управления, а выход соединен с пятым входом блока останова, выходы регистра начального адреса подключены к входам второй группы блока управления, выходы регистра команд соединены с входами второй группы блока микропрограммного управления, с входами первой группы блока останова и с входами группы блока задания частот, вход которого является тактовым входом устройства, а выход подключен к шестому входу блока останова, выходы второй группы которого соединены с информационными входами регистра результатов контроля, управляющий вход которого подключен к третьему выходу блока микропрограммного управления, четвертый выход которого соединен с первым входом второго элемента И, а выходы третьей и четвертой групп подключены соответственно к входам второй группы второго коммутатора и к информационным входам сдвигающего регистра, выход второго элемента И соединен с управляющим входом третьего регистра адреса, а второй вход подключен к управляющему выходу второго регистра адреса, входы первой, второй и третьей групп третьего блока сравнения соединены с выходами первого, второго и третьего регистров адреса соответственно, выходы второго коммутатора подключены к первым информационным входам устройства, а управляющий вход соединен с выходом записи-чтения устройства.

Кб

к5 к9от15к1

от 13

к tt,Z6 Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля и регистрации асинхронных сигналов интерфейса | 1982 |

|

SU1084803A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Устройство для контроля полупроводниковой памяти | 1985 |

|

SU1319079A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля полупроводниковых оперативных и постоянных запоминающих устройств. Целью изобретения является расширение функциональных возможностей за счет контроля блоков оперативной и постоянной памяти и повышение надежности устройства. Устройство для контроля памяти содержит регистры адреса 1, 2, 6, коммутаторы 3, 18, блок 13 микропрограммного управления, блоки формирования данных 5 и импульсов записи и чтения 9, регистр 10 числа, блоки 11, 14., 15 сравнения, блок 12 останова, блок 10 задания частот, блок 20 контроля по модулю два, регистры сдвигаюш.ий 21, начального 22 и конечного 23 адресов, команд 24 и результатов контроля 25, блок 26 сопряжения. Перед началом работы управляющая ЭВМ через блок 26 сопряжения загружает регистры 21-25. По команде с регистра 24 запускается блок 13 микропрограммного управления, формирующий контролирующий тест. При .обнаружении ошибки блоком 11 сравнения формируется сигнал прерывания. В устройстве обеспечивается режим самоконтроля путем выдачи тестовых воздействий с выходов коммутатора 18 на информационные входы устройства. Предлагаемое устройство обеспечивает возможность управления процессом контроля с помощью ЭВМ. 7 ил. $ (Л ю со О5 ел О1 00

от 17

о т 20

Фиг.5

Ki6

к

от 24к25

н1В

от 12 Фиг. 6

/

Kf2

о т 2

80

t

79

Составитель О. Исаев

Редактор М. БланарТехред И. ВересКорректор А. Обручар

Заказ 3015/56Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

Фиг. 7

| Устройство для контроля полупроводниковой памяти | 1981 |

|

SU945904A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля памяти | 1980 |

|

SU934553A2 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1986-06-07—Публикация

1984-07-13—Подача