316

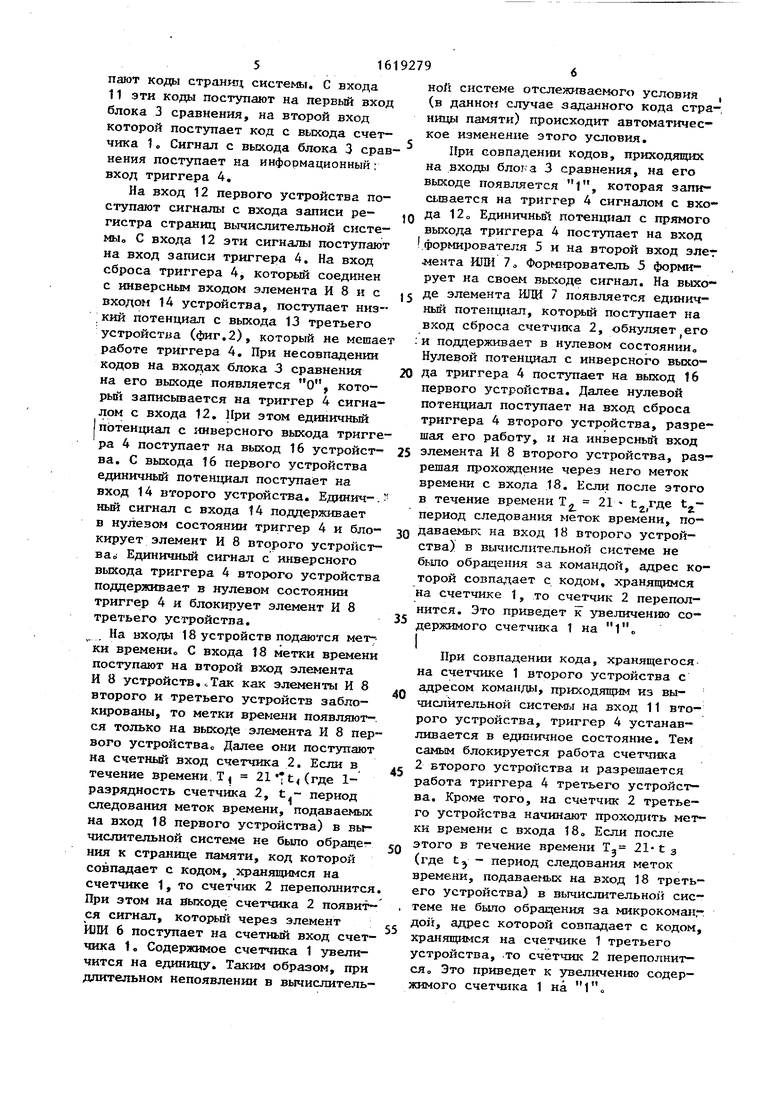

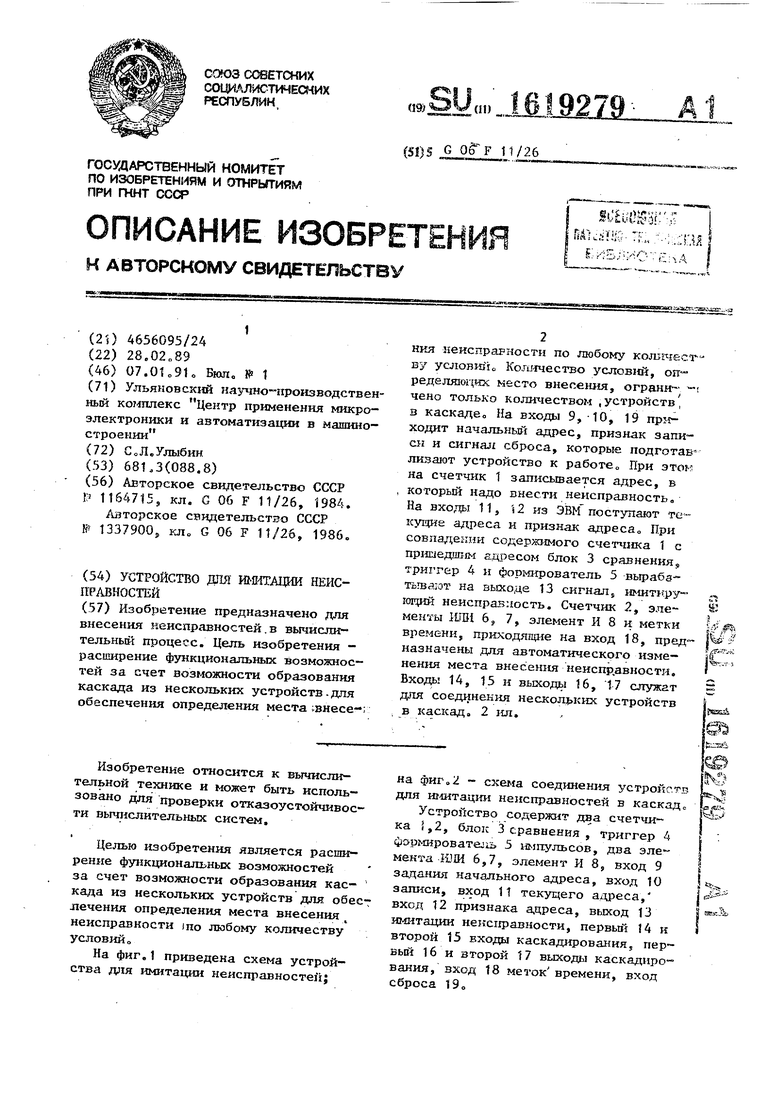

Схема соединения (фиг „.2) содержит каскад из п устройств 20 имитации неисправностейо Устройство позволяет изменить место внесения неисправностей как вручную (программно), так и автоматически (аппаратно).

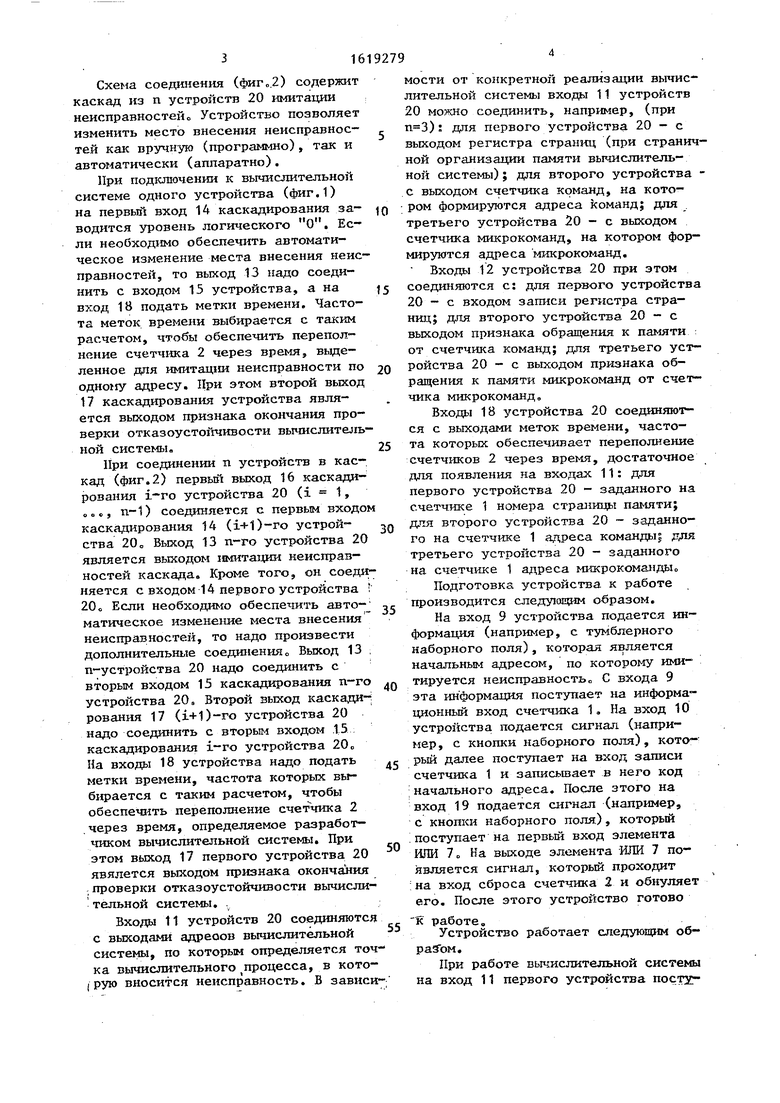

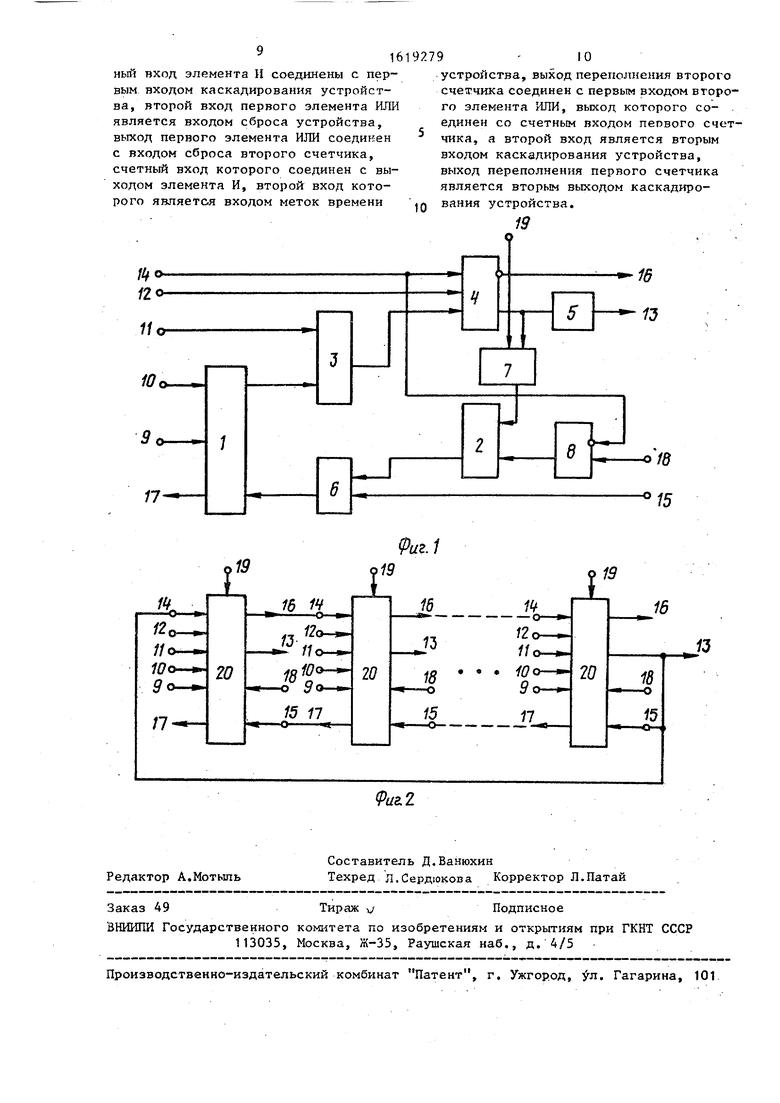

При подключении к вычислительной системе одного устройства (фиг.1) на первый вход 14 каскадирования заводится уровень логического О. Если необходимо обеспечить автоматическое изменение места внесения неисправностей, то выход 13 надо соединить с входом 15 устройства, а на вход 18 подать метки времени. Частота меток времени выбирается с таким расчетом, чтобы обеспечить переполнение счетчика 2 через время, выделенное для имитации неисправности по одному адресу. При этом второй выход 17 каскадирования устройства является выходом признака окончания проверки отказоустойчивости вычислительной системы,

При соединении п устройств в каскад (фиг.2) первый выход 16 каскадирования i-го устройства 20 (i 1, ««с, п-1) соединяется с первым входом каскадирования 14 (i-M)-ro устрой- ства 20о Выход 13 n-го устройства 20 является выходом имитации неисправностей каскада. Кроме того, он соединяется с входом 14 первого устройства 20„ Если необходимо обеспечить автоматическое изменение места внесения неисправностей, то надо произвести дополнительные соединения., Выход 13 , п-устройства 20 надо соединить с вторым входом 15 каскадирования п-го устройства 20, Второй выход каскадирования 17 (1+1)-го устройства 20 надо соединить с вторым входом 15 каскадирования 1-го устройства 20„ На входы 18 устройства надо подать метки времени, частота которых выбирается с таким расчетом, чтобы обеспечить переполнение счетчика 2 через время, определяемое разработчиком вычислительной системы. При этом выход 17 первого устройства 20 явялется выходом признака окончания проверки отказоустойчивости вычислительной системы. .

Входы 11 устройств 20 соединяются с выходами адресов вычислительной системы, по которым определяется точка вычислительного(процесса, в кото- I рук вносится неисправность. В зависи

-

10

15

20

25

м JQ , т/

35

40

45

50

55

мости от конкретной реализации вычислительной системы входы 11 устройств 20 мотао соединить, например, (при ): для первого устройства 20 - с выходом регистра страниц (при страничной организации памяти вычислительной системы); для второго устройства - с выходом счетчика команд, на котором формируются адреса команд; для третьего устройства 20 - с выходом счетчика микрокоманд, на котором формируются адреса микрокоманд.

Входы 12 устройства 20 при этом соединяются с: для первого устройства 20 - с входом записи регистра страниц; для второго устройства 20 - с выходом признака обращения к памяти от счетчика команд; для третьего устройства 20 - с выходом признака обращения к памяти микрокоманд от счетчика микрокоманд.

Входы 1В устройства 20 соединяются с выходами меток времени, частота которых обеспечивает переполнение счетчиков 2 через время, достаточное для появления на входах 11: для первого устройства 20 - заданного на счетчике 1 номера страницы памяти; для второго устройства 20 - заданного на счетчике 1 адреса команды для третьего устройства 20 - заданного на счетчике 1 адреса микрокоманды

Подготовка устройства к работе производится следующим образом.

На вход 9 устройства подается информация (например, с тумблерного наборного поля), которая является начальным адресом, по которому имитируется неисправностьс С входа 9 эта информация поступает на информационный вход счетчика 1. На вход 1О устройства подается сигнал (например, с кнопки наборного поля), кото- рый далее поступает на вход записи счетчика 1 и записывает в него код начального адреса. После этого на вход 19 подается сигнал (например, с кнопки наборного поля), который поступает на первый вход элемента ИЛИ 7 о На выходе элемента ИЛИ 7 появляется сигнал, который проходит на вход сброса счетчика 2 и обнуляет его. После этого устройство готово

к работе.

Устройство работает следующим об- раЗом.

При работе вычислительной системы на вход 11 первого устройства посту

пают коды страниц системы. С входа 11 эти коды поступают на первый вход блока 3 сравнения, на второй вход которой поступает код с выхода счетчика 1« Сигнал с выхода блока 3 сравнения поступает на информационный; вход триггера 4.

На вход 12 первого устройства поступают сигналы с входа записи регистра страниц вычислительной системы С входа 12 эти сигналы поступают на вход записи триггера 4. На вход сброса триггера 4, который соединен с инверсным входом элемента И 8 и с входом 14 устройства, поступает низкий потенциал с выхода 13 третьего устройства (фиг.2), который не мешае работе триггера 4. При несовпадении кодов на входах блока 3 сравнения на его выходе появляется О, который записывается на триггер 4 сигналом с входа 12. При этом единичный потенциал с инверсного выхода триггера 4 поступает на выход 16 устройства. С выхода 16 первого устройства единичный потенциал поступает на вход 14 второго устройства. Единич-. ный сигнал с входа 14 поддерживает в нулевом состоянии триггер 4 и блокирует элемент И 8 второго устройства Единичный сигнал с инверсного выхода триггера 4 второго устройства поддерживает в нулевом состоянии триггер 4 и блокирует элемент И 8 третьего устройства.

На входы 18 устройств подаются мет-, ки времени,, С входа 18 метки времени поступают на второй вход элемента И 8 устройств.сТак как элементы И 8 второго и третьего устройств заблокированы, то метки времени появляют-. ся только на выходе элемента И 8 первого устройствас Далее они поступают на счетный вход счетчика 2. Если в течение времени Т 21 (где 1- разрядность счетчика 2, t - период следования меток времени, подаваемых на вход 18 первого устройства) в вычислительной системе не было обращения к странице памяти, код которой совпадает с кодом, хранящимся на счетчике 1, то счетчик 2 переполнится При этом на въпсоде счетчика 2 появится сигнал, который через элемент ИЛИ 6 поступает на счетный вход счетчика t. Содержимое счетчика 1 увеличится на единицу. Таким образом, при длительном непоявлении в вычислитель0

5

0

5

0

5

0

5

0

5

ной системе отслеживаемого условия , (в данном случае заданного кода страницы памяти) происходит автоматическое изменение этого условия.

При совпадении кодов, приходящих на входы блока 3 сравнения, на его выходе появляется 1, которая записывается на триггер 4 сигналом с входа 120 Единичный потенциал с прямого выхода триггера 4 поступает на вход формирователя 5 и на второй вход элет лента ИЛИ 7„ Формирователь 5 формирует на своем выходе сигнал. На выходе элемента ИЛИ 7 появляется единичный потенциал, который поступает на вход сброса счетчика 2, обнуляет(его и поддерживает в нулевом состоянии0 Нулевой потенциал с инверсного выхода триггера 4 поступает на выход 16 первого устройства. Далее нулевой потенциал поступает на вход сброса триггера 4 второго устройства, разрешая его работу, и на инверсный вход элемента И 8 второго устройства, разрешая прохождение через него меток времени с входа 18. Если после этого в течение времени Т- 21 период следования меток времени, по- даваемьгк на вход 18 второго устройства) в вычислительной системе не было обращения за командой, адрес которой совпадает с кодом, хранящимся на счетчике 1, то счетчик 2 переполнится. Это приведет к увеличению содержимого счетчика 1 на 1,,

I

При совпадении кода, хранящегося

на счетчике 1 второго устройства с адресом команды, приходящим из вычислительной системы на вход 11 второго устройства, триггер 4 устанавливается в единичное состояние. Тем самым блокируется работа счетчика 2 второго устройства и разрешается работа триггера 4 третьего устройства. Кроме того, на счетчик 2 третьего устройства начинают проходить метки времени с входа 18 Если после этого в течение времени 21 t 3 (где t5 - период следования меток времени, подаваемых на вход 18 третьего устройства) в вычислительной системе не было обращения за микрокомандой, адрес которой совпадает с кодом, хранящимся на счетчике 1 третьего устройства, .то счетчик 2 переполнится,, Это приведет к увеличению содержимого счетчика 1 на

При совпадении кода, хранящего- ся ha счетчике 1 третьего устройства с адресом микрокоманды, приходящим из вычислительной системы на вхо 11 третьего устройства, триггер 4 устанавливается в единичное состояние„ При этом на выходе формирователя 5 формируется сигнаг, имитирующий Tie- исправность, который поступает на выход 13 устройства, С выхода 13 третьего устройства этот сигнал поступает в вычислительную систему и имитирует в ней неисправность Кроме тогэ, этот сигнал поступает на вход 15 третьего устройства и на вход 14 первого устройства. С входа 15 третьего устройства сигнал через элемент ИЛИ 6 поступает на счетный вход счетчика 1, увеличивая его со- держимое на 1. Таким образом5обеспечивается автоматическое изменение адресов, по которым имитируется неисправность о

Сигнал с ихода 14 первого уст- ройства обнуляет триггер 4, что приводит к разблокированию счетчика 2 первого устройства, а также к обну- пению триггеров 4 и блокированию меток времени во втором и третьем уст- ройствах.

Следующая имитация будет произведена при новом вхождении программы в страницу памяти, код которой указан на счетчике 1 первого устройства, и при выполнении микрокоманды, адрес которой вновь сформирован на счетчике 1 третьего устройства, команды, адрес которой совпадает с кодом на счетчике 1 второго устройства

После того, как по данной команде будет смонтирована неисправность во всех микрокомандах, счетчик 1 третьего устройства переполнится. Сигнал переполнения с выхода счетчика 1 по- ступает на выход 17 третьего устройства, далее на вход 15 второго ройства. С входа 15 сигнал через элемент ИЛИ 6 поступает на счетный вход счетчика 1 второго устройства, увеличивая его содержимое на

После того, как неисправность будет смонтирована во все микрокоманды всех команд, расположенных в данной странице памяти, счетчик 1 второго устройства переполнитсяо Сигнал переполнения с выхода счетчика 1 че- ме.з выход 17 второго устройства по- ступает на вход 15 первого устрой

ства. С входа 15 этот сигнал через элемент ИЛИ 6 поступает на счетный вход счетчика 1 первого устройства, увеличивая его содержимое на 1.

На выходе 17 появится сигнал после того, как неисправность будет смонтирована во все микрокоманды, всех команд, расположенных во всех страницах памяти. Этот сигнал является признаком окончания полной проверки отказоустойчивости вычислительной системы

Таким образом, предлагаемое устройство позволяет за счет каскадирования более точно определить в вычислительном процессе точку, в которую вносится неисправность, что позволяет увеличить число точек вычислительного процесса для имитации неисправно тей и приводит к более полной проверке отказоустойчивости вычислительных систем.

5 Q

5

0

Формула изобретения

Устройство для имитации неисправностей, содержащее два счетчика, блок сравнения, триггер, формирователь импульсов, два элемента ИЛИ, элемент И, причем первый вход блока сравнения является входом текущего адреса устройства, вход записи триггера является входом признака устройства, прямой выход триггера соединен с первым входом первого элемента ИЛИ, выход формирователя импульсов является выходом имитации неисправности устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет образования каскада из нескольких устройств для обеспечения определения места внесения неисправности по любому количеству условий, информационный вход и вход записи первого счетчика являются соответственно входом задания начального адреса и входом записи устройства, информационный выход первого счетчика соединен с вторым входом блока сравнения, выход которого соединен с информационным входом триггера, инверсный выход которого является первым выходом каскадирования устройства, прямой выход триггера соединен с входом формирователя импульсов, вход сброса триггера и инверс17

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство для имитации неисправностей | 1989 |

|

SU1755283A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1267415A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

Фиг.1

Авторы

Даты

1991-01-07—Публикация

1989-02-28—Подача