Ф

00

Изобретение относится к вычислительной технике и может найти широкое применение для оценки прведения цифровых вычислительных машин при определенных неисправностях, чт необходимо при отработке оборудования и про грамм, выполняющих контроль и диагностирование неисправностей цифровы вычислительных машин.

Известно устройство автоматическго ввода неисправности, которое обеспечивает ввод неисправности на заданный вход интегральной схемы в виде любого из уровней напряжения в соответствии с заданным уровнем напряжения и номером входа CllНедостатком является то, что устройство не обеспечивает ввод неисправности в заданный момент времени. Наиболее близким к предлагаемому по технической сущности является устройство, генерирующее тест-сигналы, имитируквдие сшибки ЭВ, содержащее генератор импульсов установленной длительности, выход которого является выходом устройства, регистр адресов команд, регистр установки произвольного адреса, схему.сравнения, первый вход которой соединен с выходом регистра установки произвольного адреса, второй - с выходом регистра адресов команд, вход которого является первым входом устройства 2J.

Недостатком данного устройства является то, что момент ввода неисправности определяется только адресом команды, выполняемой цифровой вычислительной машиной (ЦВМ), вследствие «его неисправность вводится только на первом т&кте выполнения команды. Большинство же команд в ЦВМ являются многотактными и поведение Ц№ существенно зависит от того, на каком такте выполнения той или иной команды возникает неисправность.

Цель изобретения - расширение функциональных возможностей путем имитации неисправностей на любом заданном такте выполнения команды. Поставленная цель достигается

тем, что в устройство для имитации

.неисправностей цифровой вычислительной машины, содержащее два регистра адреса, блок сравнения адресо формирователь импульсов, причем группа входов первого регистра адреса является группой входов устройства, группы выходов первого и второго регистров адреса соединены соответственно с первой и второй группами входов блока сравнения адресов, выход формирователя импульсов является выходом устройства, введены триггер, aJieMOHT И, блок сравнения тактов, реги9тр тактов, счетчик тактов, причем выход блока сравнения адресов соединен с единичным входом триггера, единичный выход которого соединен с первым входом элемента И, второй вход последнего связан с выходом блока сравнения тактов, первая и вторая труппы входов которого соединены соответственно с группами выходов счетчика тактов и регистра тактов, выход элемента И соединен с входом формирователя импульсов и запрещающим входом счетчика тактов, счетный вход которого является вхот дом устройства, нулевой выход триггера соединен с входом нулевых установок счетчика тактов.

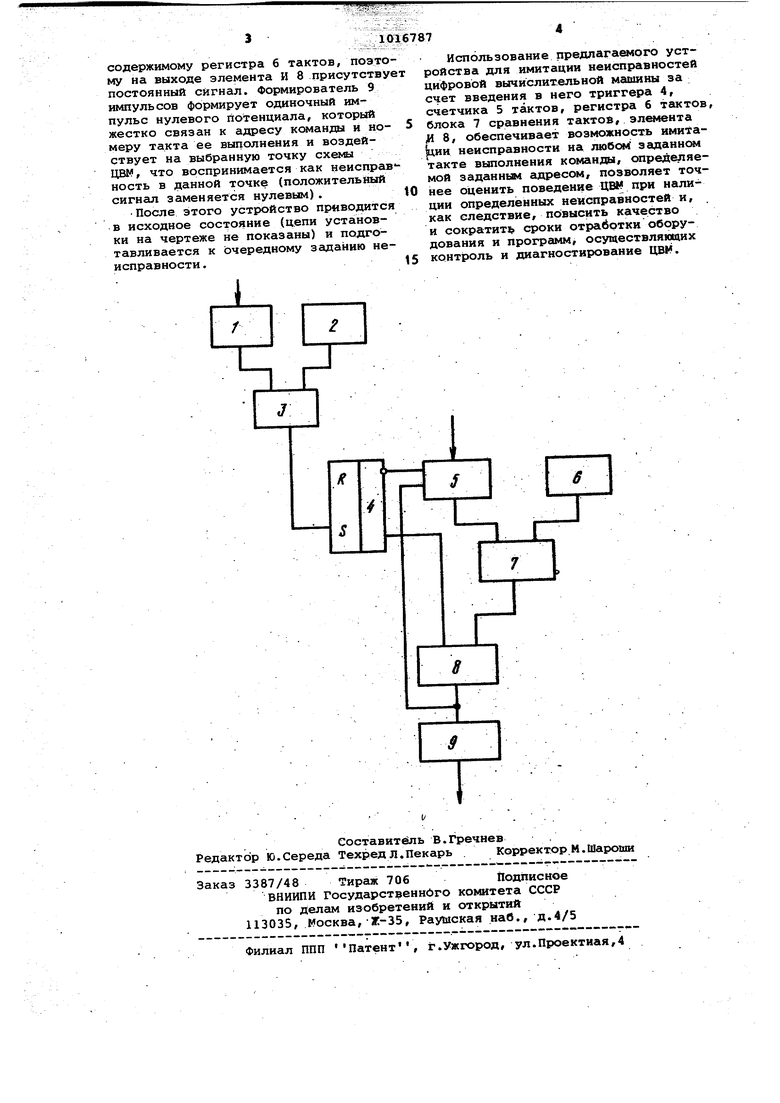

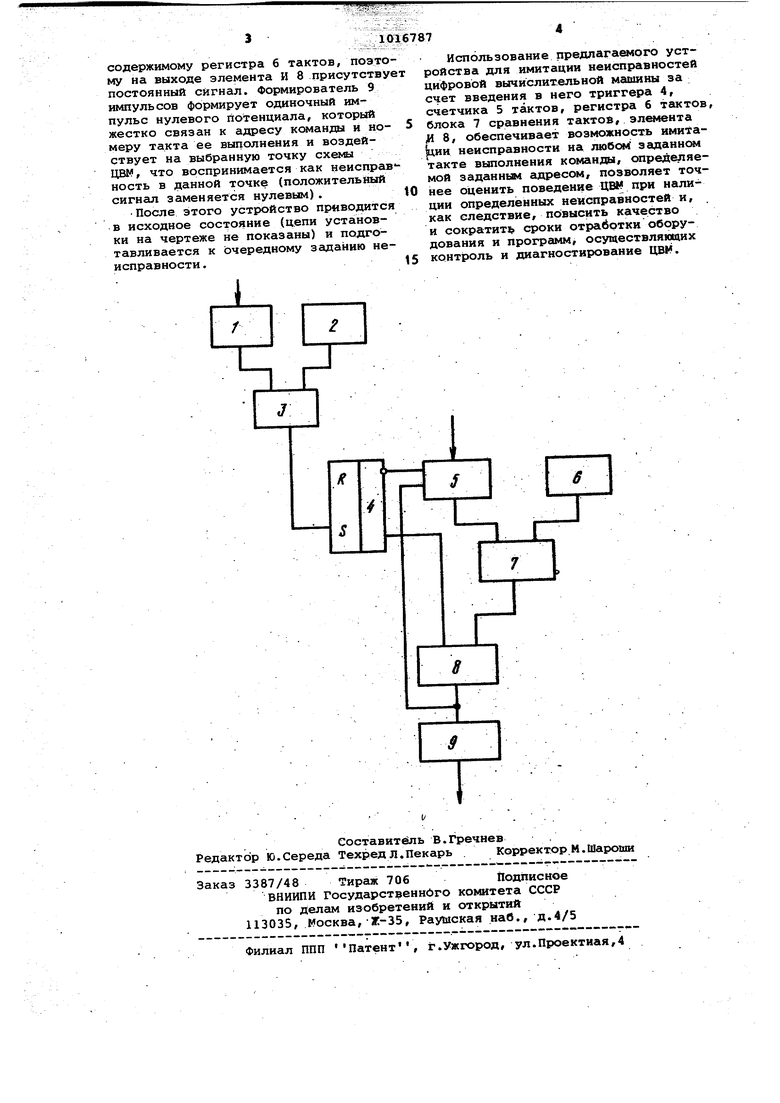

На чертеже изображена структурная схема предлагаемого устройства.

Устройство содержит первый регистр 1 адреса, второй регистр 2 адреса, блок 3 сравнения адреса, триггер 4, счетчик 5 тактов, регистр 6 тактов, блок 7 сравнения тактов, элемент И 8, формирователь 9 импульсов

Устройство работает следующим образом.

При подготовке устрюйства к работе группа входов первого регистра 1 адреса подключается к регистру адреса команд (или к цепям передачи адреса команд) ЦВМ. Счетный вход счетчика 5 тактов подключается к генератору тактовой частоты ЦВМ. Выход устройства подключается к выбранной точке схемы ЦВМ, в которой необходимо имитировать неисправность. В исходном состоянии первый регистр 1 адреса, триггер 4, счетчик 5 тактов обнулены, второй регистр 2 адреса и регистр б тактов находятся в произт вольном состоянии.Для внесения неисправности в некоторую точку схемы ЦВМ пр выполнении К-го такта команды А на втором регистре 2 гщреса устанавливается адрес А, на регистре 6 тактов устанавливается номерг такта К. При выполнении программы в определенный момент времени в первый регистр 1 адреса записывается адрес равный Аи на выходе блока 3 сравнения адреса появляется сигнал сравнения, под действиетл которого триггер 4 переходит в единичное состояние. При Этом снимается сигнал с входа обнуления счетчика 5 тактов и счетчик начинает считать импульсы тактовой частоты ЦВМ, поступающие на его счетный вход. В момент сравнения содержимого счетчика 5 тактов с содержимым регистра б тактов на выходе блока 7 сравнения тактов появляется сигнал, при совпадении которого с сигналом на единичном выходе триггера 4 формируется сигнал на выходе элмента и 8, который запускает формирователь 9 импульсов и одновременно поступает на запрещающий вход счетчика 5 тактов. Счет импульсов тактовой частоты прекращается, содержимое счетчика 5 тактов сохраняется равным

содержимому регистра 6 тактов, поэтому на выходе элемента И 8 присутствуе постоянный Сигнал. Формирователь 9 импульсов формирует одиночный импульс нулевого потенциала, который жестко связан к адресу ксманды и номеру такта ее выполнения и воздействует на выбранную точку схемы ЦВМ, что воспринимается как неисправ ность в данной точке (положительный сигнал заменяется нулевым).

После этого устройство приводится в исходное состояние (цепи установки на чертеже не показаны) и подготавливается к очередному заданию неисправности.

Использование предлагаемого устройства для имитации неисправностей цифровой вычислительной машины за счет введения в него триггера 4, счетчика 5 тактов, регистра 6 тактов блока 7 сравнения тактов, элемента ji 8, обеспечивает возможность имита|ции неисправности на moCiOvt заданнс « такте выполнения команды, опрейедяемой заданным адресом, позволяет точнее оценить поведение UBIf при налиции определённых немсправностей и, как следствие, повысить качество и сократить сроки отработки оборудования и программ, осуществляющих контроль и диагностирование ЦВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1984 |

|

SU1164715A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536387A1 |

| Устройство для имитации неисправностей | 1985 |

|

SU1283775A1 |

| Устройство для имитации сбоев и неисправностей цифровой вычислительной машины | 1985 |

|

SU1265779A1 |

| Устройство для имитации неисправностей | 1985 |

|

SU1273933A1 |

| Устройство для проверки программ на сбоеустойчивость | 1986 |

|

SU1411753A2 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

| Устройство для имитации неисправностей ЭВМ | 1989 |

|

SU1718223A1 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

УСТРОйеТЮ,ДЛЯ ИМИТАЦИИ НЕИСПРАВНОСТЕЙ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ, содержащее два регистра адреса, блок сравнения ахфесов, форгмирователь импульсов, причем группа входов первого регистра адреса является группой входов устройCTBaj группы выходов первого и второго регистров адреса соединены соответственно с первой и второй группами входов блока сравнения адресов, выход формирователя импульсов является выходом устройства, отличающееся тем, что, с целью расшиг рения его функциональных возможностей путем имитации неисправностей на любом заданном такте выполнения команды, в него введены триггер, элемент И, блок сравнения тактов, регистр тактов, счетчик тактов, причем выход блока сравнения адресов : соединения единичным входе триггера, единичный выход которого соединен с первым входом элемента И, второй вход последнего связан с выходом блока сравнения тактов, первая и вторая группы входов которого соединены соответственно с группами илходов счетчика тактов и perHctpa тактов, выход элемента и соедаиеи с входом формирователя импульсов и запре«а«вв«им входом счетчика тактов, счетный вход которого является входтал устройства, нулевой выход триггера соединен с входом нулевых установок счетчика тгистов.

Ч

г- f

ff

ч

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент СЗДА 4156132, кл | |||

| G, 06 F 11/00, опуОлик | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1983-05-07—Публикация

1982-01-22—Подача