11Г

Изобретение относится к рачиитех- нике и связи и может испо.ш.яова- но в измерительной технике, в аппаратах магнитной записи.

Цель изобретения - повьппение точности умножения частот).

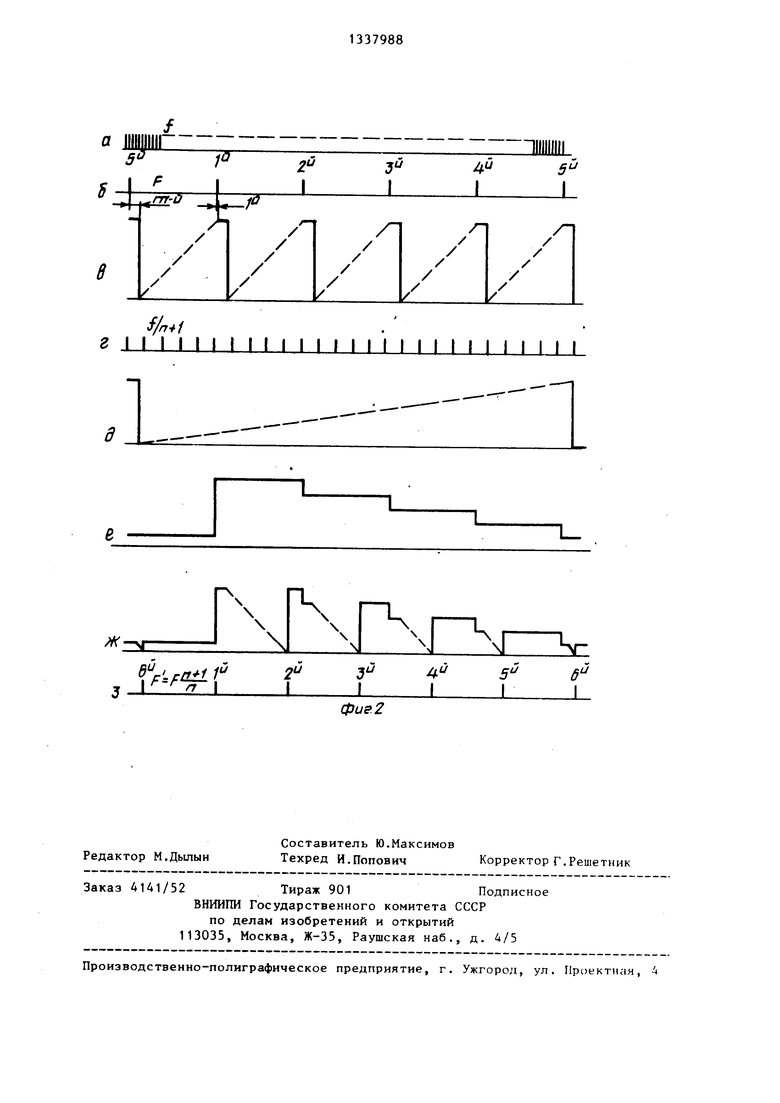

На фиг.1 представлена структурная электрическая схема дискретног о умножителя частоты; на фиг.211- - )

менные диаграммы, поясняющие его работу.

Дискретный умножитель частоты содержит опорный генератор 1, первый и второй делители 2 и 3 частоты, первый и второй счетчики 4 и 5, вычитающий счетчик 6, первый, второй и третий регистры 7-9 , регистр 10 сдпи- га, первый и второй сумматоры 11 и 12, первый и второй RS-триггеры 13 и 14, счетный триггер 15, первый, второй и третий формирователи 16-18 импульсов, первый, второй, третий, четвертый и пятый элементы И 19-23 и элемент 1ШИ 24.

Дискретный умножител) частоты работает следующим образом.

Периодическая последовательность импульсов с частотой fg (фиг.2а) с выхода опорного генератора 1 поступает на счетный вход первого делителя 2, коэф(})ициент деления равен п+ 1 (п О, целое число). Коэффициент деления второго делителя 3 равен п. С выхода лервЪго делителя 2 импульсы (фиг. 2 г) поступают на счетньп вход первого счетчика 4, а на счетные входы второго счетчи са 5 и вычитающего счетчика 6 через nepBbii i элемент И 19 поступают имлульсы с частопчи f . Измерение периода входного сигнала (фиг.25) осуществляется с помощью второго счетчика 5 (фиг.2е). Входной импульс поступает на информационн)Гй вход регистра 10, на первом выходе которого вырабатывается импульс, пос- тупающш на R-вход первого RS- . ригге- ра 13. На прямом выходе первого RS- триггера 13 устанавливается уровень О, закрывающий первый элемент И 19 На счетные входы второго счетчика 5 и вычитающего счетчика 6 прекращается поступление импульсов опорного генератора 1 . Одновременно осущестплястс-.я запись информации с выходов Brop jro счетчика 5 в первый или третий рег ис- тры 7 и 9 (в зависимости от состояния счетного триггера 15, прямой и инверсный выходы которого соединены с вхо8

дами соответственно третьего и четвертого элементов И 21 и 22) и запись информации с выходов второго сумматора 12 во второй регистр 8. С задержал /ч

кои на Г -- (т - целое чи.сло) на

втором выходе регистра 10 появляется импульс, КО1ГФЫЙ устанавливает в О

второй счетчик 5 и в 1 первый и

второй RS-триггеры 13 и 14. Результаты измерения длительности соседних периодов входного сигнала в виде двоичных кодов с выходов первого и третьего регистров 7 и 9 поступают на соответств тощие входы первого сумматора 11, на выходе которого значение двоичного кода имеет вид

20

N n. ,)

где Т; - длительность периода входного сигнала. С приходом п-го импульса на вход

ij дискретного умножителя частоты ва выходе второго формирователя 17 вырабатывается короткий импульс, который устанавливает первый делитель 2 в О, а на выходе третьего формироваQ теля 18 устанавливается уровень 1, который открывает пятый элемент И 23, и импульс с второго выхода регистра 10 поступает на вход установки нуля первого счетчика 4. Первый счетчик 4 устанавливается в О через каждые п периодов входного сигнала (фиг.23).

I

Двоичный код с выходов разрядов

первого сумматора 11 и двоичный код с инверсных выходов- разрядов первого счетчика 4 поступают на соответствующие входы второго сумматора 12, с выходов которого информаи.ия переписывается во второй регистр 8 (фиг.2Р).

Уровень О на управляющем входе иы- t

читающего счетчика 6 соотве ствует

режиму записи информации (из регистра 8), а уровень 1 соответствует режиму вычитания, т.е. до т-го импульса, вьоделенного регистром JO, вы- читающшЧ счетчик 6 находится в режиме записи кода (фиг. 2 ж), а с пр1гходом т-го импульса RS-триггер 14 устанавливается в 1 и переводит вычитающий счетчик 6 в режим вычитания. На счетный вход вычитающего счетчика 6 подается (с выхода первого элемента И 19) сигнал, в котором имеются паузы длительностью, равной интервалу между

О

5

31 3

первым и m-M имггу.пьсами, выделениями регистром 10.

Вычитаюппи счетчик 6 досчитывает до нуля и формирует на своем выходе импульс переноса, который через элемент ИЛИ 2.4 постунает на выход дискретного умножителя частоты, переключает второй RS-триггер 14 в нулевое состояние, а вычитающий счетчик 6 переводит в режим записи информации.Че рез элемент ИЛИ 24 на выход дискретного умножителя частоты проходит каждый первый импульс в пикле п, выделенный первым формирователем 16 импульсов. Таким образом, па выходе дис- кретного умножителя частоты форм1фу- ется периодическая последовательность импульсов (фиг.2з) с частотой следования. V -г -tJ Вы f п

При асимметрии входного сигнала, когда еще не формировался выходной импульс, а пришел следующий входной импульс, вычитающий счетчик 6 обнуляется входным импульсом, который про ходит через второй элемент И 20. Синхронизация дискретного умножителя частоты осуществляется путем обнуления второго делителя 3.

,-

Формула изобретения

Дискретный умножитель частоты, содержащий последовательно соединенные опорный генератор, первьй делитель частоты и первый счетчик, последовательно соединенные второй делитель частоты, первый формирователь импульсов, элемент ИЛИ, вт(1рой и третий формирователи импульсов, входы кото- рых соединены с соответствующими выходами второго делителя частоты, последовательно соед1П1енные первый RS- триггер и первый элемент И, последовательно соединенные второй RS-триг- гер и второй элемент И, третш, четвертый и пятый элементы И, о т л и - ч а ю щ и i с я .тем, что, с целью повышения точности умножения частоты, в пего введен),1 последовательно соединенные второй счетчик, первый регистр памяти, первый сумматор, второй сум3 3 7

-joн(5 ь

25

30

5 404550 9884

матор, второй регистр памяти и HI.IMH- таюииш счетчик, выход которого сс.ч ди- нен с К-входом второго КЯ-тригг( ра и с вторым входом Э1темента ИЛИ, счетный триггер, регистр сдвига и третш регистр памяти, информационные вход|л которого соединены с соответствующими выходами второго счетчика, а ВЫХОДР- третьего регистра памяти соединены с соответствующими входами первого сумматора, счетные входы второго счетчика и вычитающего счетчика объедине |ы и соединены с выходом первого элемента И, -.второй вход которого обт ед1шен с входом синхронизации регистра сдвига и соединен с выходом опорного генератора, первые входы третьего и четвертого элементов И объединены с входом записи второго регистра памяти и соединены с инверсным выходом первого RS-триггера, прямой и инверсн1,1й выходы счетного триггера соединены с вторыми входами соответственно третьего и четвертого элементов И, BI.IXO- ды которых соединеР1ы с входами записи соответственно первого и третьего регистров памяти, первый выход регистра сдвига соединен с R-входом nepBoi o RS-триггера, S-вход которого оГп.единен с S-входом второго RS-триггера, с первым входом пятого элемента И п с установочным входом второго счетчика и соединен с вторым выходом регистра сдвига, установоч)1ый вход первог о делителя частоты соединен с ВЕЛХОДОМ второго формирователя импульсов, выход третьего формирователя импульсов соединен с вторым входом пятого элемента И, выход кoтopo o сосдпнен с установочным входом первого счетчика, инверсные выходы разрядов первого счетчика соединены с соответствующими входами второго с мматора, выход второго RS-тр иггера соединен с управляющим входом вычитающего счетчика, вход установки нуля которого соединен с выходом второго элемента И, второй вход второго элемента И объединен с информационным входом регистра сдвига, со счетным входом счетного триггера и со счетным входом второго делителя частоты.

II

F7

1

2

f/n-fi

г I I I I I I i M I I I I I I I I I I I I I I I I I I

фиг 2

Редактор М.Дылын

Составитель Ю.Максимов

Техред И.Попович Корректор Г,Решетник

Заказ 4141/52Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

nillllllll

4 J

5 I

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты с дробным коэффициентом умножения | 1987 |

|

SU1492475A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Цифровое фазосдвигающее устройство | 1983 |

|

SU1081563A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Цифровое устройство для управления скоростью двигателя | 1984 |

|

SU1218367A1 |

| Помехоустойчивый цифровой фазометр | 1979 |

|

SU1002979A1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2016 |

|

RU2636750C1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2016 |

|

RU2639891C2 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

Изобретение относится к радиотехнике и связи. Цель изобретения - повышение точности умножения частоты. Умножитель содержит опорный г-р 1, делители 2 и 3 частоты, счетчики 4 и 5, вычитающий счетчик 6, регистры 7, 8 и 9 памяти, регистр 10 сдвига, сумматоры 11 и 12, RS-триггеры 13 и 14, счетный триггер 15, формирователи 16, 17 и 18 импульсов, эл-ты И 19, .20, 21, 22 и 23 иэл-т ИЛИ 24. Цель достигается введением счетчика 6, регистров 7, 8, 9 и 10, cyMMatopoB 11 и 12 и триггера 15, с помощью которых на выход умножителя проходит каждый первый импульс, вьщеленный формирователем 16, в цикле п и формируется периодическая последовательность импульсов с частотой следования Fj F(n+ 1)/n, где п и n 1 - коэффициенты деления делителей 3 и 2 соответственно. 2 ил. с СЛ оо оо со 00 00 ifitft

| Умножитель частоты | 1980 |

|

SU944097A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Импульсный умножитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU839036A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-15—Публикация

1985-08-19—Подача