Изобретение относится к импульсн технике и может быть использовано в вычислительных устройствах в качестве полного комбинационного сумматор

Целью изобретения является увеличение надежности путем упрощения.

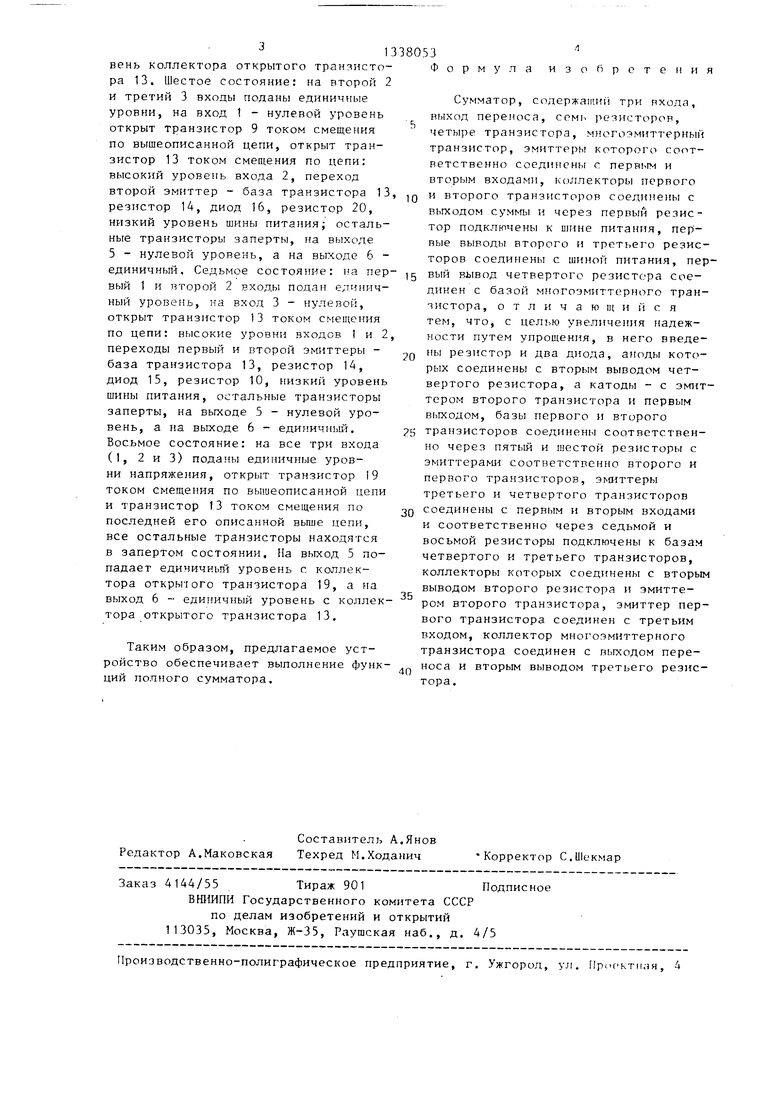

На чертеже представлена принципиальная схема сумматора.

Сумматор содержит первый 1, втор 2 и третий 3 входы, шину 4 питания, выход 5 суммы, выход 6 переноса, певый промежуточный выход 7, третий 8 и четвертый 9 транзисторы, соединенные эмиттерами с входами 1 и 2, коллекторами - с выходом 7 и через второй резистор 10 - с шиной питания 4 а базами - соответственно через восмой 11 и седьмой 12 резисторы - с входами 2 и 1, вторая дополнительна схема соединена своим первым входом с выходом 7, вторым входом - с третьим входом 3 и выходом - с выходом 5 суммы, эмиттеры многоэмиттер- ного транзистора 13 подключены к первому 1 и второму 2 входам, база чере.з четвертый резистор 14 - к анодам первого 15 и второго 16 диодов, катоды которых соединены с выходами 7 и 5 соответственно, а коллектором с выходом 6 и через третий резистор 17 - с шиной 4 питания, коллекторы второго 18 и первого 19 транзисторо соединены с выходом 5 и через первы резистор 20 - с шиной 4, их эмиттеры - с катодами диодов 15 16, с вы

ходом 7 и входом 3 и шестой резисторы 21, транзисторов 19 и 18.

Сумматор работает следующим разом.

через пятый и 22 - с базами

обЕсли за единичный уровень взять высокий уровень коллекторного напряжения открытого транзистора, а за нулевой.- низкий уровень коллекторного напряжения запертого транзистора, близкого к напряжению шины питания, то в зависимости от комбинаци этих напряжений на входах 1-3 можно выделить восемь рабочих состояний сумматора. Первое состояние: на все три входа поданы нулевые уровни, на выходы 5 и 6 попадают нулевые уров- ни, так как все транзисторы находятся в запертом состоянии. Второе состояние: на первый вход 1 подан еди- ничньй уровень, на входы 2 и 3 - нулевой, транзистор 8 открыт и удерживается в открытом состоянии током

5

22,

0

5

0

смещения по цепи: высокий уровень входа 1, переход эмиттер - база транзистора 8, резистор 11, низкий уровень входа 2, открыт транзистор 18 и удерживается током смещения по цепи: высокий уровень коллектора открытого транзистора 8, переход эмиттер - база транзистора 18, резистор низкий уровень входа 3, остальные транзисторы находятся в запертом состоянии, высокий единичный уровень напряжения с коллекторного перехода открытого транзистора 18 попадает на выход 5, на выходе 6 - нулевой уровень. Третье состояние: на второй вход 2 подан единичный уровень, на входы 1 и 3 - нулевой, открыт транзистор 9 и удерживается током по цепи: высокий уровень входа 2, переход эмиттер - база транзистора 9, резистор 12, низкий уровень входа 1, открыт транзистор 18 и удерживается в открытом состоянии током смещения по вьш1еописанной цепи, с его коллектора единичный уровень попадает на вход 5, остальные транзисторы находятся в запертом состоянии, на входе 6 нулевой уровень. Четвертое состояние: на третий вход 3 подан единичный уровень, на входы 1 и 2 - нулевой, открыт транзистор 19 и удерживается в открытом состоянии током по цепи: высокий уровень входа 3, переход эмиттер - база транзистора 19, резистор 21, резистор 10; низкий уровень шины питания, единичный уровень с коллектора открытого транзистора 19 попадает на выход 5. Остальные транзисторы заперты, так как напряжения на их базах и эмиттерах равны и низки по уровню, на выходе 6 - нулевой уровень. Пятое состояние: на первый 1 и третий 3 входы подан единичный уровень, на вход 2 - нулевой, открыт транзистор 8 током смещения по вьш1еописанной цепи, открыт транзистор 13 и удерживается в открытом состоянии током смещения по цепи: высокий уровень напряжения входа 1, переход первый эмиттер - база транзистора 13, резистор 14, диод 16, резистор 20, низкий уровень шины питания. Транзисторы 18 и 19 заперты, так как их эмиттеры и базы находятся 5 на одном единичном уровне напряжений, транзистор 9 заперт высоким уровнем входа 1, на выход 5 попадает нулевой уровень шины питания через резистор 20, на выход 6 - единичный уро5

0

5

0

вень коллектора открытого транзистора 13. Шестое состояние: на второй 2 и третий 3 входы поданы единичные уровни, на вход 1 - нулевой уровень открыт транзистор 9 током смещения по вышеописанной цепи, открыт транзистор 13 током смещения по цепи: высокий уровень входа 2, переход второй эмиттер - база транзистора 13 резистор 14, диод 16, резистор 20, низкий уровень шины питания; остальные транзисторы заперты, па выходе 5 - нулевой уровень, а на выходе 6 - единичньм. Седьмое состояние: на пер вый 1 и второй 2 входы подан единичный уровень, на вход 3 - нулевой, открыт транзистор 13 током смещения по цепи: высокие уровни входов I и 2 переходы первый и второй эмиттеры - база транзистора 13, резистор 14, диод 15, резистор 10, Ь изкий уровень шины питания, остальные транзисторы заперты, на выходе 5 - нулевой уровень, а на выходе 6 - единичный. Восьмое состояние: на все три входа (1, 2 и 3) поданы единичные уровни напряжения, открыт транзистор 19 током смещения по вышеописанной цепи и транзистор 13 током смещения по последней его описанной выше цепи, все остальные транзисторы находятся в запертом состоянии, 1а выход 5 попадает единичный уровень с коллектора откры 1 ого транзистора 19, а на выход 6 - единичный уровень с коллектора открытого транзистора 13.

Таким образом, предлагаемое устройство обеспечивает выполнение функций полного сумматора.

Редактор А.Маковская

Составитель А.Янов Техред М.Ходанич

Ко По

4144/55 Тираж 901

ВШ1ИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Ирооктиля, 4

0

g

0

5

0

5

0

Формула изобретения

Сумматор, содержащий три , выход переноса, ceMi резисторов, четыре транзистора, многоэмитт ерный транзистор, эмиттеры которого соответственно соединены с перв1 гм и вторым входами, коллекторы первого и второго транзисторов соединены с выходом суммы и через первый резистор подключены к шине питания, первые выводы второго и третьего резисторов соединены с шиной питания, первый вывод четвертого резистора соединен с базой многоэмиттерного транзистора, отличают и и с я тем, что, с целью увеличе1П1я надежности путем упрощения, в него введены резистор и два диода, аноды которых соединены с вторым выводом четвертого резистора, а катоды - с эмиттером второго транзистора и первым выходом, базы первого и второго транзисторов соединены соответственно через пятый и шестой резисторы с эмиттераг ш соответственно второго и первого транзисторов, эьшттеры третьего и четвертого транзисторов соединены с первым и вторым входами и соответственно через седьмой и восьмой резисторы подключены к базам четвертого и третьего транзисторов, коллекторы которых соединены с вторым выводом второго резистора и эмиттером второго транзистора, эмиттер первого транзистора соединен с третьим входом, коллектор многоэмиттерного транзистора соединен с выходом переноса и вторым выводом третьего резистора.

Корректор С.Шекмар Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Дешифратор строк для запоминающего устройства | 1985 |

|

SU1285531A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Универсальный Д(Т)-триггер | 1988 |

|

SU1561200A1 |

| Одновибратор | 1978 |

|

SU733088A1 |

| Триггер | 1986 |

|

SU1325669A1 |

| Однофазный D-триггер | 1988 |

|

SU1647855A1 |

| Ассоциативный запоминающий элемент | 1983 |

|

SU1130900A1 |

| Пороговый логический элемент | 1975 |

|

SU600711A1 |

Изобретение относится к импульсной технике и может быть использовано в вычислительных устройствах в качестве полного комбинационного сумматора для сложения сигналов - логического О и Г Изобретение обеспечивает повышение надежности устройства путем его упрощения. Устройство содержит входы 1-3, шину 4 питания, выход 5 суммы, выход 6 переноса, промежуточный выход 7, транзисторы 8 и 9, резисторы, многоэмиттерный транзистор 13, диоды 15 и 16, транзисторы 18 и 1,9. Введение в устройство третьего входа 3 и выходов 5 и 6 полной суммы и переноса позволило расширить функциональные возможности устройства по сравнению с прототипом. 1 ил. 00 00 00 о ел 00

| Будинский Я | |||

| Транзисторные переключающие схемы | |||

| М.: Связь, 1965, с | |||

| Кузнечный горн | 1921 |

|

SU215A1 |

| Способ обделки поверхностей приборов отопления с целью увеличения теплоотдачи | 1919 |

|

SU135A1 |

| Алексенко А.Г., Шагурин Н.И | |||

| Микросхемотехника | |||

| М.: Радио и связь, 1982, с.148, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-15—Публикация

1986-03-25—Подача