112

Изобретение относится к вычисли- те, технике и может быть использовано при построении интегральных микросхем памяти.

Цель изобретения - расширение области применения дешифратора за счет обеспечения возможности использования при изменении питающего напряжения.

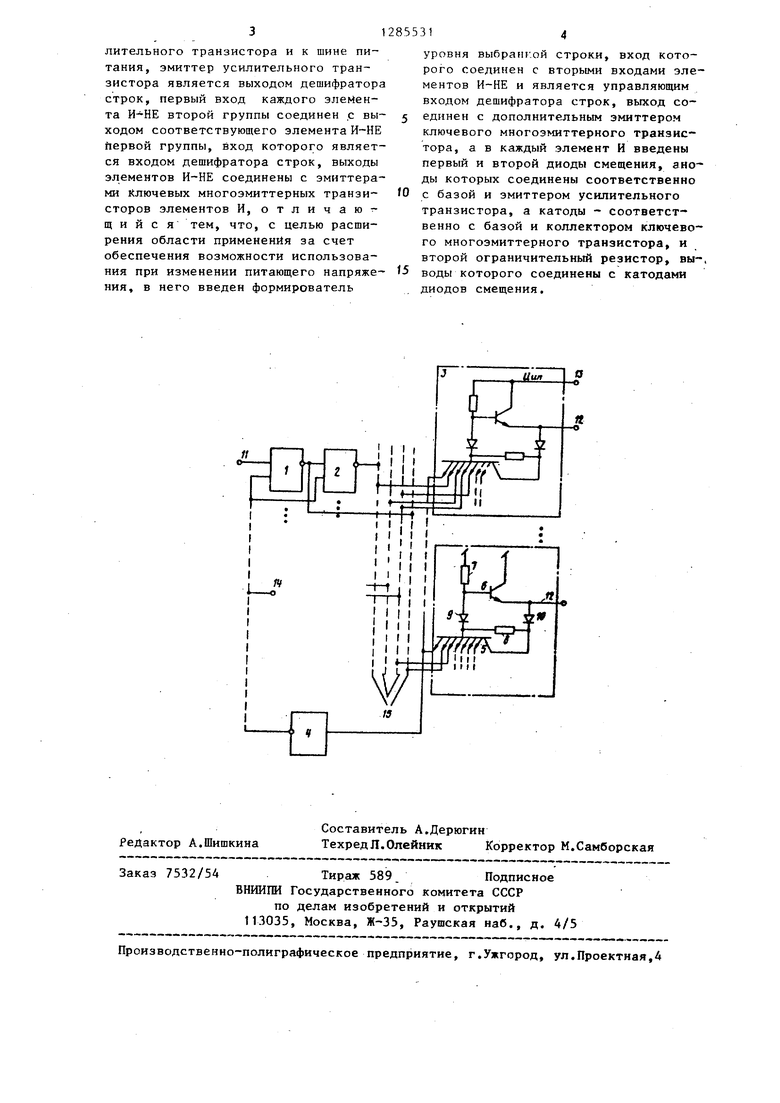

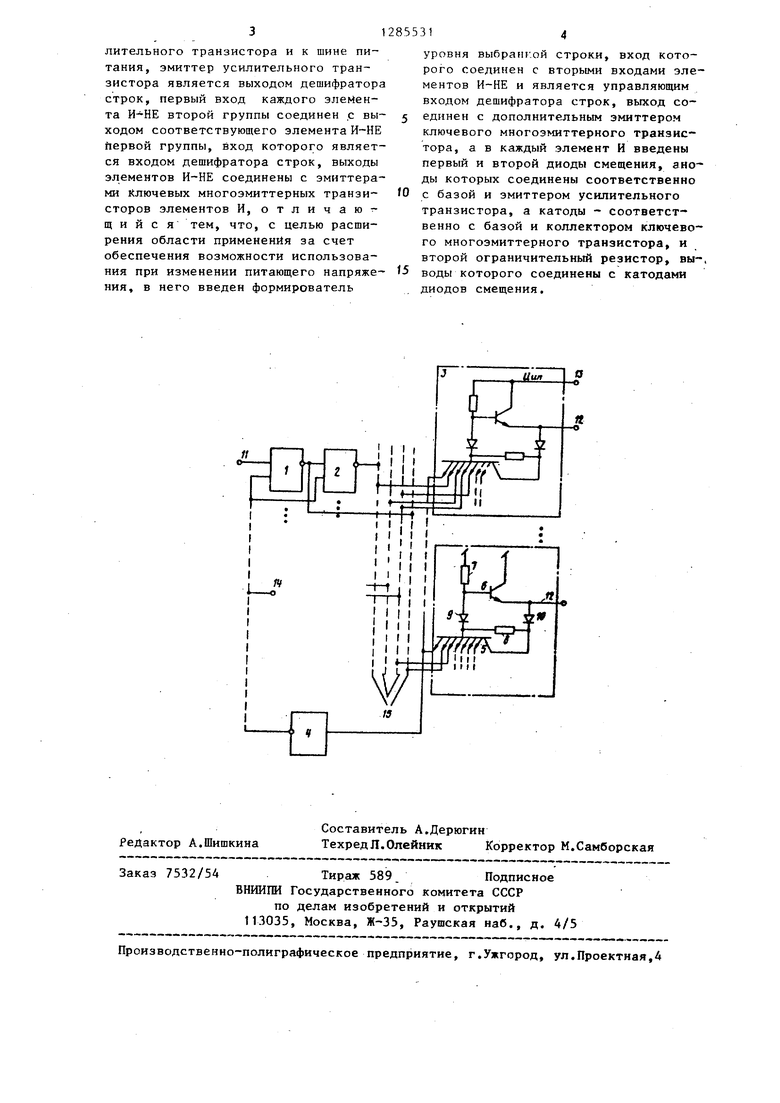

На чертеже изображена схема де- шифратора.

Дешифратор содержит первую 1 и вторую 2 группы элементов И-НЕ, элементы И 3, формирователь 4 уровня выбранной строки. Каждый элемент И состоит из ключевого многоэмиттерно- го транзистора 5, усилительного транзистора 6, первого 7 и второго 8 ограничительных резисторов, первого 9 и второго 10 диодов смещения. На схеме показаны также входы 11 И выходы 12 дешифратора, шина 13 питания, управляюш;ий вход 14, шины 15 дешифрации.

Дешифратор строк для запоминающего устройства работает следующим образом.

Если на входе 14 уровень напряжения равен уровню логического нуля.

то элементы И-НЕ 1 и 2 выключены.

выключен также формирователь 4 уровня выбранной строки, и напряжение на всех шинах 15 дешифрации соответствует уровню выходного напряжения логической единицы элементов И-НЕ 1 и 2. При этом напряжение на базе транзистора 6 равно , а напряжение на выходах 12 равно Uu.n U3gT-g , где и - падение напряжения на переходе эмиттер - база транзистора 6 Если на вход 14 подан уровень логической единицы, то в соответствии с уровнями напряжения на адресных входах 11 происходит установка элементов И-НЕ 1 и 2 в закрытое или открытое состояние, причем если первый инвертор открыт, то второй закрыт, и наоборот. Следовательно, на одних шинах 15 дешифрации будет низкий уровень напряжений, на других высокий. Формирователь 4 обеспечивает на подключенных к нему эмиттерах транзисторов 5 некоторое постоянное напряжение Uc,, относительно шины нулевого потенциала. При этом возможны два режима работы:

1. Строка выбрана. В этом режиме на всех эмиттерах транзистора 5

-

8553

5 О

25

30

35 .

45

50

55

12

высокий уровень напряжения (напря- жение на них выше напряжения на выходе формирователя 4), При этом напряжение на базе транзистора 6 в установившемся режиму равно

и атб и.+и,8т5 +UM

где Uq, - напряжение на выходе

формирователя 4, падение напряжения на переходе база - эмиттер транзистора 5, 1 - падение напряжения на

диоде 9,

Напряжение на выходе 12 при этом равн.о

и/7 U5,.-U,6.« . U,. Строка не выбрана. В этом

режиме хотя бы в одном из эмиттеров транзистора 5 низкий уровень напряжения (ниже выходного напряжения формирователя 4) за счет протекания тока по цепи: + , резистор 7, диод 9, резистор 8, коллектор - эмиттер транзистора 5, открытые выходы . элементов , шина нулевого потенциала. Установившееся значение напряжения на базе транзистора 6 равно

Usu U%U5, ,

где и - уровень напряжения на выходе элемента И-НЕ во включенном состоянии.

I

Напряжение на выходе 12 при этом

равно

иГ, Ч тб -и.Ьтб .

Из рассмотрения работы дешифратора строки для запоминающего уст- i, ройства вытекает, что кратковремен- . ные и быстрые изменения напряжения питания в режиме Строка выбрана равны

Us.b иф,+изЬт5 и.. и,2и,й . и не могут оказать влияния на напряжение на выходе 12 и поэтому не могут быть причиной ненадежной работы микросхемы памяти.

Формула изобретения

Дешифратор строк для«запоминающего устройства, содержащий первую и вторую группы элементов И-НЕ, элементы И, каждый из которых состоит из ключевого многоэмиттерного транзистора, усилительного транзистора и первого ограничительного резистора, один вывод которого подключен к базе, а ДРУГОЙ - к коллектору уси3

лительного транзистора и к шине питания, эмиттер усилительного транзистора является выходом дешифратор строк, первый вход каждого элемента второй группы соединен с выходом соответствующего элемента И-НЕ первой группы, вход которого является входом дешифратора строк, выходы элементов И-НЕ соединены с эмиттерами Ключевых многоэмиттерных транзисторов элементов И, отличаю - щ и и с я тем, что, с целью расширения области применения за счет обеспечения возможности использования при изменении питающего напряжения, в него введен формирователь

уровня выбрар1г.ой строки, вход которого соединен с вторыми входами элементов И-НЕ и является управляющим входом дешифратора строк, выход соединен с дополнительным эмиттером ключевого многоэмиттерного транзистора, а в каждый элемент И введены первый и второй диоды смещения, аноды которых соединены соответственно с базой и эмиттером усилительного транзистора, а катоды - соответственно с базой и коллектором ключевого многоэмиттерного транзистора, и второй ограничительный резистор, выводы которого соединены с катодами диодов смещения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Устройство для ввода информации | 1982 |

|

SU1205136A1 |

| Формирователь сигналов считывания | 1984 |

|

SU1238152A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Интегральная логическая схема | 1979 |

|

SU1001480A1 |

| Интегральная логическая схема | 1979 |

|

SU860314A1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

| Анализатор уровня напряжения | 1979 |

|

SU792163A1 |

| Преобразователь сигналов для усилителя считывания | 1984 |

|

SU1244716A1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении интегральных микросхем памяти. Целью изобретения является расширение области применения дешифратора за счет возможности использования его при изменении питающего напряжения. Для достижения этой цели в дешифратор введен формирователь уровня выбранной строки, а в каждый элемент И дешифратора - ограничительный резистор и два диода смещения. При этом изменения напряжения питания, связанные с выборкой микросхем памяти,не будут влиять на значение напряжения на выходах дешифратора и не могут быть причиной ненадежной работы микросхе- мы памяти. 1 ил. с fS го 00 сд СП со

ft

Редактор А.Шишкина

Составитель А.Дерюгин

Техред Л. Олейник Корректор М.Самборская

Заказ 7532/54Тираж 589. Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Запоминающее устройство | 1983 |

|

SU1171849A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| СПОСОБ УПРАВЛЕНИЯ СВЯЗЬЮ, УСТРОЙСТВО СВЯЗИ И ПРОГРАММА | 2010 |

|

RU2534736C2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1987-01-23—Публикация

1985-03-19—Подача