113

Изобретение относится к автоматике и вычислительной технике, может быть использовано для построения различных устройств переработки дискретной информации и является усовершенствованием изобретения по авт. св. СССР № 1034188.

Целью изобретения является повышение быстродействия порогового эле- мента.

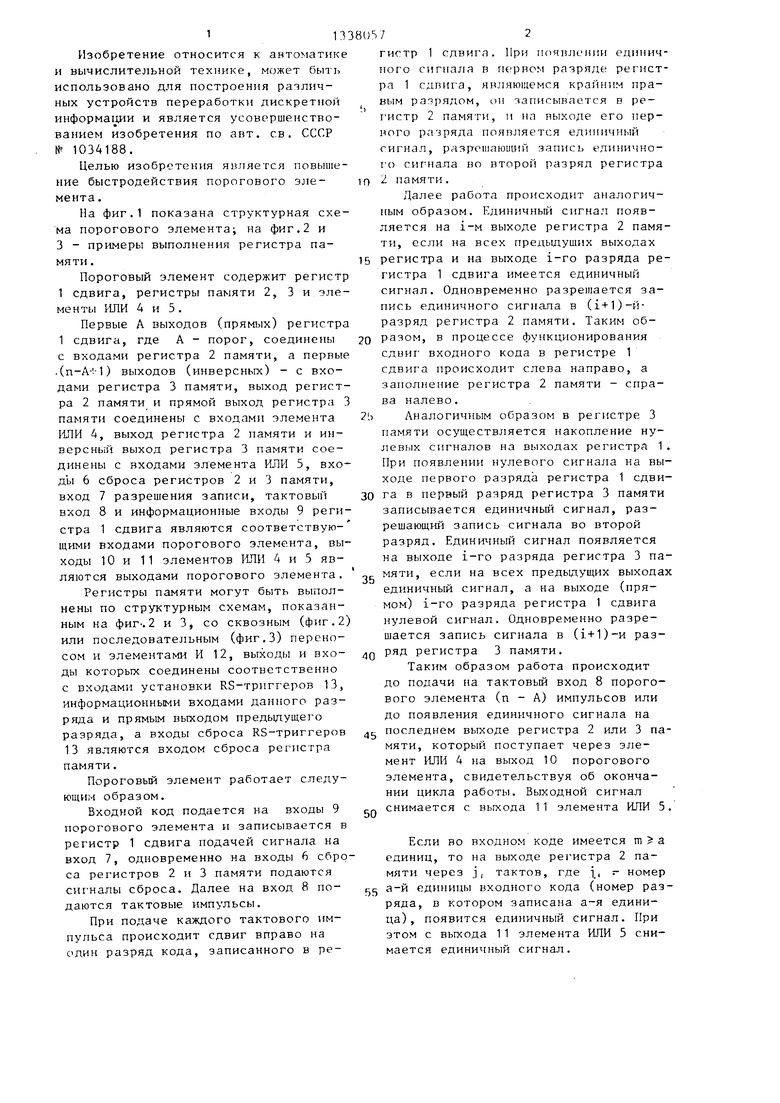

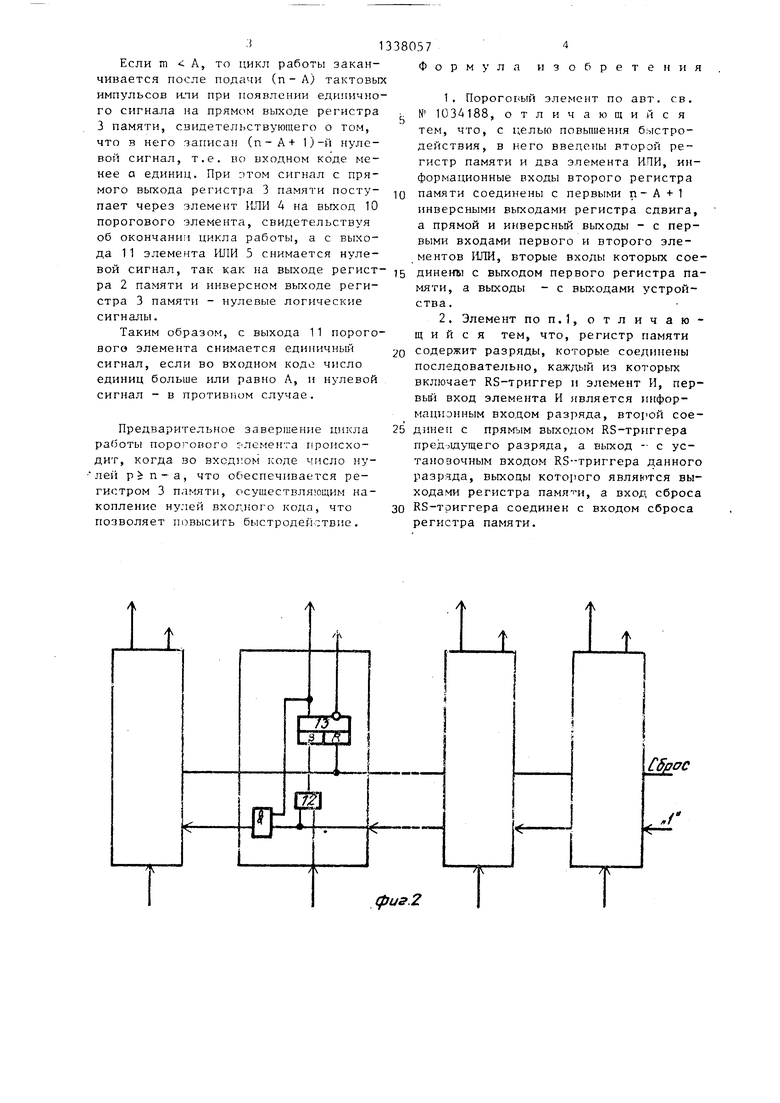

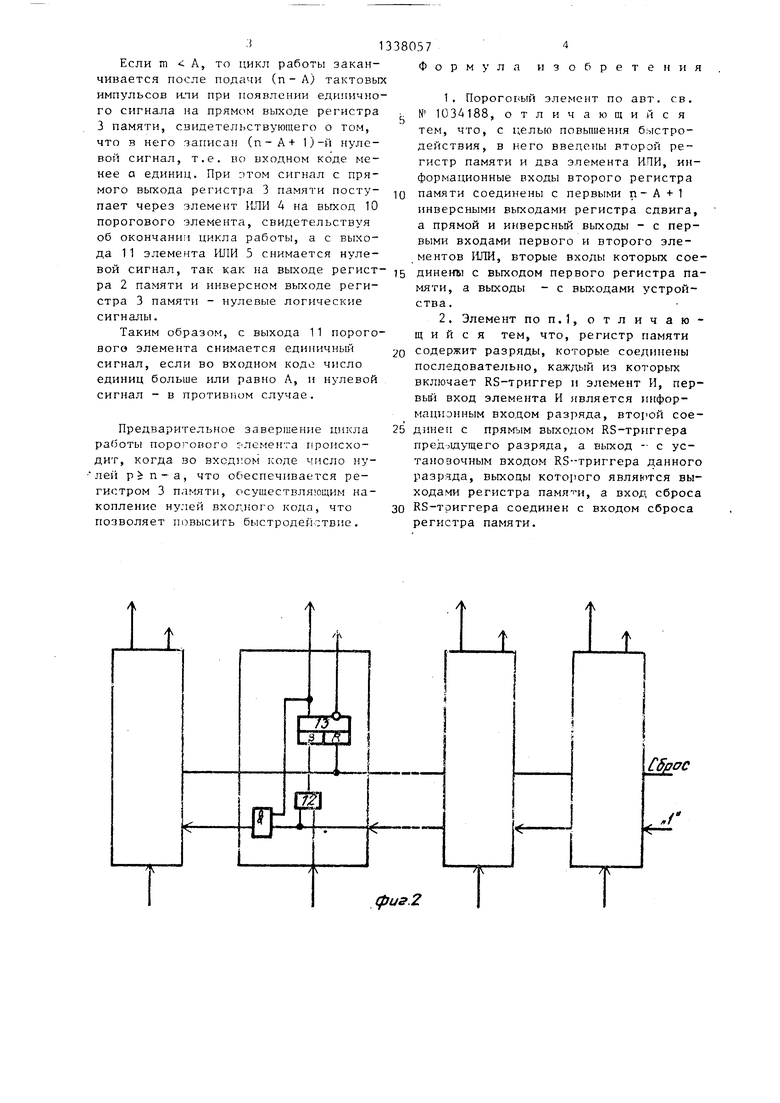

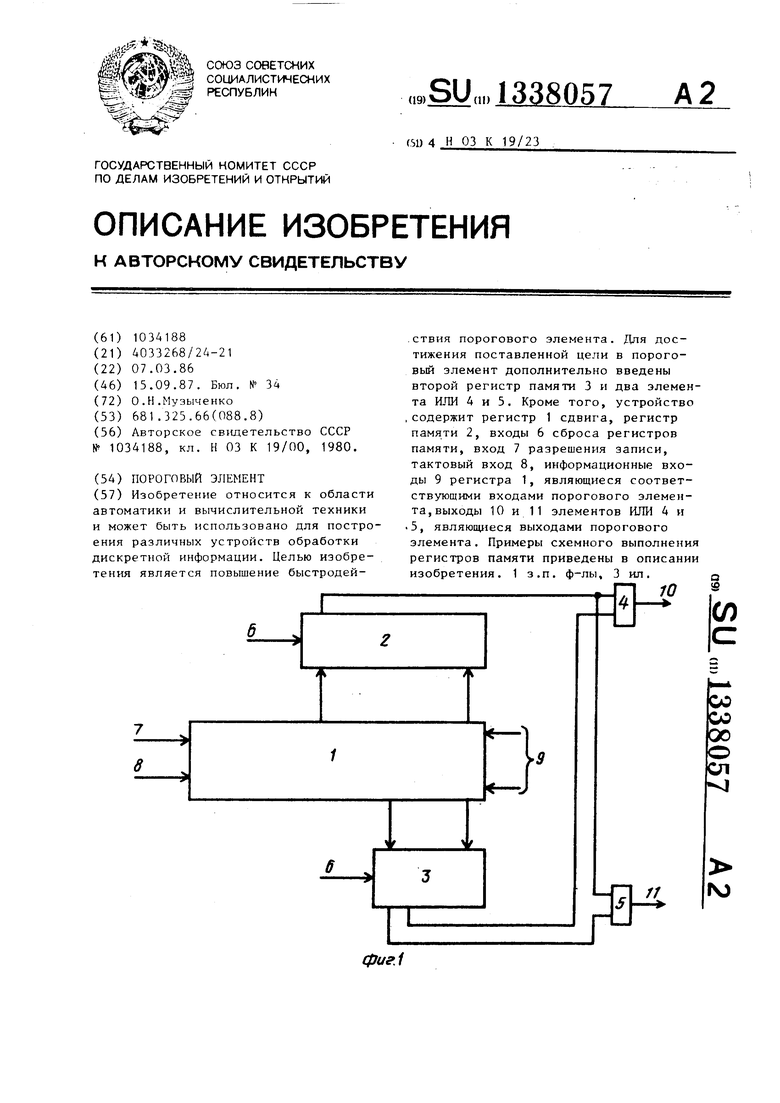

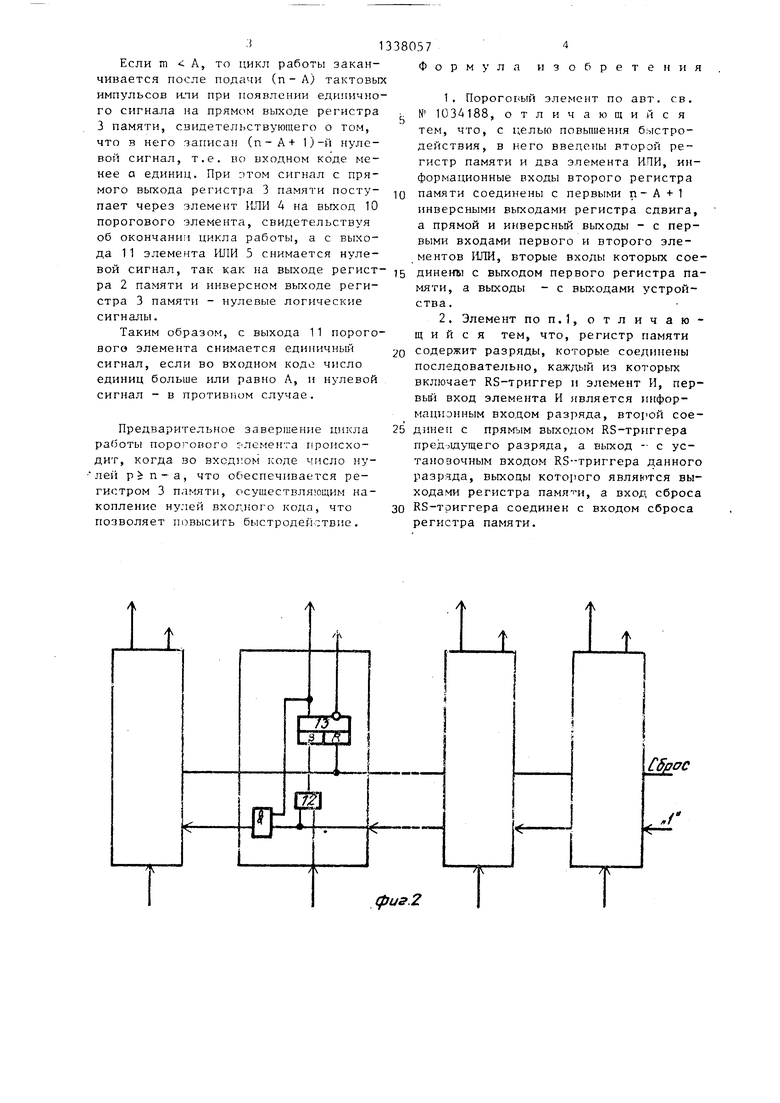

Иа фиг.1 показана структурная схема порогового элемента; на фиг.2 и 3 - примеры выполнения регистра памяти.

Пороговый элемент содержит регистр 1 сдвига, регистры памяти 2, 3 и элементы 1-ШИ 4 и 5.

Первые А выходов (прямых) регистра 1 сдвига, где А - порог, соединены с входами регистра 2 памяти, а первые .(п-А- .-1) выходов (инверсных) - с входами регистра 3 памяти, выход регистра 2 памяти и прямой выход регистра 3 памяти соединены с входами элемента ИЛИ 4, выход регистра 2 памяти и ин- версньй выход регистра 3 памяти соединены с входами элемента ИЛИ 5, входы 6 сброса регистров 2 и 3 памяти, вход 7 разрешения записи, тактовый вход 8 и информационные входы 9 регистра 1 сдвига являются соответствующими входами порогового элемента, выходы 10 и 11 элементов РШИ 4 и 5 являются выходами порогового элемента.

Регистры памяти могут быть выполнены по структурным схемам, показанным на фиг-. 2 и 3, со сквозным (фиг. 2) или последовательным (фиг.З) переносом и элементами И 12, выходы и вхо- ды которых соединены соответственно с входами установки RS-триггеров 13, информационными входами данного разряда и прямым выходом предыдущего разряда, а входы сброса RS-триггеров 13 являются входом сброса регистра памяти.

Пороговый элемент работает следу- ющи;-1 образом.

Входной код подается на входы 9 порогового элемента и записывается в регистр 1 сдвига подачей сигнала на вход 7, одновременно на входы 6 сброса регистров 2 и 3 памяти подаются сигналы сброса. Далее на вход 8 по- даются тактовые импульсы.

При подаче каждого тактового импульса происходит сдвиг вправо на один разряд кода, записанного в ре72

гистр 1 сдвига. При почвлсчши единичного сигнала в первом разряде регистра 1 сдвига, япляю1 1емся крайним правым разрядом, он записывается в ре- г истр 2 памяти, и на выходе его первого разряда появляется единичный сигнал, разрешающий запись единично- I o сигнала во второй разряд регистра 2 памяти.

Далее работа происходит аналогич ным образом. Единичный сигнал появляется на i-M выходе регистра 2 памяти, если на всех предыдущих выходах регистра и на выходе i-ro разряда регистра 1 сдвига имеется единичный сигнал. Одновременно разрешается запись единичного сигнала в (1+1)-й- разряд регистра 2 памяти. Таким образом, в процессе функционирования СДВИГ входного кода в регистре 1 сдвига происходит слева направо, а заполнение регистра 2 памяти - справа налево.

Аналогичным образом в регистре 3 памяти осуществляется накопление нулевых сигналов на выходах регистра 1. При появлении нулевого сигнала на выходе первого разряда регистра 1 сдвига в первый разряд регистра 3 памяти записывается единичный сигнал, разрешающий запись сигнала во второй разряд. Единичный сигнал появляется на выходе i-ro разряда регистра 3 памяти, если на всех предыдущих выходах единичный сигнал, а на выходе (прямом) i-ro разряда регистра 1 сдвига нулевой сигнал. Одновременно разрешается запись сигнала в (i+1)-H разряд регистра 3 памяти.

Таким образом работа происходит до подачи на тактовый вход 8 порогового элемента (п - А) импульсов или до появления единичного сигнала на последнем выходе регистра 2 или 3 памяти, который поступает через элемент ИЛИ 4 на выход 10 порогового элемента, свидетельствуя об окончании цикла работы. Выходной сигнал снимается с выхода 11 элемента ИЛИ 5.

Если во входном коде имеется m а единиц, то на выходе регистра 2 памяти через JI тактов, где |, :- номер а-й единицы входного кода (номер разряда, в котором записана а-я единица), появится единичный сигнал. При этом с выхода 11 элемента ИЛИ 5 снимается единичный сигнал.

Если m А, то цикл работы заканчивается после подачи (п - Л) тактовых импульсов или при появлении единичного сигнала на прямом выходе регистра 3 памяти, снидетельствующего о том, что в него записан (п-А+ 1)-и нулевой сигнал, т.е. во входном коде менее а единиц. При этом сигнал с прямого выхода регистра 3 памяти поступает через элемент ИЛР 4 на выход 10 порогового элемента, свидетельствуя об окончани пикла работы, а с выхода 11 элемента ИЛИ 5 снимается нулевой сигнал, так как на выходе регист- g динены с выходом первого регистра пара 2 памяти и инверсном выходе регистра 3 памяти - нулевые логические сигналы.

Таким образом, с выхода 11 порогового элемента снимается единичный сигнал, если во входном кодо число единиц больше или равно А, и нулевой сигнал - в противном случае.

Предварительное завершение цикла работы порогового з-лемента происходит, когда во вхсд1;ом коде число ну- лей pi п -а, что обеспечивается регистром 3 памяти, осуществляющим накопление нулей кода, что позволяет повысить быстродействие.

мяти, а выходы - с выходами устройства.

2. Элемент поп.1, отличающийся тем, что, регистр памяти

20 содержит разряды, которые соединены последовательно, каждый из которых включает RS-триггер и элемент И, пер- Bbrfi вход элемента И является информационным входом разряда, второй сое25 динеп с пряьгогм выходом RS-триггера пред-одущего разряда, а выход - с установочным входом КЗ-триггера данного разряда, выходы которого являются вы- хода.ми регистра , а вход сброса

30 RS-триггера соединен с входом сброса регистра памяти.

Формула изобретения

1. Пороговый элемент по авт. св. № 1034188, о тл и ч а ющий с я тем, что, с целью повьппения быстродействия, в него введены второй регистр памяти и два элемента ИЛИ, информационные входы второго регистра памяти соединены с первыми п- А +1 инверсными выходами регистра сдвига, а прямой и инверсный выходы - с первыми входами первого и второго элементов ИЛИ, вторые входы которых соемяти, а выходы - с выходами устройства.

2. Элемент поп.1, отличающийся тем, что, регистр памяти

содержит разряды, которые соединены последовательно, каждый из которых включает RS-триггер и элемент И, пер- Bbrfi вход элемента И является информационным входом разряда, второй соединеп с пряьгогм выходом RS-триггера пред-одущего разряда, а выход - с установочным входом КЗ-триггера данного разряда, выходы которого являются вы- хода.ми регистра , а вход сброса

RS-триггера соединен с входом сброса регистра памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый элемент | 1986 |

|

SU1368978A2 |

| Пороговый элемент (его варианты) | 1980 |

|

SU1034188A1 |

| Сумматор @ частотно-импульсных сигналов | 1982 |

|

SU1156068A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Устройство для приема и передачи информации | 1988 |

|

SU1536422A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для построения различных устройств обработки дискретной информации. Целью изобретения является повышение быстродей8 .ствия порогового элемента. Для достижения поставленной цели в пороговый элемент дополнительно введены второй регистр памяти 3 и два элемента ИЛИ А и 5. Кроме того, устройство ,содержит регистр 1 сдвига, регистр памяти 2, входы 6 сброса регистров памяти, вход 7 разрешения записи, тактовый вход 8, информационные входы 9 регистра 1, являющиеся соответствующими входами порогового элемента,выходы 10 и 11 элементов ИЛИ 4 и 5, являющиеся выходами порогового элемента. Примеры схемного выполнения регистров памяти приведены в описании изобретения. 1 з.п. ф-лы, 3 ил. ГО . п да- (Л 00 оо 00 СП 6 // N) фигА

С5ррс

,1

фиг.2

Редактор А.Маковская

Составитель 0.Скворцов Техред М.Ходакич.

4144/55

Тираж 901 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Про изводственно-полиграфическое предприятие, г. Ужгород, ул, Проектная, 4

(рие.З

Корректор С.Шекмар

Подписное

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-15—Публикация

1986-03-07—Подача