«L

СЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый элемент (его варианты) | 1980 |

|

SU1034188A1 |

| Устройство параллельно-последовательного поиска и замены вхождений в обрабатываемых словах | 2022 |

|

RU2793554C1 |

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде | 1982 |

|

SU1096651A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| УСТРОЙСТВО СОРТИРОВКИ ИНФОРМАЦИИ МЕТОДОМ ДЕШИФРАЦИИ ДАННЫХ | 2006 |

|

RU2319197C1 |

| УСТРОЙСТВО СОРТИРОВКИ ИНФОРМАЦИИ МЕТОДОМ ПРЕОБРАЗОВАНИЯ ДАННЫХ В АДРЕС | 2008 |

|

RU2382396C2 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| Устройство для контроля распределителя | 1983 |

|

SU1128260A2 |

| Пороговый элемент | 1986 |

|

SU1338057A2 |

Изобретение может быть использовано для построения устройств переработки дискретной информации. Пороговый элемент содержит регистр 1 сдвига, регистр 2 памяти и блок 4 контроля обнуления. Введение элемента И 6, регистра 3 памяти, блока 5 контроля обнуления и элементов ИПИ 7 и 8 повьшает быстродействие устройства. 1 табл., 2 ил.

/

/ .

р

8

11

Фи&1

Изобретение относится к автоматике и вычислительной технике, может быть использовано для построения различных устройств переработки дискретной информации и является усовершенствок

ванием известного порогового элемента по авт. св. № 1034188.

Цель изобретения - повышение быстродействия порогового элемента.

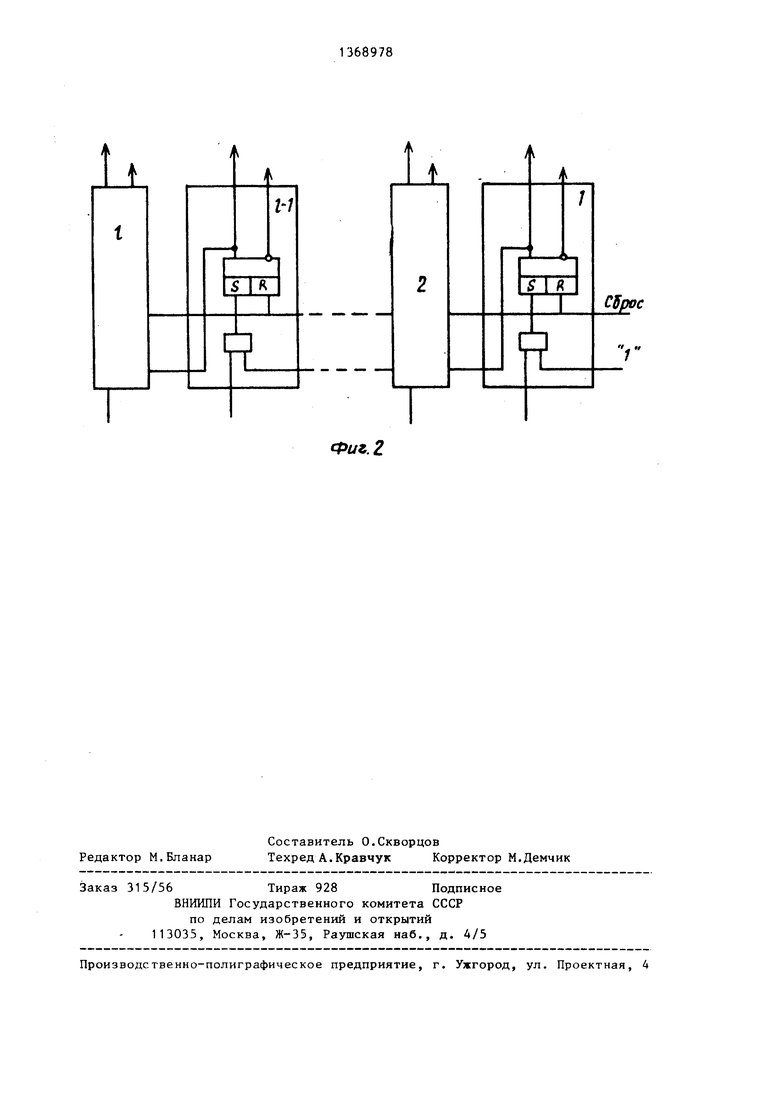

На фиг.1 изображена структурная схема порогового элемента, на фиг.2- структурная схема регистра памяти.

Пороговьм элемент содержит регистр 1 сдвига, регистры 2 и 3 памяти, блоки 4 и 5 контроля обнуления, элемент И 6, элементы ИЛИ 7 и 8. Информационные входы 9 регистра сдвига соединены с информационными входами порогового элемента. Первые а выходов регистра 1 сдвига (прямых) соединены с входами регистра 2 памяти (первым выходом регистра 1 сдвига является выход его крайнего правого разряда), а остальные (п-а) выходов - с входами блока 4 контроля обнуления, первые (п-а+1) выходов (инверсных) регистра 1 сдвига соединены с входами регистра 3 памяти, а остальные (а-1) выходов - с входами блока 5 контроля обнуления. Выходы последних разрядов стров 2 и 3 памяти и выходы блоков 4 и 5 контроля обнуления соединены с входами элемента ИЛИ 7, выход 10 которого соединен с выходом порогового

разряда регистра 3 памяти и выход блока 5 контроля обнуления соединены с входами элемента И 6, выход которого, а также выход последнего разряда регистра 2 памяти соединены с входами элемента ИЛИ 8, выход 11 которого соединен с выходом порогового элемента. Вход 12 разрешения записи регистра 1 сдвига соединен с входами сброса регистров 2 и 3 памяти и входом порогового элемента, тактовый вход регистра 1 сдвига соединен с тактовым входом 13 порогового элемента.

Регистры 2 и 3 памяти могут быть выполнены как в известном устройстве либо в виде последовательно соединенных разрядов, каждый из которых содержит RS-триггер и элемент И (фиг.2).

Блок 4 контроля обнуления может быть выполнен в виде элемента И с прямыми 1входами, если он соединен с

6

g

5

0

0

35

40

45

50

55

инверсными выходами регистра 1 сдвига, и в виде элемента И с инверсными входами, если он соединен с йрямыми выходами регистра 1 сдвига.

Блок 5 контроля обнуления может быть выполнен в виде элемента И с прямыми входами, если он соединен с прямыми выходами регистра 1 сдвига, и в виде элемента И с инверсными входами, если он соединен с инверсными выходами регистра 1 сдвига.

Пороговьй элемент функционирует следующим образом.

На вход 12 устройства подается импульс запуска, при поступлении которого происходит запись в регистр 1 сдвига входного кода, поданного на входы 9 порогового элемента, а также сброс регистров 2 и 3 памяти. Далее на вход 13 порогового элемента подаются тактовые импульсы.

При подаче каждого тактового импульса происходит сдвиг вправо на один разряд кода, записанного в регистр 1 сдвига. При появлении единичного сигнала в первом разряде регистра 1 сдвига, являющемся крайним правым разрядом, он записьшается в регистр 2 памяти и на выходе его первого разряда появляется единичный сигнал, разрешающий запись единичного сигнала во второй разряд регистра 2 памяти. Далее работа происходит аналогичным образом. Единичньй сигнал появляется на i-м выходе регистра 2 памяти, если на всех предыдущих выходах регистра имеется единичный сигнал и на выходе i-ro разряда регистра 1 сдвига также единичный сигнал. Одновременно разрешается запись единичного сигнала в (1+1)-й разряд регистра 2 памяти. Таким образом, в процессе функционирования сдвиг входного кода в регистре 1 сдвига происходит слева направо, а заполнение регистра 2 памяти справа налево.

Аналогичным образом в регистре 3 памяти осуществляется накопление нулевых сигналов с выходов регистра 1 сдвига. При появлении нулевого сигнала на выходе первого разряда регистра 1 сдвига в первый разряд регистра 3 памяти записывается единичный сигнал, разрешающий запись сигнала во второй разряд. Единичный сигнал появляется на выходе i-ro разряда регистра 3 памяти, если на всех предыдущих выходах имеется единичный сигнал и на выходе

(прямом) i-го разряда регистра 1 сдвига имеется нулевой сигнал. Одновременно разрешается запись сигнала в (i-t-l)-fl разряд регистра 3 памяти. Таким образом в регистре 2 памяти осуществляется накопление единиц, а в регистре 3 - нулей входного кода.

Работа продолжается таким образом до появления единичного логического сигнала хотя бы на одном из выходов блоков 4 или 5 контроля обнуления, или на выходах регистров 2 и 3 памяти, соединенных с входами элемента ИЛИ 7, что вызывает на его выходе 10

ничный сигнал, свидетельствующий об окончании цикла работы устройства.

Результат снимается с выхода 11 элемента ИЛИ 8 устройства. Если во входном коде m а единиц, то единичный сигнал появляется либо на выходе блока 5 контроля обнуления (если в (а-1) последних разрядах регистра 1 ;двига записан единичный код), либо ia выходе регистра 2 памяти после 1акопления а единиц входного кода, 1ТО вызывает единичный сигнал на выводе элемента ИЛИ 7 и выходе элемен- а ИЛИ 8 (на инверсном выходе регистра 3 памяти, соединенном с входом лемента И 6, имеется единичный сиг- {ал) . Если во входном коде m - а щиниц, то единичный сигнал появляет- я на выходе блока 4 контроля обнуле- ия, либо на прямом выходе регистра 3 амяти, что вызывает единичный сигнал а выходе 10 элемента И 7 и нулевой игнал на выходе 11 элемента ИЛИ 8, ак как на выходе регистра 2 памяти и ыходе элемента И 6 имеются нулевые игналы.

Таким образом на выходе порогового лемента формируется единичный сиг- ал, если на входном коде имеется

а единиц, и нулевой сигнал в про- ивном случае.

Таким образом обеспечивается пред- Iарительное завершение цикла работы орогового элемента, когда во входном

оде число нулей Ра п-а, что обеспе- 1вается регистром 3, осуществляю цим f 1копление нулей входного кода, либо огда в (а-1) последнем разряде вход- пго кода имеются единицы, что осу- ств:1яется блоком 5 контроля обнуле- ,

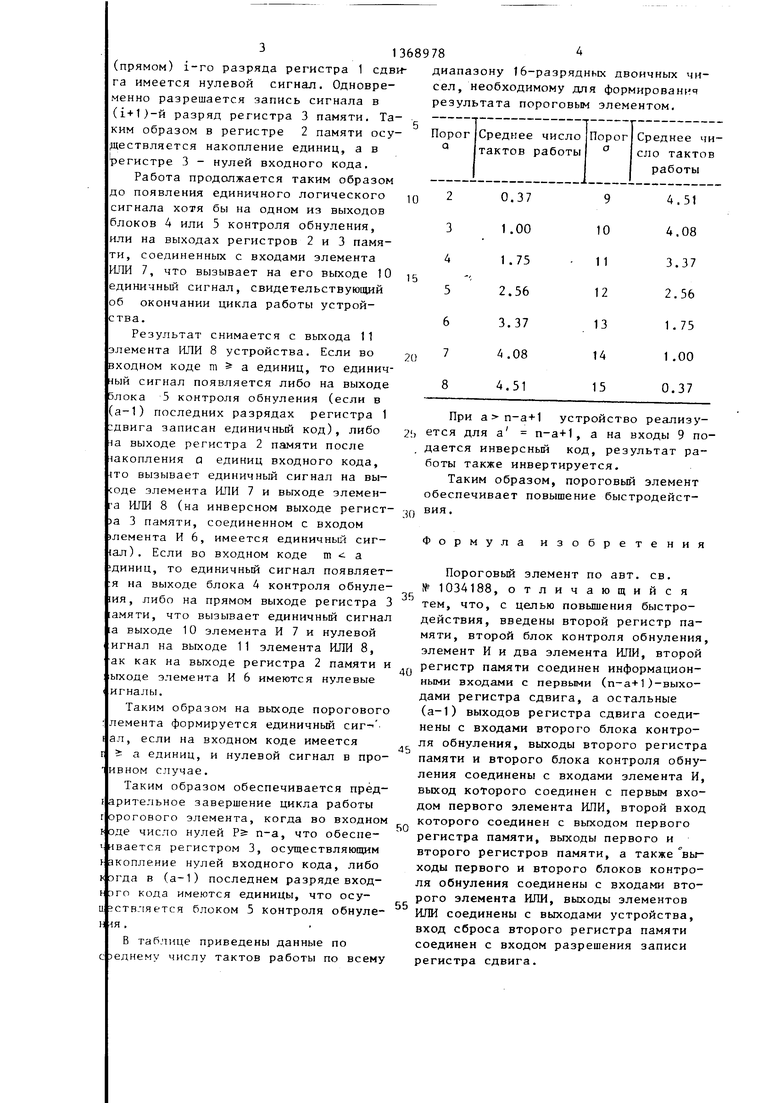

В таблице приведены данные по эеднему числу тактов работы по всему

диапазону 16-разрядных двоичных чисел, необходимому для формирования результата пороговым элементом.

10

15

20

При + 1 устройство реализу- 2;, ется для а п-а+1 , а на входы 9 подается инверсный код, результат работы также инвертируется.

Таким образом, пороговый элемент обеспечивает повышение быстродейст30 «ияФормула изобретения

5

0

5

0

5

Пороговый элемент по авт. св. № 1034188, отличающийся тем, что, с целью повышения быстродействия, введены второй регистр памяти, второй блок контроля обнуления, элемент И и два элемента ИЛИ, второй регистр памяти соединен информационными входами с первыми (n-a-i-1)-выходами регистра сдвига, а остальные (а-1) выходов регистра сдвига соединены с входами второго блока контроля обнуления, выходы второго регистра памяти и второго блока контроля обнуления соединены с входами элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого регистра памяти, выходы первого и второго регистров памяти, а также выходы первого и второго блоков контроля обнуления соединены с входами второго элемента ИЛИ, выходы элементов ИЛИ соединены с выходами устройства, вход сброса второго регистра памяти соединен с входом разрешения записи регистра сдвига.

Фиг. 2

Авторы

Даты

1988-01-23—Публикация

1986-05-28—Подача