держих мультиплексор 1 , блок - памяти программ, дешифратор 3, две группы 4 и И триггеров, генератор импульсов 5, вход 6 начальной установки, элемент НЕ 7, триггер 8, формирователь импульсов 9, элемент И 10, информационные входы 12 и Выходы 13„ Положительный эффект, заключающийся в обеспечении зависимости процесса вы1

Устройство относится к автоматике и вычислительной технике и может быть использовано для вычисления булевых функций в системах контроля и управления техническими и технологическими средствами.

Цель изобретения - повышение быстродействия за счет исключения из процесса вычисления булевых функцийар- гументов, от значения которых функции не зависят

На фиГо представлена схема устройства для вычисления булевых функций; на фиг.2 - граф-схема алгоритма вы- числения булевых функций

Устройство для вычисления булевых функций содержит мультиплексор 1, блок 2 памяти программ, дешифратор 3, группу триггеров 4, генератор 5 им- пульсов, вход 6 начальной установки, элемент НЕ 7, триггер 8, формирователь 9 импульсов, элемент И 10, группу триггеров 11, информационные входы 12, выходы 13 „

Устройство работает следующим образом.

Когда на входе 6 начальной установки имеет место сигнал, запрещантщий работу устройства, по отрицательному фронту первого после появления сигнала запрета импульса на выходе, триггера 8 формируется сигнал установки группы триггеров 4 в начальное состояние При этом на выходах группы триггеров 4 имеет место нулевой код независимо от поступления на его тактовые входы тактовых импульсов„ При

появлении на входе 6 сигнала, разре

тающего работу устройства, по отрицательному фронту первого тактового имчисления бу,1;ев1ЛУ. sJiyuKiuif от значений их apryMo.fiTOB, оПр-С11еч Влется тем, что при анализе значения любого из аргументов логических функций по результату анализа формируется условный переход к команде, по которой производится анализ другого аргумента или формируется результат вычисле- }шя, 2 И.Л., 1 табЛо

пульса, поступающего с выхода генератора 5 импульсов, на выходе триггера В формируется сигнал, разрешающий ра боту группы триггеров 4 по тактовым входам По положительным фронтам тактовых импульсов производится вызов команд программы вычисления булевых функций, записанной в блоке 2 памяти программ

Каждая команда содержит код адреса опрашиваемого аргумента, поступающий на управляющие входы мультиплексора 1, код старших разрядов адреса условного перехода, поступающий на информационные входы группы триггеров 4, при этом на информационный вход его первого триггера поступает сигнал, равный значению опрашиваемого аргумента, - так формируется младший разряд кода условного перехода, код адреса результата вычисляемой функ- ции, который поступает на адресные входы дешифратора 3, результата вычисления логической функции, который поступает на информационные входы группы триггеров 11„

Сигнал разрешения записи результата вычисления, который поступает на первый вход элемента И Ю

Вычисление булевых функций осущесвляется следуюпшм образом.

По первой команде программы, которая формируется на выходах блока 2 памяти программ, когда устройство находится в состоянии ожидания, на первый информационный вход группы триггеров 4 поступает сигнал, соответствующий значению первого опрашивемого аргумента первой функции, на

остальные информационные входы группы триггеров 4 поступают старшие разряды кода условного переходао Таким образом, на информационных входах группы триггеров 4 формируется код условного перехода, который зависит от значения опрашиваемого аргумента и определяет, какую команду устройство выполнит на первом такте работы.

После появления на установочных входах группы триггеров 4 сигнала, разрешающего его работу по тактовым входам, по положительному фронту первого тактового импульса код усл.ов ного перехода записывается в группу триггеров 4 и формируется на его выходах о По этому коду на выходах блока 2 памяти программ формируется код следующей команды, по которой в зависимости от значения опрашиваемого ранее аргумента опрашивается какой-либо из следующих аргументов этой функции, или, если, значение опрошенного аргумента полностью определяет значение вычисляемой функции, опрашивается первый аргумент следующей функциио При этом осуществляется запись результата вычисления функции в один из триггеров группы триггеров 1U

Запись результата осуществляется .по одному из тактовых входов группы, триггеров 11. Результат вычисления поступает из блока 2 памяти программ Номер тактового входа определяется кодом адреса результата, который поступает на адресные входы дешифратора 3 из блока 2 памяти программ Дешифратор 3 стробируется импульсом, формируемым по отрицательному фронту тактового импульса формирователем 9 импульсов Этот импульс поступает на стробирующий вход дешифратора 3 с выхода элемента И 10 при наличии на его первом входе сигнала разрешения записи результата, который поступает из блока 2 памяти программ,

После опроса всех необходимых для вычисления данных булевых функций аргументов, устройство можно повторить всю процедуру вычисления либо прекратить ее и выполнять две пустых, не имеющих значения команды, выполнение которых не влияет на результаты вычисления , Коды условных переходов, формирующиеся в результате выполне;- ния этих двух команд, приводят к последующему выполнению одной °из них

Устррйство находится в режиме выполнения этих команд до появления на шине 6 начальной установки

сигнала, запрещающего работу группы триггеров 4 по тактовому входу

Дпя циклического повторения процедуры вычисления логических функций необходимо в калщой команде, в которой имеется результат последней из вычисляемых функций, сформировать код условного перехода на первые два слова программы

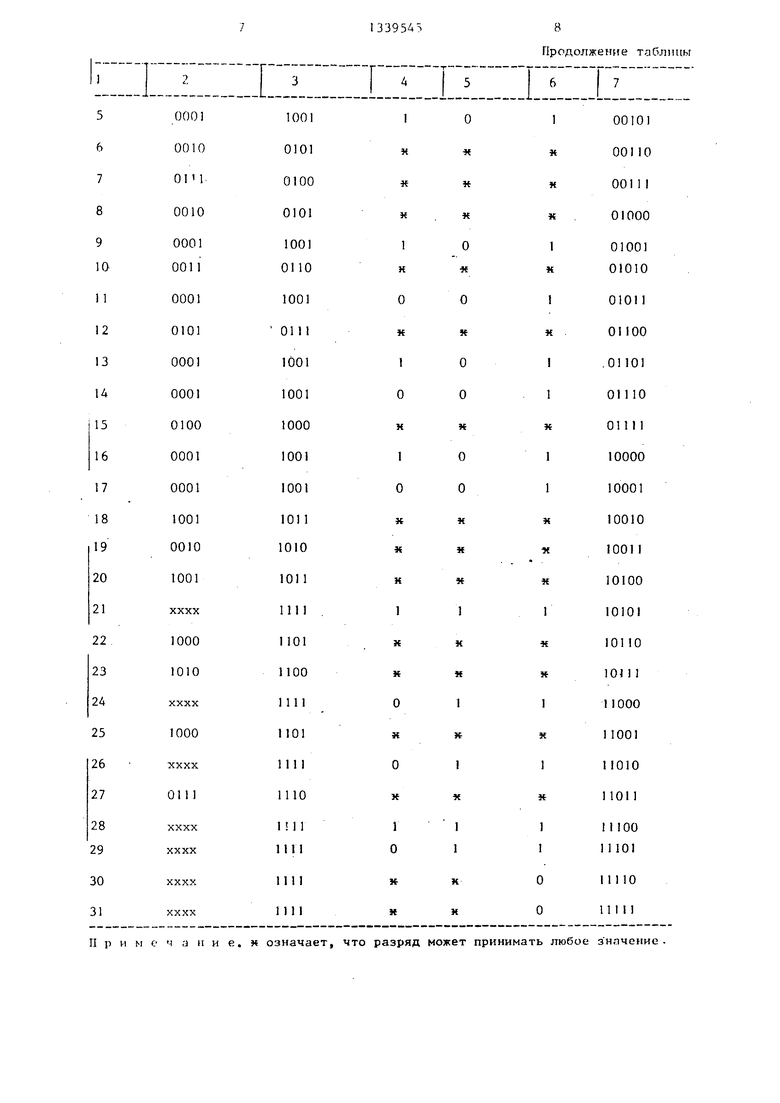

В 1 аблице представлена программа . вычисления функций

Y, , V .xj V Xg-x,;

i г- 7- 0)

Граф-схема алгоритма бинарной прог-, раммы вычисления функций (1) представлена на фиГо2,

Вычисление функций (I) при значениях аргументов х 1, х, О,

х. 1, х О, X,, 1, X, 1, 0 следующее ,

При нулевом коде на адресном входе блока 2 памяти программ производится опрос аргумента х, входящего в первую вычисляемую функцию При х 1 на выходе группы триггеров 4 по первому тактовому импульсу формируется код условного перехода 00011,

поэтому на выходе блока 2 памяти

программ формируется команда (слово) № 3„

По этой команде производится опрос аргумента X, и, поскольку х, 0, формируется код условного перехода 00100 к команде № 4

Переход к этой команде осуществляется по следующему тактовому импульсу о Затем опрашивается х и, так как Xg 0, осуществляется переход к команде. № 7„ Далее опрашивается х и осуществляется переход к команде № 8, так как х 0. Здесь

опрашивается х., поскольку х 1, осуществляется переход к команде № 11, по которой производится запись результата вычисления Y, 0 по адресу О в группе триггеров 11, и одновременно опрашивается первый аргумент ункции Yj - X , так как х 0, форируется код условного перехода к коанде № 18, по которой опрашивается ргумент По условию х 1, поэтому происходит условный переход к команде № 23 и опрашивается аргумент . По значению х, 0 осуществляется переход к команде № 24, по которой происходит запись значения 0 по первому адресу, и формируется условный переход к пустым командам № 30 и 31 о Выполнение этих команд приводит независимо от значения опра- шиваемого аргумента к формированию адреса условного перехода в одной из них с, Следовательно, происходит зацикливание программы„

Таким образом, устройство осущест- вляет вычисление булевых функций с учетом значений аргументов, входящих в эти функцииJ тем самым исключаются участки процесса вычисления, не влияюпще на конечный результат вычисления, а сам процесс вычисления зависит от значений аргументов,, Например, если х 0, вычисление первой функции заканчивается на первом такте, осуществляется переход к ко- манде № 2, по которой рассматривается значение аргумента х,, как аргумента функции Yj , и происходит запис значения Y, 0 в группу триггеров по адресу 0.

Формула изобретения

Устройство для вычисле1-шя булевых функций, содержащее блок памяти программ, мультиплексор, генератор импульсов, дешифратор, триггер, элемент НЕ, элемент И, причем выходы кода адреса опрашиваемого аргумента блока памяти программ соединены с управляющими входами мультиплексора, отличающееся тем, что, с

целью повьпнения быстродействия за счет исключения из процесса вычисления булевых функций аргументов, от значений которых функции не зависят, оно содержит две группы триггеров и формирователь импульсов, причем информационные входы устройства соединены с информационными входами мультиплексора, выход которого соединен с информационным входом первого триггера первой группы, информационные входы остальных триггеров которой соединены с выходами кода адреса условного перехода блока памяти программ, выходы кода адреса.результата которого соединены с адресными входами дешифратора, стробируюш гй вход которого соединен с выходом элемента И, первый вход которого соединен с выходом разрешения записи результата блока памяти программ, второй вход элемента И соединен с выходом формирователя импульсов, вход которого соединен с тактовым входом триггера и выходом элемента НЕ, вход которого соединен с выходом генератора импульсов и тактовыми входами триггеров первой группы, установочные входы которых соединены с выходом тригтера, информационный вход которого соединен с входом начальной установки устройства, выходы которого соединены с выходами -триггеров второй группы, тактовые входы которых соединены с выходами дешифратора, а информационные входы триггеров втор.ой группы соединены с выходом значения результата блока памяти программ адресные входы которого соединены с выходами триггеров первой группы„

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления булевых функций | 1988 |

|

SU1501033A1 |

| Устройство для вычисления булевых функций | 1988 |

|

SU1608641A1 |

| Устройство для определения значений булевых функций | 1985 |

|

SU1315965A1 |

| Устройство для реализации булевых функций | 1986 |

|

SU1310801A1 |

| Управляющая логическая машина | 1983 |

|

SU1119022A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для временного программного управления | 1985 |

|

SU1290259A1 |

| УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2003 |

|

RU2254603C1 |

| Устройство для вычисления функции | 1985 |

|

SU1290305A1 |

Изобретение относится к автоматике и вычислительной технике и пред- назначено для вычислений булевых функций. Цель изобретения - повьшзение быстродействия за счет исключения из процесса вычисления булевых функций аргументов, от значений которых функции Не зависят. Устройство соСлЭ СО СО ел 4; ел

Авторы

Даты

1987-09-23—Публикация

1986-01-08—Подача