ментов И, выходы которых соединены сосоответственно с первьм и вторым входами второго элемента ИЛИ, выход которого подключен к входу разрешения записи счетчика адреса перехода, выходы разрядов которого подключены соответственно к входам седьмого эле мента И, выход которого подключен к информационному входу устройства вьгоода,,к второму входу четвертого элемента И и к третьему входу шестого элемента И, четвертьй выход блока синхронизации подключен к установочному входу счетчика адреса, выходы радрядов которого соединены с адресными входами запоминающего устройства.

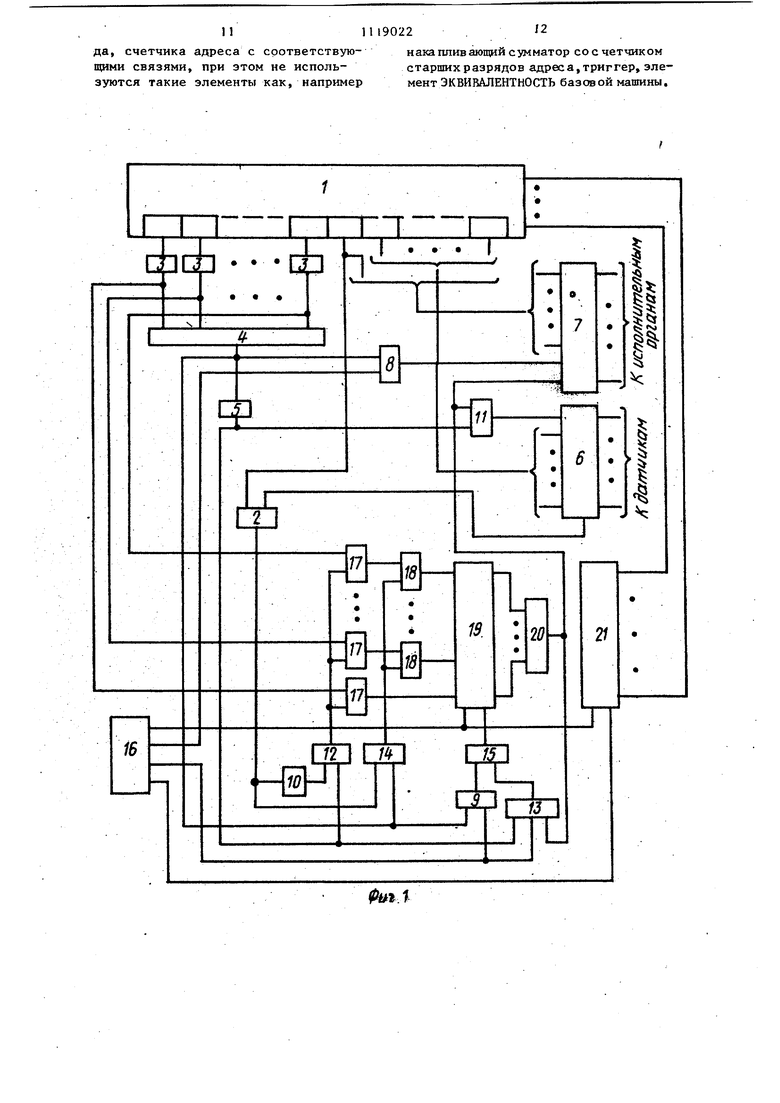

2. Машина по п. 1, отличающаяся тем, что устройство вывода содержит регистр, дешифратор адреса и элементы НЕ, вход каждого из которых соединен с соответствующим выходом дешифратора, а выход подключен к синхронизирующему входу соответствующего разряда регистра, информационные входы разрядов регистра соединены с информационным входом устройства, тактовьй вход дешифратора адреса соединен с входом синхронизации устройства, информационные входы дешифратора адреса соединены соответственно с адресными входами устройства, выходы разрядов регистра являются соответст венно информационными выходами устроства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для временного программного управления | 1985 |

|

SU1290259A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1774335A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

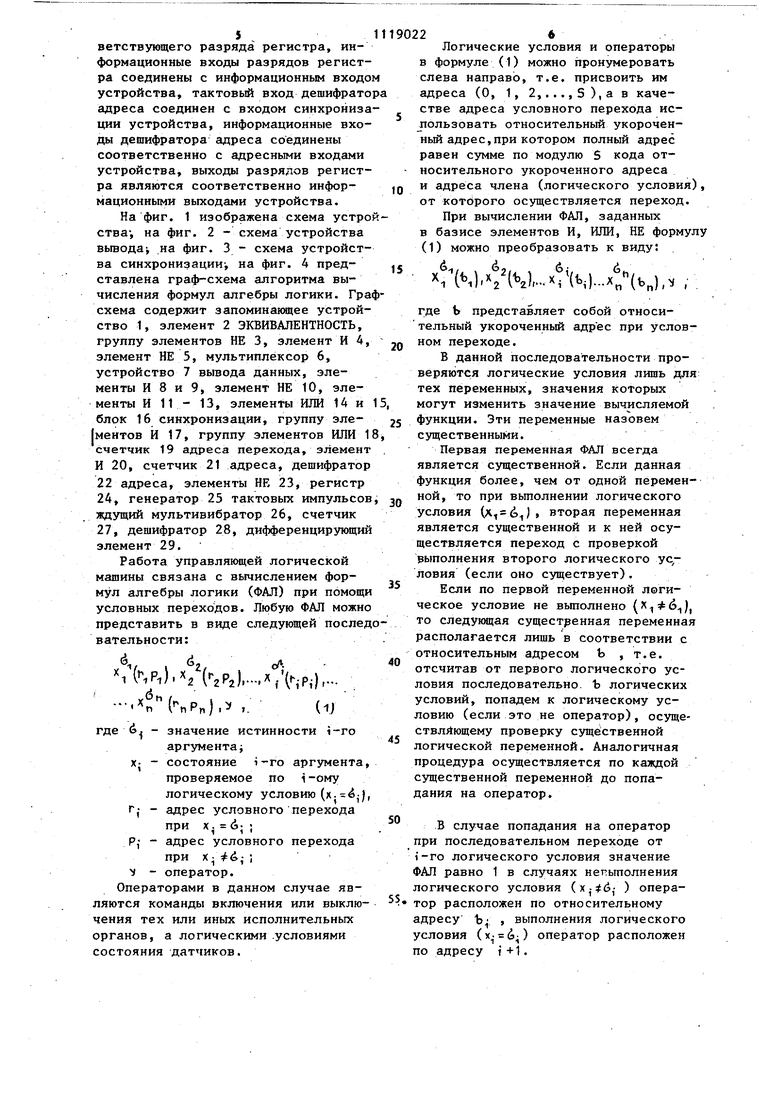

1, УПРАВЛЯЮЩАЯ ЛОГИЧЕСКАЯ МАШИНА, содержащая запоминающее устройство, устройство вывода данных, мультиплексор, группу элементов И, группу элементов НЕ, элементы И., НЕ, ИЛИ, элемент ЭКВИВАЛЕНТНОСТЬ, блок синхронизации, 1-К-й информационные выходы запоминающего устройства соединены с входами соответствующих элементов НЕ группы, выходы которых соединены с первыми входами соответствующих элементов И группы, информационные выходы мультиплексора и устройства вывода данных являются соответственно первой и второй группами выходов машины, отличающаяся тем, что, с целью сокращения аппаратурных затрат, она содержит группу элементов ИЛИ, счетчик адреса и счетчик адреса перехода, причем выходы группы элементов НЕ соединены соответственно с входами первого элемента И, выход которого подключен к первым входам второго и третьего элементов И, к первому входу первого элемента ИЛИ и к входу первого элемента НЕ, выход которого подключен к первЬм входам четвертого. пятого и шестого элементов И, К+2 п-й информационные выходы запоминающего устройства соединены соответственно с адресными входами мультиплексора, управляющий вход коммутации которого соединен с выходом четвертого элемента И, К+1 -и -и информационные выходы запоминающего устройства соединены соответственно с адресными входами устройства вывода данных, вход синхронизации которого соединен с выходом второго элемента И, К+1-Й информационный выход запоминающего устройства соединен с первым входом элемента ЭКВИВАЛЕНТНОСТЬ, второй вход которого подключен к тактирующему выходу мультиплексора, выход элемента ЭКВИВАЖНТНОСТЬ подключен к второму входу первого элемента ИЛИ и через второй элемент НЕ к второму входу пятого элемента И, выход которого соединен с вторыми входами элементов И группы, выход первого элемента И группы подключен к входу первого разряда счетчика адСО реса перехода, выходы элементов И группы, начиная с второго, подключеЬ9 ны к первым входам соответствующих tN9 элементов ИЛИ группы, вторые входы которых соединены с выходом первого элемента ИЛИ, а выходы подключены соответственно к входам разрядов счетчика адреса перехода, начиная с второго разряда, счетньй вход счетчика адреса перехода и счетный вход счетчика адреса подключены к первому выходу блока синхронизации, второй выход которого соединен с вторым вхо дом второго элемента И, третий выход блока синхронизации соединен с вторыми входами третьего и шестого эле

Изобретение относится к вычислительной технике и предназначено для решения задач логического управления технологическими процессами.

Известна управляющая логическая 5 машина, содержащая запоминающее устройство, накапливающий сумматор, счетчик, устройства ввода, вьгеода и управления, элементы И, ИЛИ, НЕ LlJОднако данная управляющая логи- О ческая машина характеризуется тем, что переход к командам вьшода может производится только по 1 (или только по о) решения. При управ- лении малоинерционными объектами это 15 приводит к увеличению аппаратурных затрат на запоминающее- устройство.

Наиболееблизким к изобретению является управляющая логическая машина, содержащая запоминающее уст- . 20 ройство, входы которого подключены к выходам накапливающего сумматора и к выходам счетчика старших разрядов адреса, выходы первой группы разрядов соединены с входами соот 25 ветствующих элементов НЕ группы и первыми входами соответствующих элеентов И первой группы, выходы котоых соединены с входами накапливаюего сумматора, выходы .второй груп- 30 ы разрядов соединены с первыми вхоами соответствующих элементов И

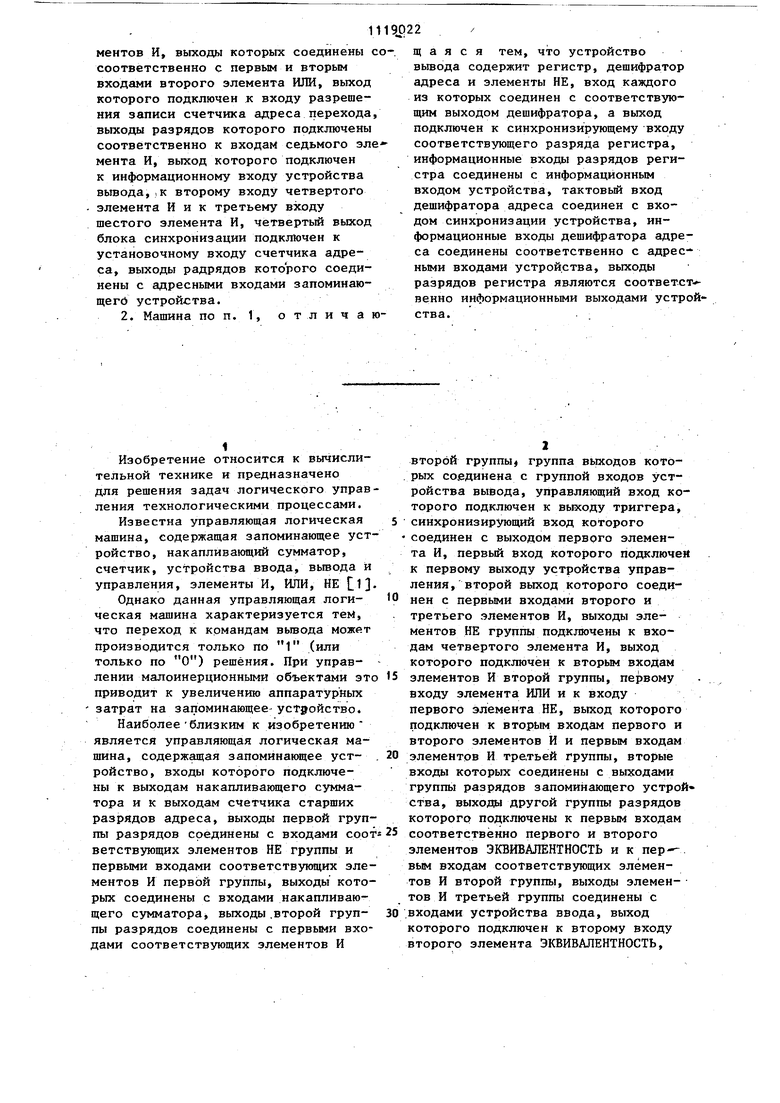

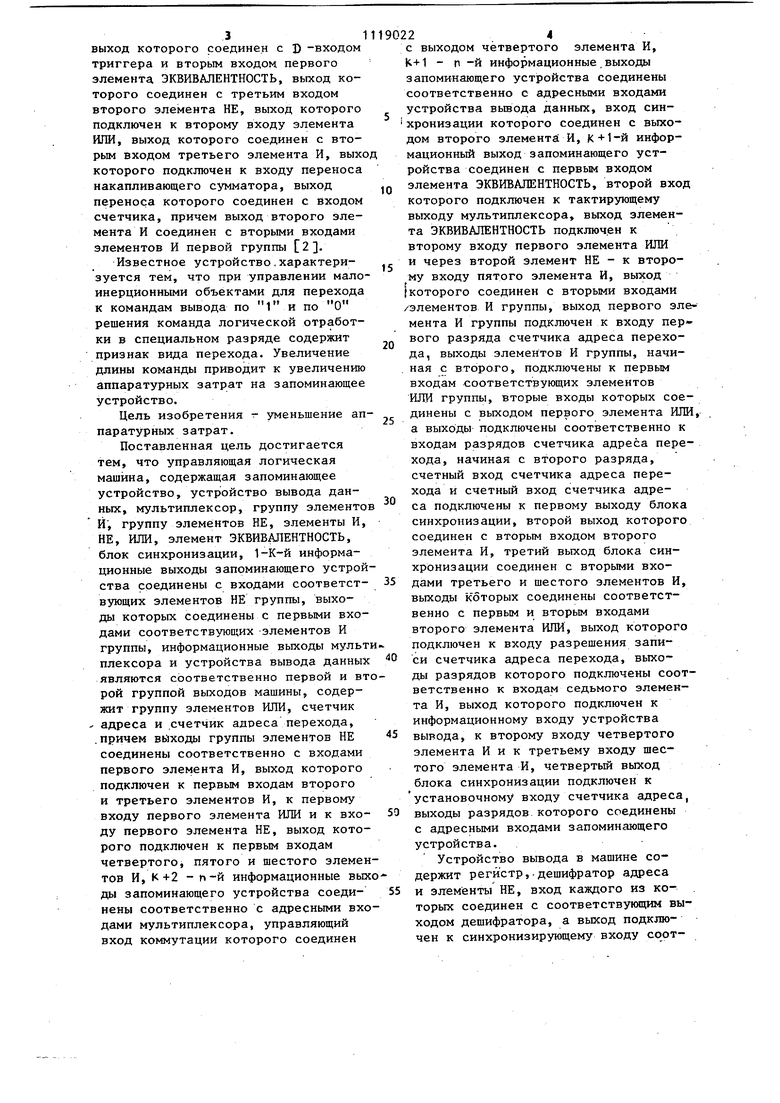

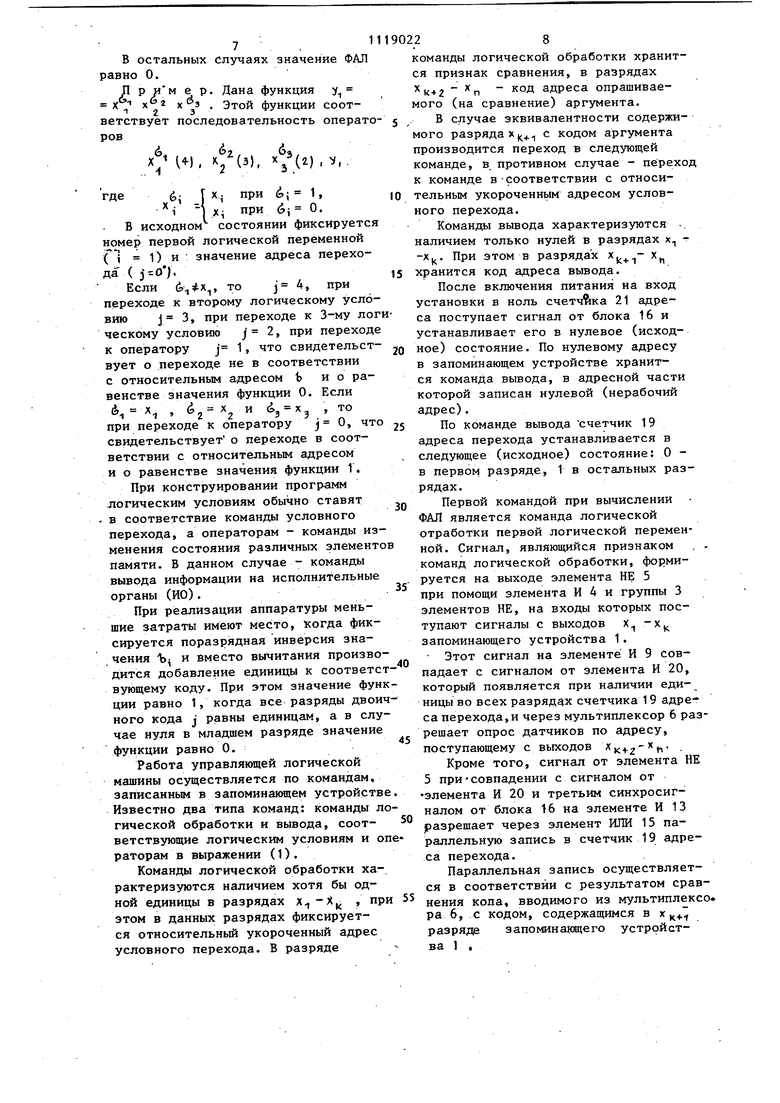

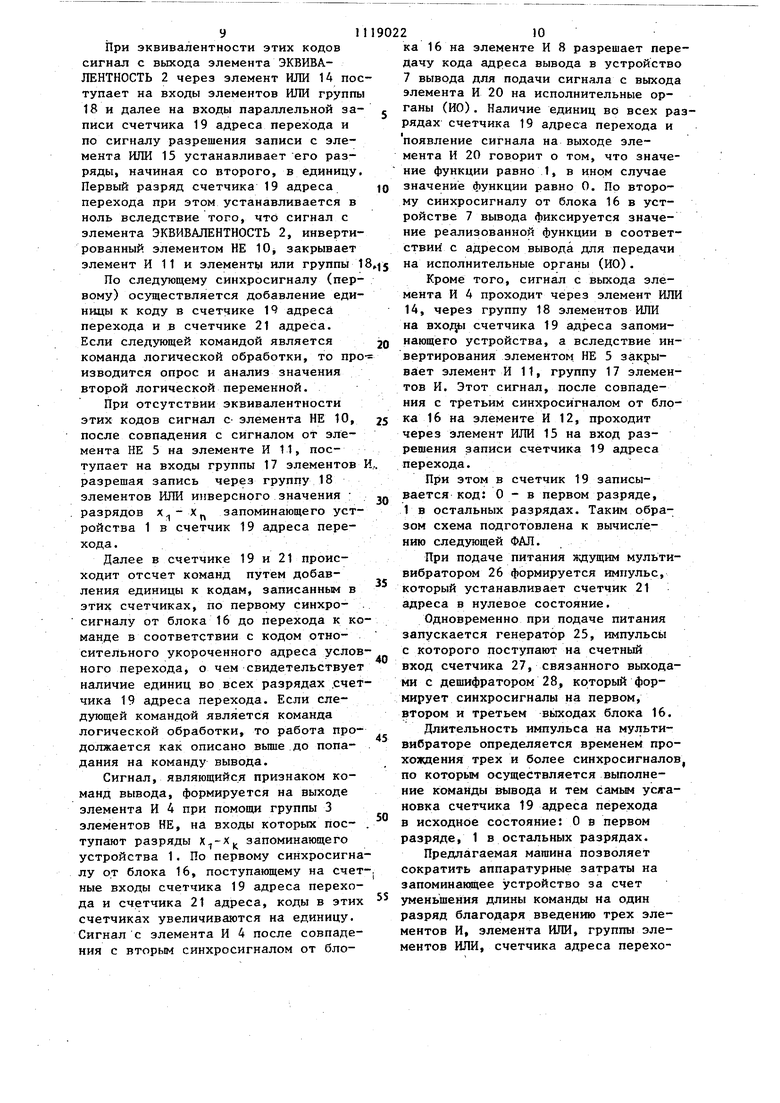

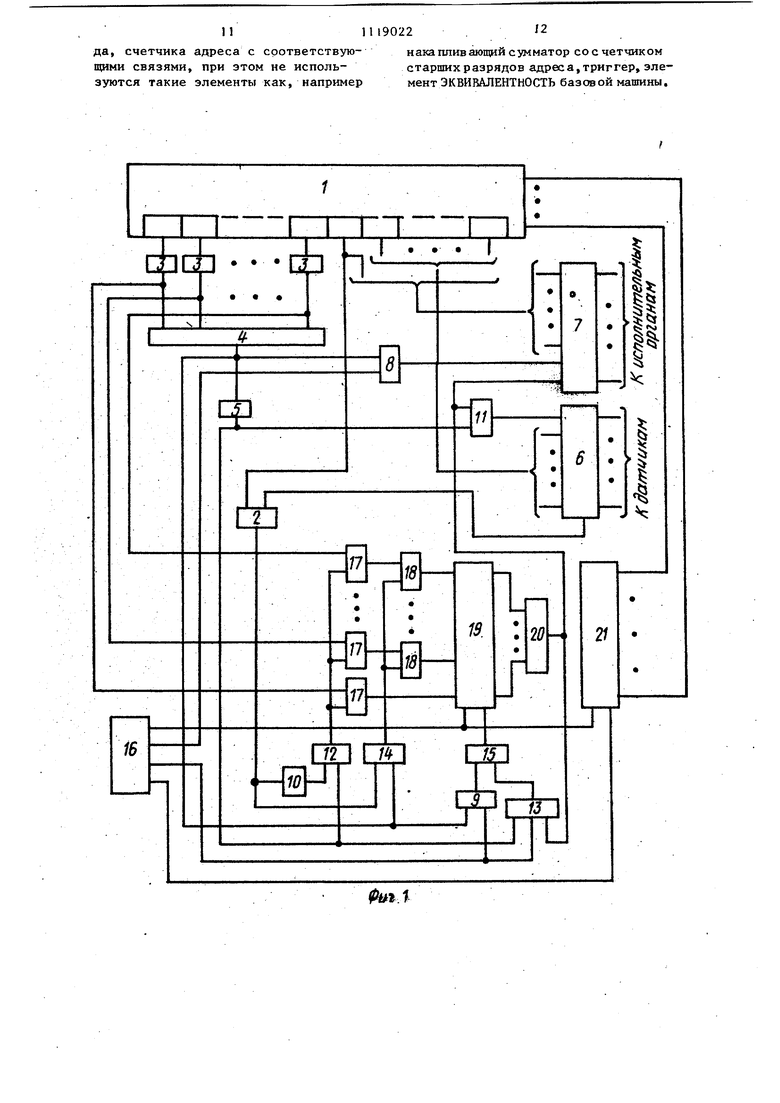

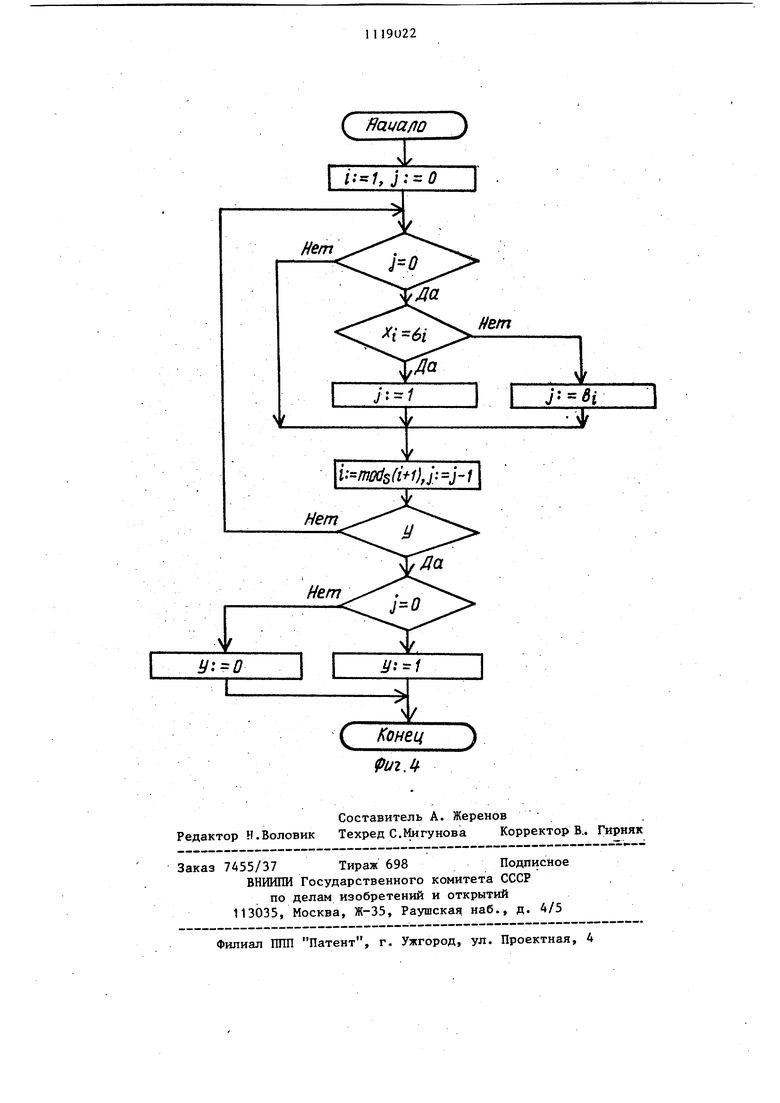

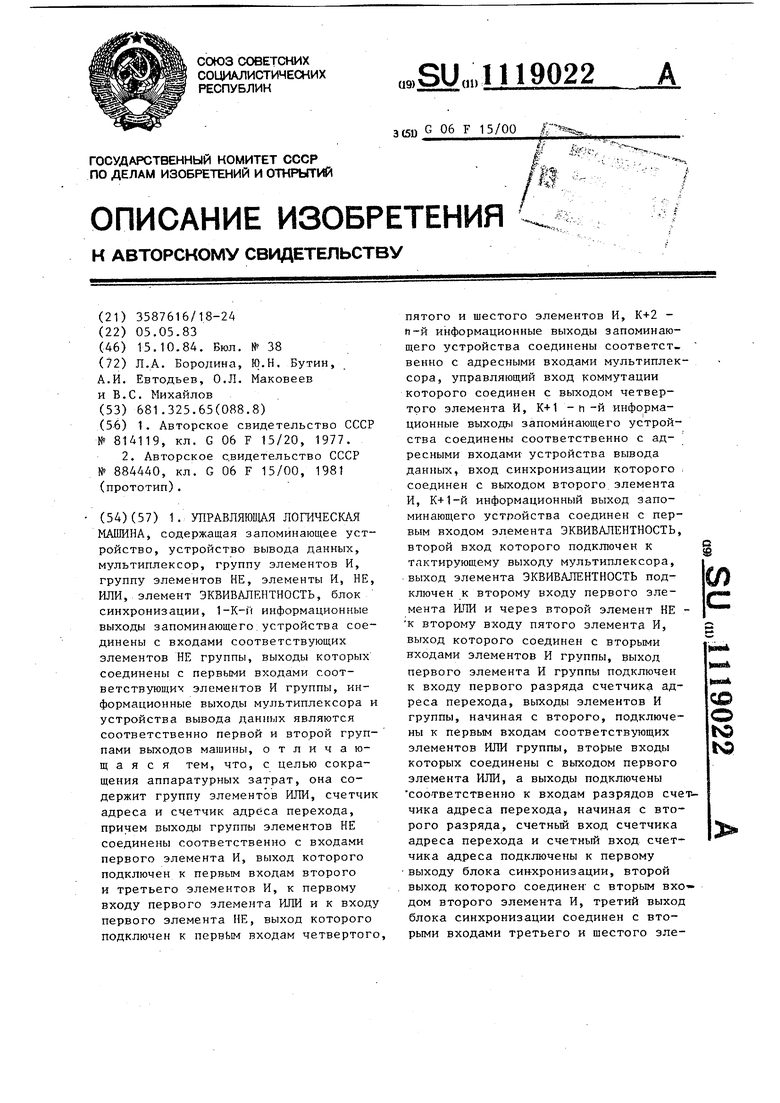

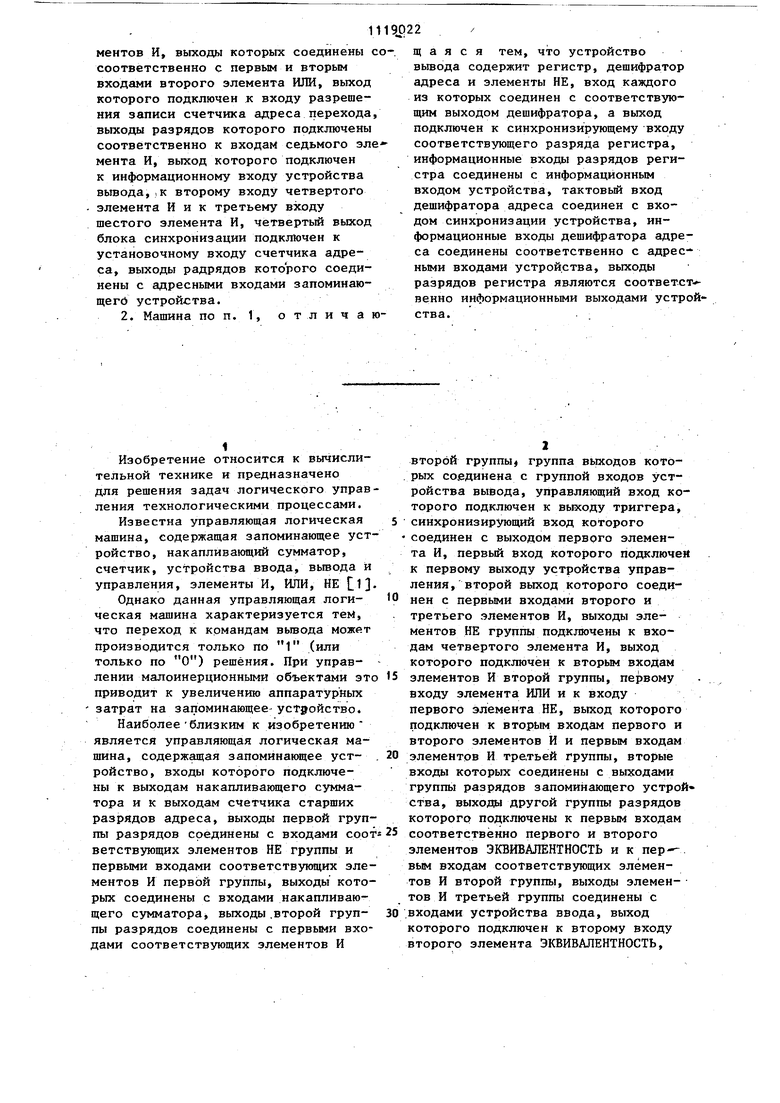

второй группы группа выходов которых соединена с группой входов устройства вывода, управляющий вход которого подключен к выходу триггера, синхронизирующий вход которого соединен с выходом первого элемента И, первый вход которого подключе к первому выходу устройства управления, второй выход которого соединен с первыми входами второго и третьего элементов И, выходы элементов НЕ группы подключены к входам четвертого элемента И, выход которого подключен к вторьм входам элементов И второй группы, первому входу элемента ИЛИ и к входу первого элемента НЕ, выход которого подключен к вторым входам первого и второго элементов И и первым входам элементов И третьей группы, вторые входы которых соединены с вь1ходами группы разрядов запоминающего устройства, выходы другой группы разрядов которого подключены к первым входам соответственно первого и второго элементов ЭКВИВАЛЕНТНОСТЬ и к первым входам соответствующих элементов И второй группы, выходы элементов И третьей группы соединены с входами устройства ввода, выход которого подключен к второму входу второго элемента ЭКВИВАЛЕНТНОСТЬ, 3 выход которого соединен с D -входом триггера и вторым входом первого элемента. ЭКВИВАЛЕНТНОСТЬ, выход которого соединен с третьим входом второго элемента НЕ, выход которого подключен к второму входу элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И, вых которого подключен к входу переноса накапливающего сумматора, выход переноса которого соединен с входом счетчика, причем выход второго элемента И соединен с вторыми входами элементов И первой группы 2. Известное устройство.характеризуется тем, что при управлении мало инерционными объектами для перехода к командам вывода по 1 и по О решения команда логической отработки в специальном разряде содержит признак вида перехода. Увеличение длины команды приводит к увеличению аппаратурных затрат на запоминающее устройство. Цель изобретения - уменьшение ап паратурных затрат. Поставленная цель достигается тем, что управляющая логическая машина, содержащая запоминающее устройство, устр ойство вывода данных, мультиплексор, группу элементо И, группу элементов НЕ, элементы И, НЕ, ИЛИ, элемент ЭКВИВАЛЕНТНОСТЬ, блок синхронизации, 1-К-й информационные выходы запоминающего устрой ства соединены с входами соответствующих элементов НЕ группы, выходы которых соединены с первыми входами соответствующих элементов И группы, информационные выходы мульт плексора и устройства вывода данных являются соответственно первой и вт рой группой выходов машины, содержит группу элементов ИЛИ, счетчик адреса и счетчик адреса перехода, .причем выходы группы элементов НЕ соединены соответственно с входами первого элемента И, выход которого подключен к первым входам второго и третьего элементов И, к первому входу первого элемента ИЛИ и к входу первого элемента НЕ, выход которого подключен к первым входам четвертого, пятого и шестого элемен тов И, К+2 - п-й информационные вых ды запоминающего устройства соединены соответственно с адресными вхо дами мультиплексора, управляющий вход коммутации которого соединен 24 с выходом четвертого элемента И, К+1 - п -и информационные выходы запоминающего усттройства соединены соответственно с адресными входами устройства вьшода данных, вход синхронизации которого соединен с выходом второго элемента И, К+1-й информационный выход запоминающего устройства соединен с первым входом элемента ЭКВИВАЛЕНТНОСТЬ, второй вход которого подключен к тактирующему выходу мультиплексора, выход элемента ЭКВИВАЛЕНТНОСТЬ подключен к второму входу первого элемента ИЛИ и череэ второй элемент НЕ - к второму входу пятого элемента И, выход которого соединен с вторыми входами элементов И группы, выход первого элемента И группы подключен к входу первого разряда счетчика адреса перехода, выходы элементов И группы, начиная с второго, подключены к первым входам соответствующих элементов ИЛИ группы, вторые входы которых соединены с выходом первого элемента ИЛИ, а выходы подключены соответственно к входам разрядов счетчика адреса перехода, начиная с второго разряда, счетный вход счетчика адреса перехода и счетный вход счетчика адреса подключены к первому выходу блока синхронизации, второй выход которого соединен с вторым входом второго элемента И, третий выход блока синхронизации соединен с вторыми входами третьего и шестого элементов И, выходы Которых соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого подключен к входу разрешения записи счетчика адреса перехода, выходы разрядов которого подключены соответственно к входам седьмого элемента И, выход которого подключен к информационному входу устройства вывода, к второму входу четвертого элемента И и к третьему входу шестого элемента И, четвертьй выход блока синхронизации подключен к установочному входу счетчика адреса, выходы разрядов, которого соединены с адресными входами запоминающего устройства. Устройство вывода в машине содержит регистр,.дешифратор адреса и элементы НЕ, вход каждого из ко- . торых соединен с соответствующим выходом дешифратора, а выход подключен к синхронизирующему входу соответствующего разряда регистра, информационные входы разрядов регистра соединены с информационным входо устройства, тактовый вход дешифрато адреса соединен с входом синхрониза ции устройства, информационные входы дешифратора адреса соединены соответственно с адресными входами устройства, выходы разрядов регистра являются соответственно информационными выходами устройства. На фиг. 1 изображена схема устро ства-, на фиг. 2 - схема устройства вьгоода на фиг. 3 - схема устройства синхронизации, на фиг. 4 представлена граф-схема алгоритма вычисления формул алгебры логики. Гра схема содержит запоминаницее устройство 1, элемент 2 ЭКВИВАЛЕНТНОСТЬ, группу элементов НЕ 3, элемент И 4 элемент НЕ 5, мультиплексор 6, устройство 7 вывода данных, элементы И 8 и 9, элемент НЕ 10, элементы И 11 - 13, элементы ИЛИ 14 и блок 16 синхронизации, группу эле ментов И 17, группу элементов ИЛИ 1 счетчик 19 адреса перехода, элемент И 20, счетчик 21 адреса, дешифратор 22 адреса, элементы HR 23, регистр 24, генератор 25 тактовых импульсов ждущий мультивибратор 26, счетчик 27, дешифратор 28, дифференцирующий элемент 29. Работа управляющей логической машины связана с вычислением формул алгебры логики (ФАЛ) при помощи условных переходов. Любую ФАЛ можно представить в виде следующей послед вательности: (p1).).-.i;(-pi)r.. КРп). значение истинности 1-го аргументаi состояние i-ro аргумента, проверяемое по i-ому логическому условию (х- и,-) адрес условного перехода при x.d.;; адрес условного перехода при ; оператор. Операторами в данном случае являются команды включения или выключения тех или иных исполнительных органов, а логическими .условиями состояния датчиков. 26 Логические условия и операторы в формуле (1) можно пронумеровать слева направо, т.е. присвоить им адреса (О, 1, 2,...,S),a в качестве адреса условного перехода использовать относительный укороченный адрес, при котором полный адрес равен сумме по модулю 5 кода относительного укороченного адреса и адреса члена (логического условия), от котброго осуществляется переход. При вычислении ФАЛ, заданных в базисе элементов И, ИЛИ, НЕ формулу (1) можно преобразовать к виду: ,«hu..«t(«)...(bj,,, г;де Ь представляет собой относительный укороченный адрес при условном переходе. В данной последовательности проверяются логические условия лишь для тех переменных, значения которых могут изменить значение вычисляемой функции. Эти переменные назовем сзпцественными. Первая переменная ФАЛ всегда является существенной. Если данная функция более, чем от одной переменной, то при вьтолнении логического условия (х, 6) ) вторая переменная является существенной и к ней осуществляется переход с проверкой выполнения второго логического условия (если оно суш;ествует) . Если по первой переменной Логическое условие не выполнено , то следукицая сущестренная переменная располагается лишь в соответствии с относительным адресом b , т.е. отсчитав от первого логического условия последовательно. Ъ логических условий, попадем к логическому условию (если это не оператор), осуществлйющему проверку существенной логической переменной. Аналогичная процедура осуществляется по каждой существенной переменной до попадания на оператор. В случае попадания на оператор при последовательном переходе от i-ro логического условия значение АЛ равно 1 в случаях невыполнения огического условия (х,,- ) оператор расположен по относительному дресу Ъ| , выполнения логического словия (х. (э) оператор расположен о адресу t +1. В остальных случаях значение ФАЛ равно 0. П р им ер. Дана функция ч о /i. л 1 Этой функции соот г 3 ветствует последовательность операт ров В исходном состоянии фиксируетс номер первой логической переменной (1 1) и : значение адреса перехода ( . Если d,x, то j переходе к второму логическому усло вию j 3, при переходе к 3-му ло ческому условию j 2, при переход к оператору j 1, что свидетельст вует о переходе не в соответствии с относительным адресом fe и о равенстве значения функции 0. Если при переходе к оператору j О, чт свидетельствует о переходе в соответствии с относительным адресом и о равенстве значения функции 1, При конструировании программ логическим условиям обычно ставят . в соответствие команды условного перехода, а операторам - команды из менения состояния различных элемент памяти. В данном случае - команды вывода информации на исполнительные органы (НО). При реализации аппаратуры меньшие затраты имеют место, когда фиксируется поразрядная инверсия значения - и вместо вычитания произво дится добавление единицы к соответс вующему коду. При этом значение фун ции равно 1, когда все разряды двои ного кода j равны единицам, а в слу чае нуля в младшем разряде значени функции равно 0. Работа управляющей логической машины осуществляется по командам, записанным в запоминающем устройств Известно два типа команд: команды л гической обработки и вывода, соответствующие логическим условиям и o раторам в выражении (1). Команды логической обработки характеризуются наличием хотя бы одной единицы в разрядах х-, -Х , пр этом в данных разрядах фиксируется относительный укороченный адрес условного перехода. В разряде команды логической обработки хранится признак сравнения, в разрядах к+г °Л адреса опрашиваемого (на сравнение) аргумента. В случае эквивалентности содержимого разряда х, с кодом аргумента производится переход в следующей команде, в, противном случае - переход к команде в-соответствии с относительным укороченным адресом условного перехода. Команды вывода характеризуются -. наличием только нулей в разрядах х -Хц. При этом в разрядах х,- х хранится код адреса вывода. После включения питания на вход установки в ноль счетчика 21 адреса поступает сигнал от блока 16 и устанавливает его в нулевое (исходное) состояние. По нулевому адресу в запоминающем устройстве хранится команда вывода, в адресной части которой записан нулевой (нерабочий адрес). По команде вывода счетчик 19 адреса перехода устанавливается в следующее (исходное) состояние: О в первом разряде, 1 в остальных разрядах. Первой командой при вычислении ФАЛ является команда логической отработки первой логической переменной. Сигнал, являющийся признаком , . команд логической обработки, формируется на выходе элемента НЕ 5 при помощи элемента И 4 и группы 3 элементов НЕ, на входы которых посS тупают сигналы с выходов запоминающего устройства 1. Этот сигнал на элементе И 9 совпадает с сигналом от элемента И 20, который появляется при наличии единицы во всех разрядах счетчика 19 адреса перехода,и через мультиплексор 6 разрешает опрос датчиков по адресу, поступающему с выходов Кроме того, сигнал от элемента НЕ 5 присовпадении с сигналом от элемента И 20 и третьим синхросигналом от блока 16 на элементе И 13 разрешает через элемент ИЛИ 15 параллельную запись в счетчик 19 адреса перехода. Параллельная запись осуществляется в соответствии с результатом сравнения копа, вводимого из мультиплексо ра 6, с кодом, содержащимся в х разряде запоминающего устройства 1 , При эквивалентности этих кодов сигнал с выхода элемента ЭКВИВАЛЕНТНОСТЬ 2 через элемент ИЛИ 14 по тупает на входы элементов ИЛИ группы 18 и далее на входы параллельной за писи счетчика 19 адреса перехода и по сигналу разрешения записи с элемента ИЛИ 15 устанавливает его разряды, начиная со второго, в единицу Первый разряд счетчика 19 адреса перехода при этом устанавливается в ноль вследствие того, что сигнал с элемента ЭКВИВАЛЕНТНОСТЬ 2, инверти рованный элементом НЕ 10j закрывает элемент И 11 и элементы или группы По следующему синхросигналу (пер вому) осуществляется добавление еди ницы к коду в счетчике 19 адреса перехода и в счетчике 21 адреса. Если следующей командой является команда логической обработки, то про изводится опрос и анализ значения второй логической переменной. При отсутствии эквивалентности этих кодов сигнал с элемента НЕ 10, после совпадения с сигналом от элемента НЕ 5 на элементе И 11, поступает на входы группы 17 элементов разрешая запись через группу 18 элементов ИЛИ инверсного значения : разрядов X.-- х запоминающего устройства 1 в счетчик 19 адреса перехода . Далее в счетчике 19 и 21 происходит отсчет команд путем добавления единицы к кодам, записанным в этих счетчиках, по первому синхросигналу от блока 16 до перехода к ко манде в соответствии с кодом относительного укороченного адреса услов ного перехода, о чем свидетельствует наличие единиц во всех разрядах .счет чика 19 адреса перехода. Если следующей командой является команда логической обработки, то работа продолжается как описано вьше до попадания на команду вывода. Сигнал, являющийся признаком команд вывода, формируется на выходе элемента И 4 при помощи группы 3 элементов НЕ, на входы которых поступгшзт разряды , запоминающего устройства 1. По первому синхросигна лу от блока 16, поступающему на счет ные входы счетчика 19 адреса перехода и счетчика 21 адреса, коды в этих счетчиках увеличиваются на единицу. Сигнал с элемента И 4 после совпадения с вторым синхросигналом от блока 16 на элементе И В разрешает передачу кода адреса вывода в устройство 7 вывода для подачи сигнала с выхода элемента И 20 на исполнительные органы (ИО). Наличие единиц во всех разрядах счетчика 19 адреса перехода и появление сигнала на выходе элемента И 20 говорит о том, что значение функции равно 1, в ином случае значение функции равно 0. По второму синхросигналу от блока 16 в устройстве 7 вывода фиксируется значение реализованной функции в соответствии с адресом вывода для передачи на исполнительные органы (ИО). Кроме того, сигнал с выхода элемента И 4 проходит через элемент ИЛИ 14, через группу 18 элементов ИЛИ на счетчика 19 адреса запоминающего устройства, а вследствие инвертирования элементом НЕ 5 элемент И 11, группу 17 элементов И. Этот сигнал, после совпадения с третьим синхросигналом от блока 16 на элементе И 12, проходит через элемент ИЛИ 15 на вход разрешения записи счетчика 19 адреса перехода. При этом в счетчик 19 записывается код: О - в первом разряде, 1 в остальных разрядах. Таким образом схема подготовлена к вычислению следующей ФАЛ. При подаче питания яэдущим мультивибратором 26 формируется импульс, который устанавливает счетчик 21 адреса в нулевое состояние. Одновременно при подаче питания запускается генератор 25, импульсы с которого поступают на счетный вход счетчика 27, связанного выходами с дешифратором 28, который формирует синхросигналы на первом, втором и третьем вьпсодах блока 16. Длительность импульса на мультивибраторе определяется временем прохождения трех и более синхросигналов, по которым осуществляется выполнение команды вывода и тем самым уся-ановка счетчика 19 адреса перехода в исходное состояние: О в первом разряде, 1 в остальных разрядах. Предлагаемая машина позволяет сократить аппаратурные затраты на запоминающее устройство за счет уменьшения длины команды на один разряд благодаря введению трех элементов И, элемента ИЖ, группы элементов ИЛИ, счетчика адреса перехо1111190222

да, счетчика адреса с соответствую-накапливающий сумматор со счетчиком

щими связями, при этом не исполь-старшихразрядов адреса,триггер, элезуются такие элементы как, напримермент ЭКВИВАЛЕНТНОСТЬ базовой мапшны.

к выходи ВыВоАх из запоминающего жмента в tJcmpoucmSa 1

Г

п

г

/г исполнительным органам Фи1. 2

li

Фиг.З

( Наш/10

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 884440, кл, G 06 F 15/00, 1981 (прототип), | |||

Авторы

Даты

1984-10-15—Публикация

1983-05-05—Подача