формации, злемеичъ If 3,-3i 1 ервой группы, элементы И BTopof i труп пы, настроечный вход 5, управляющий вход 6, элементы Ш1И 7,,-7, первой группы , арифметические блоки 8,-8 , второй информационный вход 9 второй информационный выход 10, адресный вход 11, шину 12 ввода тестовой информации, элементы И 13,-135 третьей группы, элементы И K,-14a, четвертой группы, элементы НЕ первой группы, элементы И 16,-16, пятой группы, элементы И 17,-17, шестой

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств для обработки цифровых данных„

Цель изобретения - повышение достоверности контроля устройства о

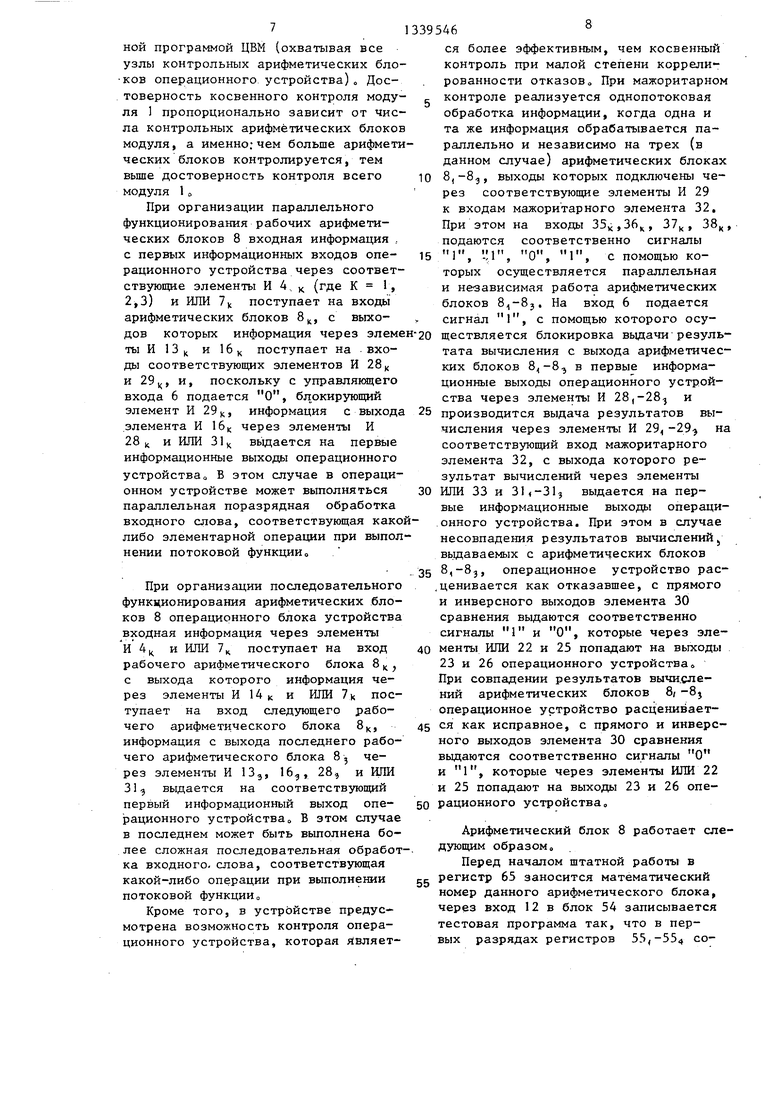

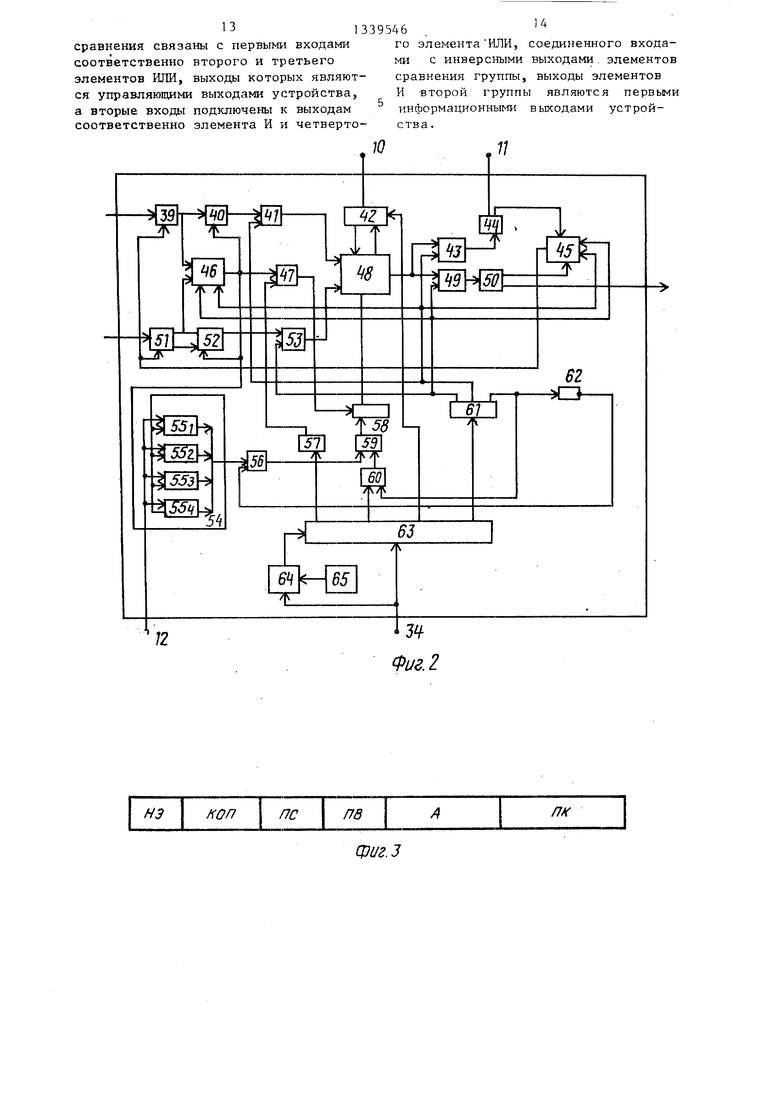

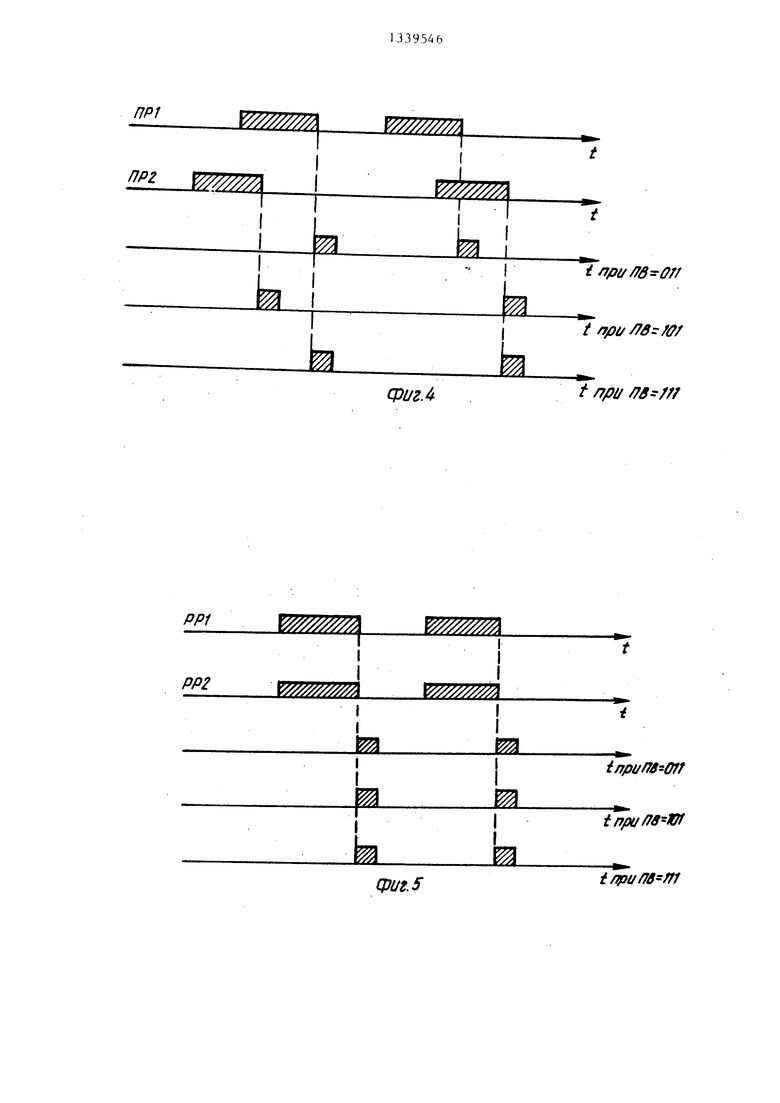

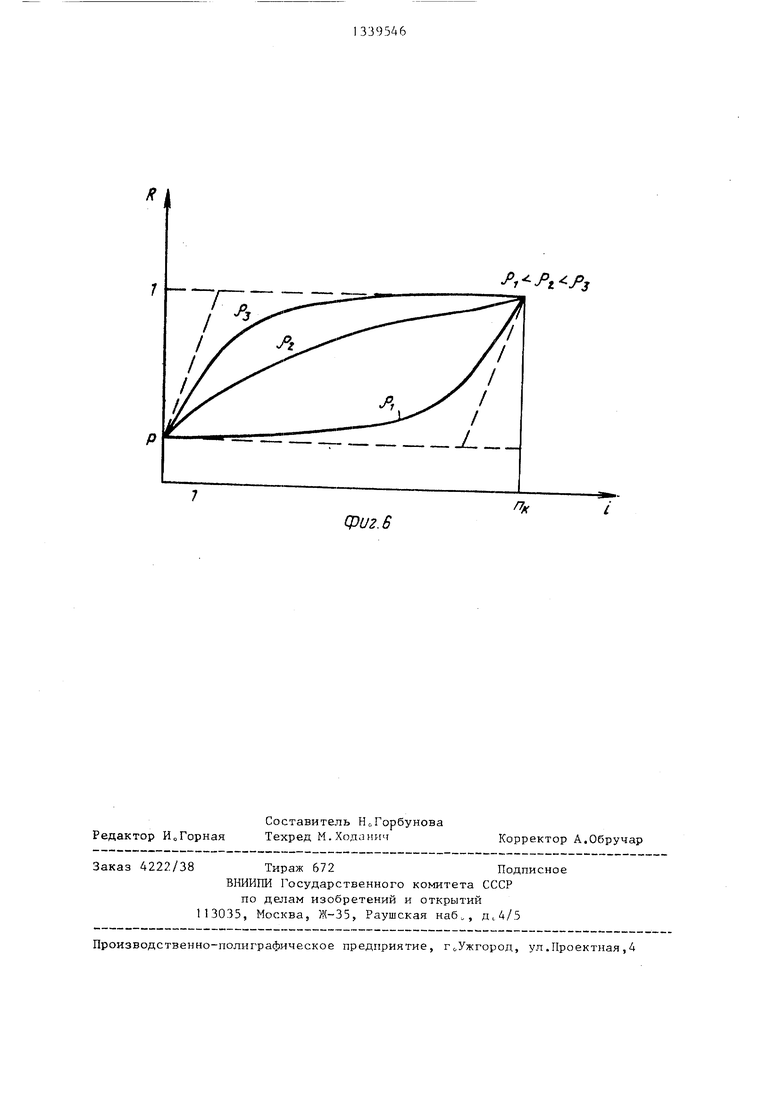

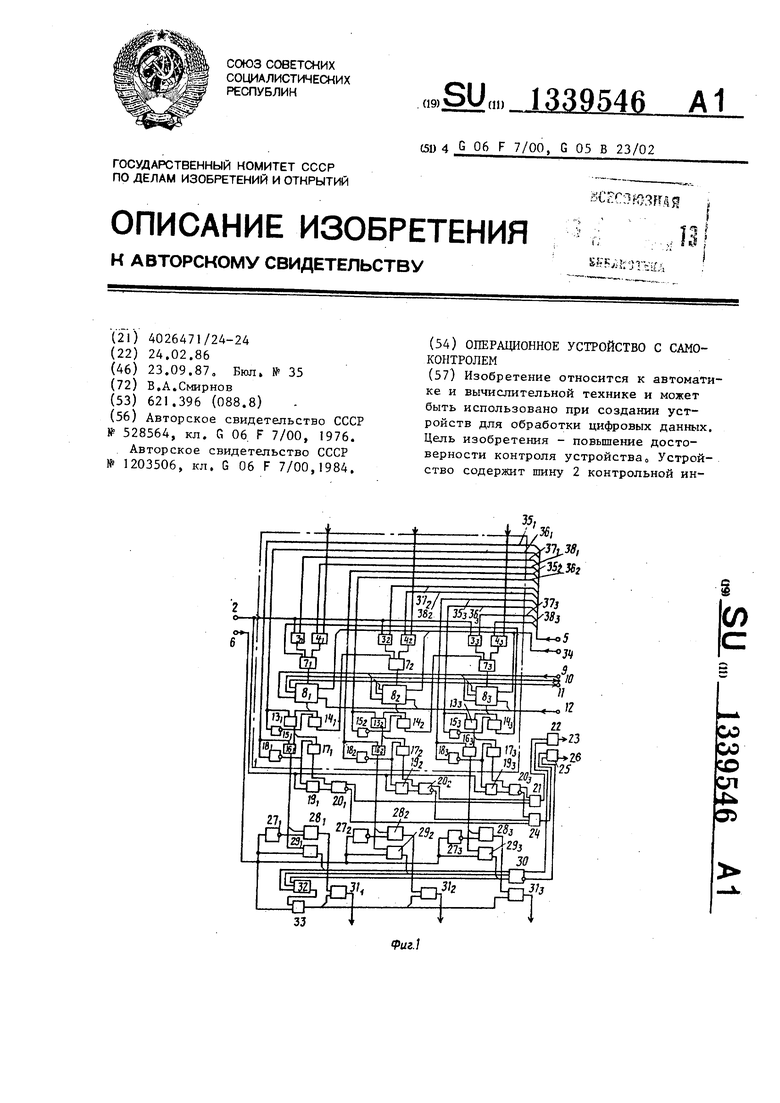

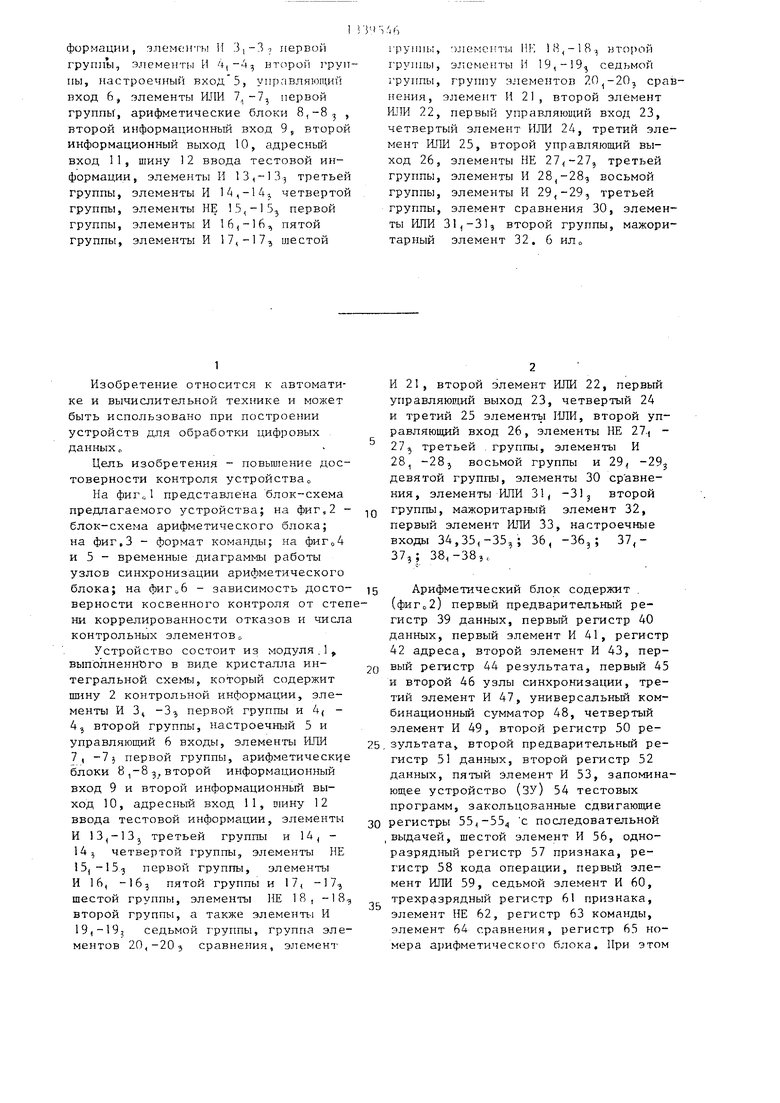

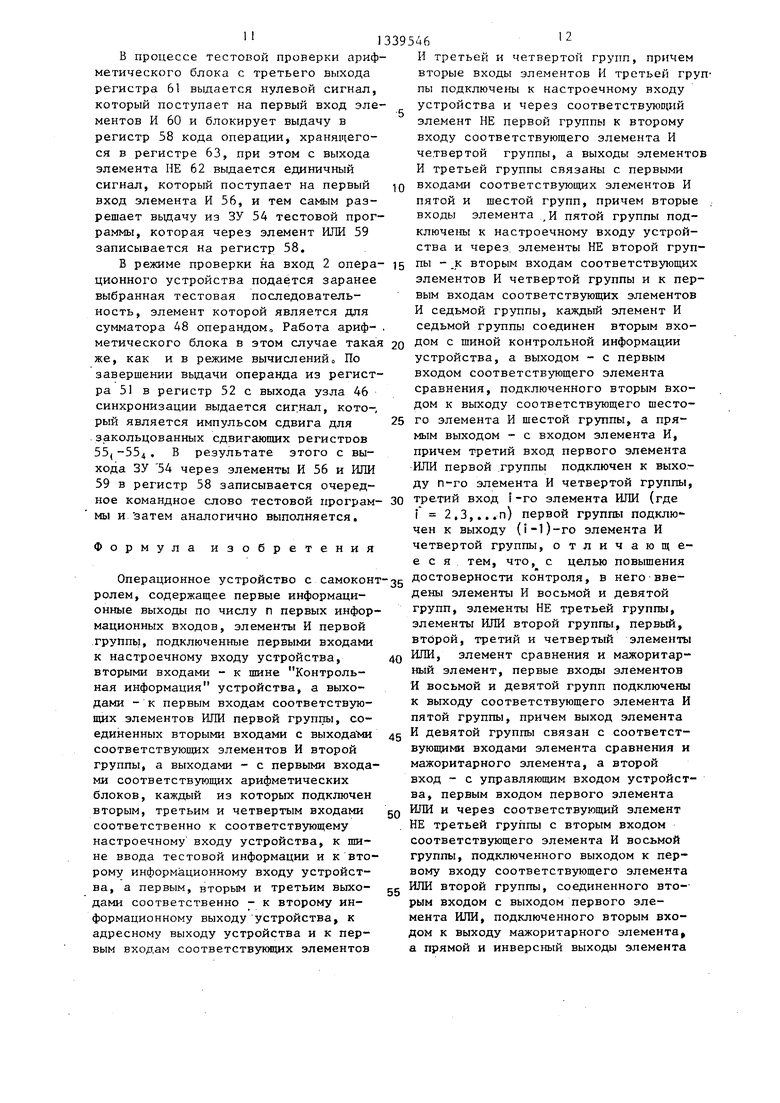

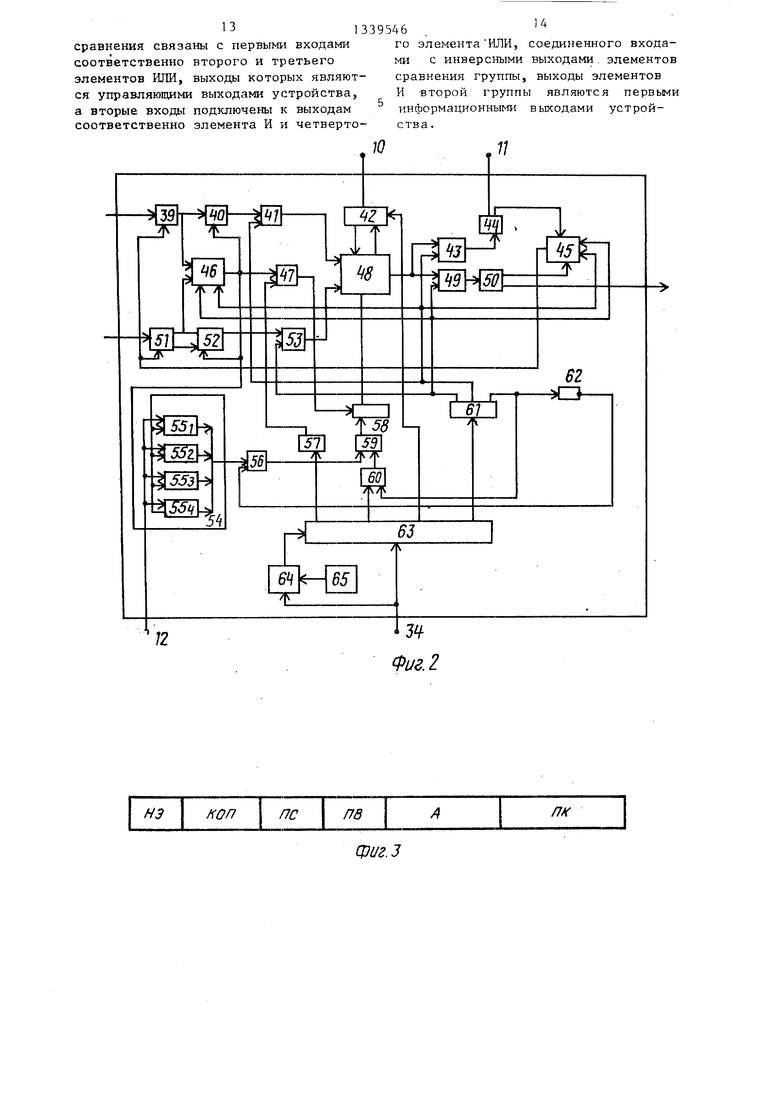

На фиг,,1 представлена блок-схема предлагаемого устройства; на фиг,2 - блок-схема арифметического блока; на фиг,3 - формат команды; на фиг о 4 и 5 - временные диаграммы работы узлов синхронизации арифметического блока; на фигоб - зависимость досто- верности косвенного контроля от степни коррелированности отказов и числа контрольных элементов с,

Устройство состоит из модуля.1,

выполненного в виде кристалла интегральнои схемы, который содержит шину 2 контрольной информации, элементы И 3 -3 первой групш 1 и 4( - 4, второй группы, настроечный 5 и управляющий 6 входы, элементы ИЛИ 7, -7з первой группы, арифметическ е блоки 8,-85 второй информационный вход 9 и второй информационный выход 10, адресный вход 11, 01ину 12 ввода тестовой информации, элементы И 3,-13j третьей группы и 14, - 14 ;j четвертой группы, элементы НЕ 15, -15.

первой группы, элементы И 16, -165 пятой группы и 17, -17, шестой группы, элементы НЕ 18, -18 второй группы, а также элеменпч И 19,-19, седьмой т руппы, группа элементов 20,-20} сравнения, элемент

j4S:jh

I pyiiiibi, jJieMCHTbi ИР. 8,-18.5 нторой группы, элементы И 19,-19 седьмой группы, группу элементов 7.0 -20, сравнения, элемент И 21, второй элемент ШШ 22, первый управляющий вход 23, четвертый элемент ИЛИ 24, третий элемент Ш1И 25, второй управляющий выход 26, элементы НЕ , третьей группы, элементы И 28,-28, восьмой группы, эле.менты И 29,-29 третьей группы, элемент сравнения 30, элементы ИЛИ 31,-31, второй группы, мажоритарный элемент 32. 6 ил„

5

0

5

Ь

И 21 , второй элемент ИЛИ 22, первый управляющий выход 23, четвертый 24 и третий 25 элементь ИЛИ, второй управляющий вход 26, элементы НЕ 27.) - 27 третьей . группы, элементы И 28, -28 восьмой группы и 29 29j девятой группы, элементы 30 ср авне- ния, элементы ИЛИ 31, -31, второй группы, мажоритарный элемент 32, первый элемент ИЛИ 33, настроечные входы 34,35,-35,; 36, -36,; 37,- 37,; 38,-38,,

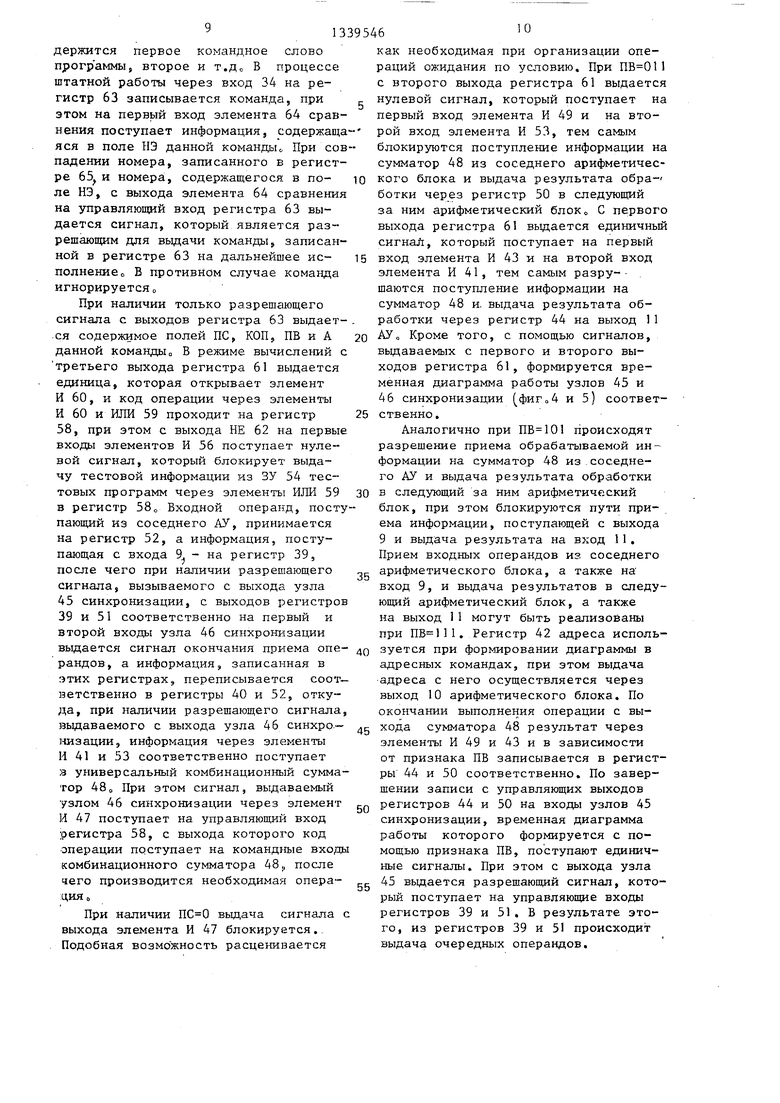

Арифметический блок содержит . (фиГ(,2) первый предварительный регистр 39 данных, первый регистр 40 данных, первый элемент И 41, регистр 42 адреса, второй элемент И 43, первый регистр 44 результата, первый 45 и второй 46 узлы синхронизации, третий элемент И 47, универсальный ком- бинационньй сумматор 48, четвертый элемент И 49, второй регистр 50 ре- зультата, второй предварительный регистр 51 данных, второй регистр 52 данных, пятый элемент И 53, запоминающее устройство (ЗУ) 54 тестовых программ, закольцованные сдвигающие регистры 55,-55 с последовательной .выдачей, шестой элемент И 56, одноразрядный регистр 57 признака, регистр 58 кода операции, первый элемент ИЛИ 59, седьмой элемент И 60, трехразрядный регистр 61 признака, элемент НЕ 62, регистр 63 команды, элемент 64 сравнения, регистр 65 номера арифметического блока. При этом

входы арифметического блока 8 подключены к информационным входам регистра 39, управляющий вход которого подключен к управляющему входу регистра 51 и выходу узла 45 синхронизации, информационные выходы регистров 39 и 51 подключены к информационным входам регистров АО и 52 соответственно, а управляющие выходы регистров 39 и 51 - соответственно к первому и второму входам узла 46 синхронизации,.выход которого подклчен к управляющим входам регистров 40 и 52, к тактируюпщм входам ре- гистров 55,-55 ЗУ 54 и первому входу элемента И 47, второй вход которого подключен к выходу одноразрядного регистра 57, а выход - к управляющему входу регистра 58, выходы которого подключены к управляющим входам комбинационного сумматора 48, первые и вторые входы операндов которого подключены к выходам элементов И 41 и 53 соответственно, причем первые входы элементов И 41 и 53 подключены соответственно к выходам регистров 40 и 52, а их вторые входы - к первым и вторым выходам регистра 61, при этом первый выход последнего подключен к первому входу элемента И 43, первому входу узла 45 синхронизации и третьему входу узла А6 синхронизации, второй выход этого регистра - к первому входу элемента И 49, к второму входу узла 45 синхронизации и к четвертому входу узла 46 синхронизации, вторые входы элеметов И 43 и 49 подключены к информационному выходу комбинационного сумматора 48, который также подключен к регистру 42 адреса, соединенному с выходом 10 арифметического блока, а их выходы - к входам регистров 44

И 50 соответственно, управляющие выходы которых подключены к третьему и соответственно четвертому входам узла 45 синхронизации, а информационные - к соответствующим информационным выходам арифметического блока 8, при этом управляющий вход регистра 42 подключен к первому выходу регистра 63, второй выход которого подключен к входу регистра 61, третий вы45

50

Поле НЭ служит для указания номера арифметического блока, для, которого предназначается данная команда Поле КОП используется для задания кода операции, на выполнение которой настраивается данный арифме.Г тический блок. Список возможных операций, на выполнение которых может быть настроен арифметический блок, включает операции пересылок, арифметические, логические и разовые операции, операции условных переходов. Поле ПС используется для управления подачей сигналов начала выполнения операций. При ненулевом значении ПС выполнение операций начинается после окончания записи операндов на выходные регистры 40 и 52 при наличии сигнала разрешения, который является для комбинационного сумматора 48 синхронизирующим

При ненулевом значении ПС синхронизирующий сигнал игнорируется, Поле

ход которого подключен к первому вхо- 55 используется для задания характера ду элемента И 60 и входу элемента обмена следующим образом:

5

10

20

ig339546

НЕ 62, выход которого подключен к первому вх оду элемента И 56, второй вход которого подключен к выходам сдвигающих закольцован1а1х регистров 55,-554 и ЗУ 54, а выход - к первому входу элемента ИЛИ 59, выход которого подключен к входу регистра 58, а второй вход - к выходу элемента И 60, второй вход которого подключен к третьему выходу регистра 63, четвертый выход которого подключен к входу одноразрядного регистра 57, причем информационный вход регистра 63 подключен к входу 34 и первому входу элемента 64, второй вход которого подключен к выходу регистра 65, а выход - к управляющему входу регистра 63, информационные входы регистров 55(-554 блока 54 подключены к вхо- ДУ 12о

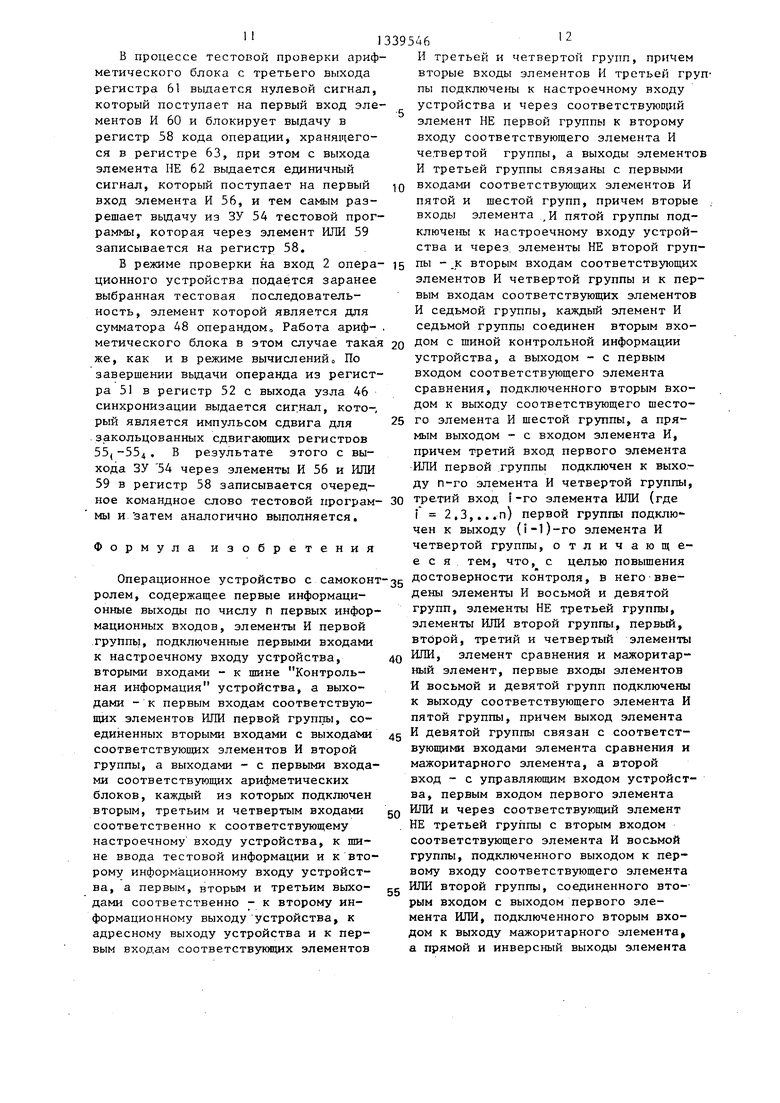

Формат команды () предусматривает пять полей: НЭ - поле номера арифметического блока 8, КОП - код

25 операции, ПС - поле запрета (разрешения) сигналов начала операции, на выполнение которой настроен данный арифметический блок, ПВ - поле выбора, А - адресное поле, ПК - поле коммутации.

30

Поле НЭ служит для указания номера арифметического блока, для, которого предназначается данная команда Поле КОП используется для задания кода операции, на выполнение которой настраивается данный арифме.Г тический блок. Список возможных операций, на выполнение которых может быть настроен арифметический блок, включает операции пересылок, арифметические, логические и разовые операции, операции условных переходов. Поле ПС используется для управления подачей сигналов начала выполнения операций. При ненулевом значении ПС выполнение операций начинается после окончания записи операндов на выходные регистры 40 и 52 при наличии сигнала разрешения, который является для комбинационного сумматора 48 синхронизирующим

При ненулевом значении ПС синхронизирующий сигнал игнорируется, Поле

в

1339546

, операция выполняется с

использованием адресного поля;

101, операция выполняется с использованием коммутационного поля;

111, операция выполняется с использованием адресного и . комм утационного полей;

100, разовые операции (тестовые команды)о

Адресное поле используется для задания адреса при выполнении адресных командо

Поле коммутации ПК используется для коммутации арифметического блока в модуле операционного устройства с В этом поле задаются сигналы, которые при расшифровке команды поступают на входы 35,-38,; ,; 35з-38з.

Устройство работает следующим образом.

Перед началом работы на вход 5 операционного устройства подаются управляющие сигналы и команды,, соответствующие программе выполнения функции f, о В случае использования косвенного контроля модуля операционного устройства на вход 6 устройства подается сигнал О, С помощью управляющих сигналов.

,;

поступающих на 34

вхо ды 34|-37, , - j,, t, операционном устройстве происходит выделение контрольных и рабочих арифметических блоков. Коммутации рабочих арифметических блоков 8 операционного устройства также определя ются-управляющими cигнaлa И, посту- пгуощимн на входы 35,-38,; .; , В таблиде даны знач ения управляющих сигналов, подаваемых на эти входы для выделения конт- рольных и рабочих арифметических блоков модуля 1 и задания режима боты рабочих арифметических блоков (параллельный или последовательный) , Контрольные арифметические блоки не- пользуются для косвенного контроля модуля, так как наличие корреляционных связей между отказами различных долей кристалла модуля делает возможным применение косвенного контрол

I

При контроле модуля соответствующи;е контролыше арифметические блоки 8 используются для выполнения тесто

I

вой программы. На вход 2 подается

контрольная информация, которая через соответствующие элементы И 3 и ИЛИ 7 поступает на вход арифметического блока 8, являющегося контрольным для модуля данного операционного устройства С выхода контрольного арифметического блока 8 информация через соответствующие элементы И 13 и ИЛИ 17 попадает на вход элемента 20 сравнения, на другой вход которого с входа 2 через элемент И 19 также поступает контрольная информация, В случае совпадения информации данный модуль расценивается как исправный, и с прямого выхода элемента 20 сравнения выдается 1, а с инверсного - О, В состоянии исправности на входы элемента И 21 поступает 1, которая через элемент ИЛИ 22 выдается на выходы 23, при этом на входы элемента ИЛИ 24 поступает О, который через элемент ИЛИ 23 проходит на выход 26 о В случае несовпадения информации данный модуль расценивается как неисправный, и с прямого выхода элемента 20 сравнения выдается О, который через элементь И 21 и ИЛИ 22 поступает на выход 23, а с инверсного выхода элемента 20 сравнения выдается 1, которая через элементы ИЛИ 24 и 23 поступает на выход 26 Выходы 23 и 26 -операционного устройства используются для индикации его состояния исправности

Тестовая программа, используемая для контроля контрольных арифметических блоков 8 модуля 1J выполняется независимо от штатной работы арифметических блоков 8 данного операционного устройства Способы построения тестовых программ могут быть различными, В частности, тестовая программа может быть сравнима по своей сложности с контрольной проверочной программой ЦВМ (охватывая все узлы контрольных арифметических бло- ков операционного устройства)о Достоверность косвенного контроля модуля 1 пропорционально зависит от числа контрольных арифметических блоков модуля, а именно: чем больше арифметических блоков контролируется, тем вьше достоверность контроля всего модуля 1 о

При организации параллельного функционирования рабочих арифметических блоков 8 входная информация , с первых информационных входов операционного устройства через соответствующие элементы И 4, у; (где К 1, 2,3) и ИЛИ УК поступает на входы арифметических блоков 8, с выходов которых информация через элемен-20 ществляется блокировка вьщачи результы И 13

и и ID к поступает на .входы соответствующих элементов И 28 и 29ц, и, поскольку с управлякяцего входа 6 подается О, блокирующий элемент И 29 , информация с выхода .элемента И через элементы И 28ц и ИЛИ 31) вьщается на первые информационные выходы операционного устройствао В этом случае в операционном устройстве может выполняться параллельная поразрядная обработка входного слова, соответствующая какой- либо элементарной операции при выполнении потоковой функции

При организации последовательного функчионировання арифметических блоков 8 операционного блока устройства входная информация через элементы

25

тата вычисления с выхода арифметических блоков в первые информационные выходы операционного устройства через элементы И 28,-28., и производится выдача результатов вына

числения через элементы И 29, -29.J соответствующий вход мажоритарного элемента 32, с выхода которого результат вычислений через элементы

30 ИЛИ 33 и 31,-31з выдается на первые информационные выходы операционного устройства. При этом в случае несовпадения результатов вычислений выдаваемых с арифметических блоков

35 8,-83, операционное устройство рас- ценивается как отказавшее, с прямого и инверсного выходов элемента 30 сравнения вьщаются соответственно сигналы 1 и О, которые через элеИ 4,, и ИЛИ 7, поступает на

рабочего арифметического блока и

вход

8,

с выхода которого информация через элементы И 14 ц и РШИ 7 к поступает на вход следующего рабочего арифметического блока 8, информация с выхода последнего рабочего арифметического блока 8 через элементы И 13, 16, 28 и ШШ 31 выдается на соответствующий первый информационный выход операционного устройства о В этом случае в последнем может быть выполнена более сложная последовательная обработка входного, слова, соответствующая какой-либо операции при выполнении потоковой функции

Кроме того, в устройстве предусмотрена возможность контроля операционного устройства, которая является более эффективным, чем косвенный контроль при малой степени коррели- рованности отказов При мажоритарном контроле реализуется однопотоковая обработка информации, когда одна и та же информация обрабатывается параллельно и независимо на трех (в данном случае) арифметических блоках 8,-8з, выходы которых подключены через соответствующие элементы И 29 к входам мажоритарного элемента 32, При этом на входы 35,36, 37, 38 зтветстз

I 1 II II 1 II Мои II 1 II

1 , -Л , и , 1 ,

торых осуществляется параллельная и независимая работа арифметических блоков . На вход 6 подается сигнал 1, с помощью которого осуч - к подаются соответственно сигналы 1, .1, О, 1, с помощью ко

тата вычисления с выхода арифметических блоков в первые информационные выходы операционного устройства через элементы И 28,-28., и производится выдача результатов вына

числения через элементы И 29, -29.J соответствующий вход мажоритарного элемента 32, с выхода которого результат вычислений через элементы

ИЛИ 33 и 31,-31з выдается на первые информационные выходы операционного устройства. При этом в случае несовпадения результатов вычислений выдаваемых с арифметических блоков

8,-83, операционное устройство рас- ценивается как отказавшее, с прямого и инверсного выходов элемента 30 сравнения вьщаются соответственно сигналы 1 и О, которые через элементы ИЛИ 22 к 25 попадают на выходы 23 и 26 операционного устройства При совпадении результатов вычи.сле- ний арифметических блоков 8/ -8j операционное устройство расценивается как исправное, с прямого и инверсного выходов элемента 30 сравнения выдаются соответственно сигналы О и 1, которые через элементы ИЛИ 22 и 25 попадают на выходы 23 и 26 операционного устройства.

Арифметический блок 8 работает следующим образом.

Перед началом штатной работы в регистр 65 заносится математический номер данного арифметического блока, через вход 12 в блок 54 записывается тестовая программа так, что в первых разрядах регистров 55,-554 со55

держится первое командное слово прогр ам я 5 второе и т.д„ В процессе штатной работы через вход 34 на регистр 63 записывается команда, при этом на первый вход элемента 64 сравнения поступает информация, содержао1а яся в поле НЭ данной команды При совпадении номера, записанного в регистре 65 и номера, содержащегося в поле НЭ, с выхода элемента 64 сравнения на управляющий вход регистра 63 выдается сигнал, который является разрешающим для вьщачи команды, записанной в регистре 63 на дальнейшее исполнение о В противном случае команда игнорируется о

При наличии только разрешающего сигнала с выходов регистра 63 выдает- ся содержимое полей ПС, КОП, ПВ и А данной команды а Б режиме, вычислений с третьего выхода регистра 61 выдается единица, которая открывает элемент И 60, и код операции через элементы И 60 и ИПИ 59 проходит на регистр 58, при этом с выхода НЕ 62 на первые входы элементов И 56 поступает нулевой сигнал, который блокирует выдачу тестовой информации из ЗУ 54 тестовых программ через элементы ИЛИ 59 в регистр 58о Входной операнд, поступающий из соседнего АУ, принимается на регистр 52, а информация, поступающая с входа 9 - на регистр 39, после чего при наличии разрешающего сигнала, вызываемого с выхода узла 45 синхронизации, с выходов регистров 39 и 51 соответственно на первый и второй входы узла 46 синхронк(зации

вьщается сигнал окончания приема one- Q зуется при формировании диаграммы в рандов, а информация, записанная в адресных командах, при этом выдача

этих регистрах, переписывается соответственно в регистры 40 и 52, откуда, при наличии разрешающего сигнала, вьщаваемого с выхода узла 46 синхро - низации, информация через элементы И 41 и 53 соответственно поступает 3 универсальный комбинационный сумматор 48о При этом сигнал, вьодаваемый узлом 46 синхронизации через элемент И 47 поступает на управляющий вход регистра 58, с выхода которого код операции поступает на командные входы комбинационного сумматора 48,, после чего производится необходимая операция о

При наличии вьщача сигнала с выхода элемента И 47 блокируется.. Подобная возможность расценивается

как необходимая при организации операций ожидания по условию. При с второго выхода регистра 61 выдается

нулевой сигнал, который поступает на первый вход элемента И 49 и на второй вход элемента И 53, тем самым блокируются поступление информации на сумматор 48 из соседнего арифметического блока и выдача результата обра- ботки через регистр 50 в следующий за ним арифметический блок С первого выхода регистра 61 выдается единичный сигнал, который поступает на первый вход элемента И 43 и на второй вход элемента И 41, тем самым разру-- , шаются поступление информации на сумматор 48 и. выдача результата обработки через регистр 44 на выход 11 АУ„ Кроме того, с помощью сигналов, вьщаваемых с первого и второго выходов регистра 61, формируется временная диаграмма работы узлов 45 и 46 синхронизации фиг о 4 и 5) соответственно.

Аналогично при происходят разрешение приема обрабатываемой информации на сумматор 48 из соседнего АУ и выдача результата обработки в следующий за ним арифметический блок, при этом блокируются пути приема информации, поступающей с выхода 9 и выдача результата на вход 11. Прием входных операндов из соседнего

арифметического блока, а также на

вход 9, и вьщача результатов в следующий арифметический блок, а также на выход 1 1 могут быть реализованы при . Регистр 42 адреса исполь

5

адреса с него осуществляется через выход 10 арифметического блока. По окончании выполнения операции с выхода сумматора 48 результат через элементы И 49 и: 43 и в зависимости от признака ПВ записывается в регистры 44 и 50 соответственно. По завершении записи с управляющих выходов регистров 44 и 50 на входы узлов 45 синхронизации, временная диаграмма работы которого формируется с помощью признака ПВ, поступают единичные сигналы. При этом с выхода узла g 45 вьщается разрешающий сигнал, который поступает на управляющие входь: регистров 39 и 51. В результате этого, из регистров 39 и 51 происходит выдача очередных операндов.

0

метического блока с третьего выхода регистра 61 выдается нулевой сигнал, который поступает на первый вход элементов И 60 и блокирует выдачу в регистр 58 кода операции, хранящегося в регистре 63, при этом с выхода элемента НЕ 62 вьщается единичный сигнал, который поступает на первый вход элемента И 56, и тем самым разрешает выдачу из ЗУ 54 тестовой программы, которая через элемент ИЛИ 59 записывается на регистр 58.

В режиме проверки на вход 2 опера- 15 пы -.к вторым входам соответствующих ционного устройства подается заранее элементов И четвертой группы и к пер- выбранная тестовая последовательвым входам соответствующих элементов И седьмой группы, каждый элемент И седьмой группы соединен вторым вхоность, элемент которой является для

вым входам соответствующих элементов И седьмой группы, каждый элемент И седьмой группы соединен вторым вхосумматора 48 операндом. Работа ариф- . метического блока в этом случае такая 20 шиной контрольной информации же, как и в режиме вычислений По устройства, а выходом - с первым завершении вьщачи операнда из регист- входом соответствующего элемента

сравнения, подключенного вторым входом к выходу соответствующего шесто- 25 го элемента И шестой группы, а прямым выходом - с входом элемента И, причем третий вход первого элемента ИЛИ первой группы подключен к выхора 51 в регистр 52 с выхода узла 46 синхронизации выдается сиг.нал, кото-, рый является импульсом сдвига для .закольцованных сдвигающих регистоов 55( -55, В результате этого с выду п-го элемента И четвертой группы.

хода ЗУ 54 через элементы И 56 и ИЛИ 59 в регистр 58 записывается очередное командное слово тестовой програм- 30 третий вход i-го элемента ИЛИ (где мы и затем аналогично выполняется, i 2,3,...п) первой группы подключен к выходу (i-l)-ro элемента И

Формула изобретениячетвертой группы, отличающееся тем, что, с целью повышения

Операционное устройство с самоконт-з5 Достоверности контроля, в него вве- ролем, содержащее первые информаци- дены элементы И восьмой и девятой онные выходы по числу п первых информационных входов, элементы И первой группы, подключенные первыми входами к настроечному входу устройства, вторыми входами - к шине Контрольная информация устройства, а выходами - к первым входам соответствующих элементов ИЛИ первой группы, соединенных вторыми входами с выхода Ми 45 Девятой группы связан с соответст- соответствующих элементов И второй вующими входами элемента сравнения и группы, а выходами - с первыми входа- мажоритарного элемента, а второй

групп, элементы НЕ третьей группы, элементы ИЛИ второй группы, первый, второй, третий и четвертый элементы 4Q ИЛИ, элемент сравнения и мажоритарный элемент, первые входы элементов И восьмой и девятой групп подключены к выходу соответствующего элемента И пятой группы, причем выход элемента

ми соответствующих арифметических блоков, каждый из которых подключен вторым, третьим и четвертым входами соответственно к соответствующему настроечному входу устройства, к шине ввода тестовой информации и к второму информационному входу устройства, а первым, вторым и третьим выхо- gg ИЛИ второй группы, соединенного вто-дами соответственно - к второму информационному выходу устройства, к адресному выходу устройства и к первым входам соответствукицих элементов

вторые входы элементов И третьей группы подключены к настроечному входу устройства и через соответствуюпшй элемент НЕ первой группы к второму входу соответствующего элемента И четвертой группы, а выходы элементов И третьей группы связаны с первыми входами соответствующих эле-ментов И пятой и шестой групп, причем вторые входы элемента и пятой группы подключены к настроечному входу устройства и через элементы НЕ второй группы -.к вторым входам соответствующих элементов И четвертой группы и к пер-

вым входам соответствующих элементов И седьмой группы, каждый элемент И седьмой группы соединен вторым шиной контрольной информации устройства, а выходом - с первым входом соответствующего элемента

ду п-го элемента И четвертой группы.

третий вход i-го элемента ИЛИ (где i 2,3,...п) первой группы подключен к выходу (i-l)-ro элемента И

Достоверности контроля, в него вве- дены элементы И восьмой и девятой Девятой группы связан с соответст- вующими входами элемента сравнения и мажоритарного элемента, а второй

групп, элементы НЕ третьей группы, элементы ИЛИ второй группы, первый, второй, третий и четвертый элементы ИЛИ, элемент сравнения и мажоритарный элемент, первые входы элементов И восьмой и девятой групп подключены к выходу соответствующего элемента И пятой группы, причем выход элемента

вход - с управляющим входом устройства, первым входом первого элемента ИЛИ и через соответствующий элемент НЕ третьей группы с вторым входом соответствующего элемента И восьмой группы, подключенного выходом к первому входу соответствующего элемента

рым входом с выходом первого элемента ИЛИ, подключенного вторым входом к выходу мажоритарного элемента, а прямой и инверсный выходы элемента

сравнения связаны с первыми входами соответственно второго и третьего элементов ИЛИ, выходы которых являются управляющими выходами устройства, а вторые входы подключены к выходам соответственно элемента И и четвертого элемента ИЛИ, соединенного входами с инверсными выходами, элементов сравнения группы, выходы элементов И второй группы являются первьми информационными выходами устройства .

72

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное вычислительное устройство | 1984 |

|

SU1203506A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для реализации подстановок | 1989 |

|

SU1683025A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Операционное устройство микропроцессора | 1979 |

|

SU1164719A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при создании устройств для обработки цифровых данных. Цель изобретения - повышение достоверности контроля устройства Устройство содержит шину 2 контрольной ин33 п (Л СлЭ 00 СО ел 35

ф1/г.З

ПР1

w//y//////

vy/////////A

прг

i /7flf//7d-ff7/

t ffpt// e: fff

фиг Л

t fjpl/ /7 --///

цзиг.5

inpu/7e ff1

фиг. 6

Редактор И„Горная

Составитель Но Горбунова Техред М.Хода нич

Заказ 4222/38 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,,,

Производственно-полиграфическое предприятие, г Ужгород, ул.Проектная,4

Корректор А.Обручар

Авторы

Даты

1987-09-23—Публикация

1986-02-24—Подача