Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств для обработки данных.

Цель изобретения - повьшение производительности устройства.

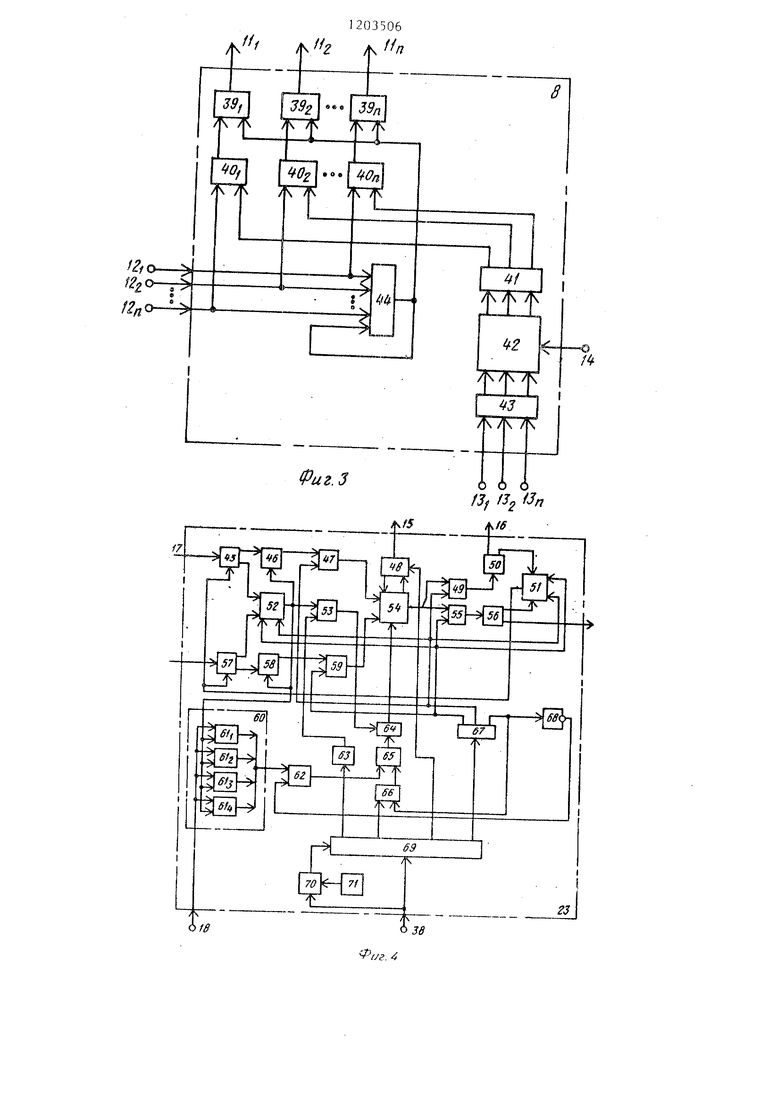

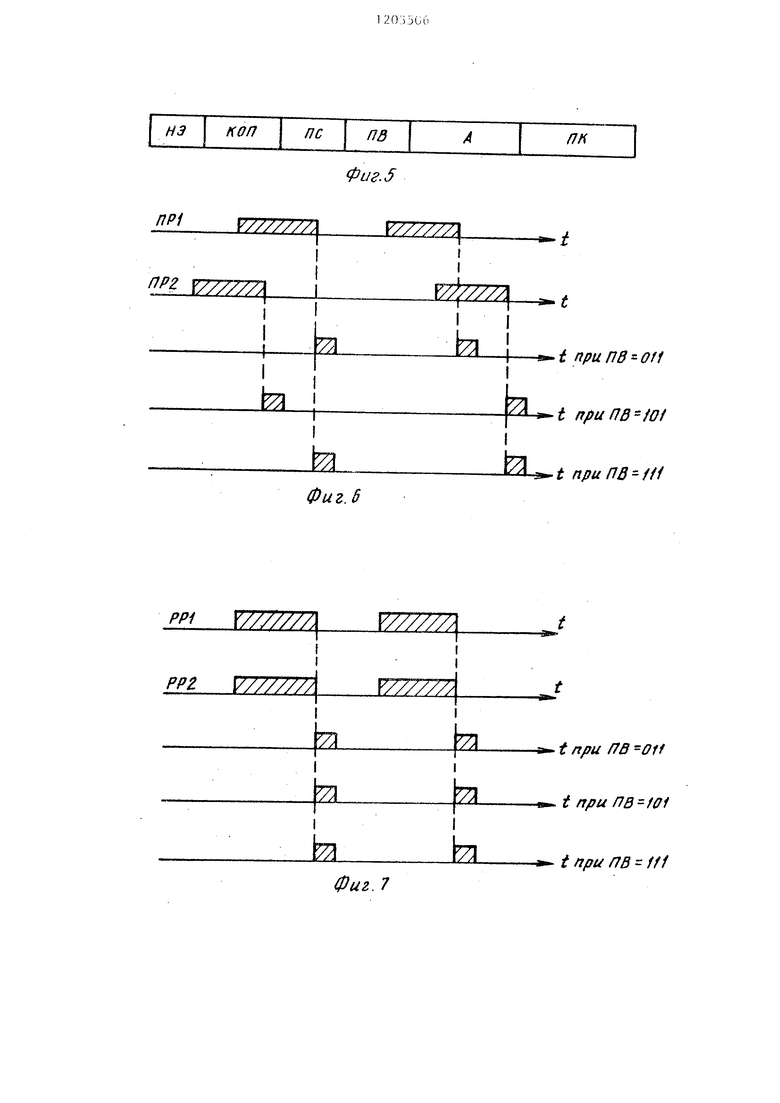

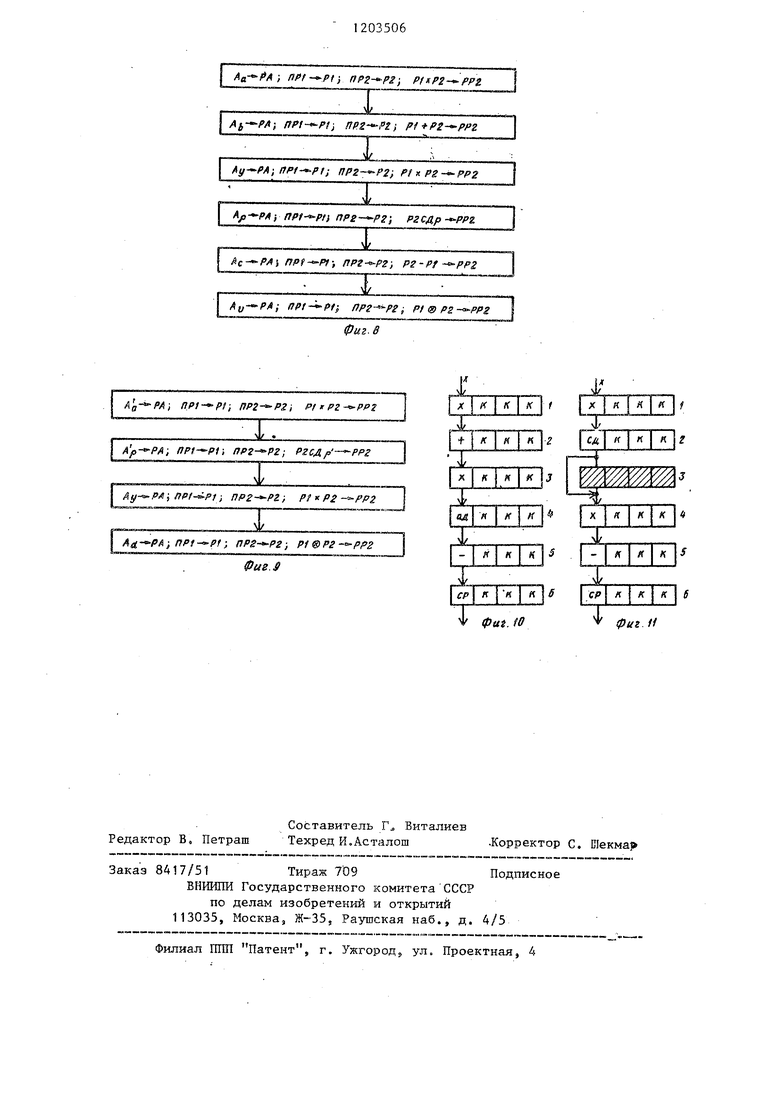

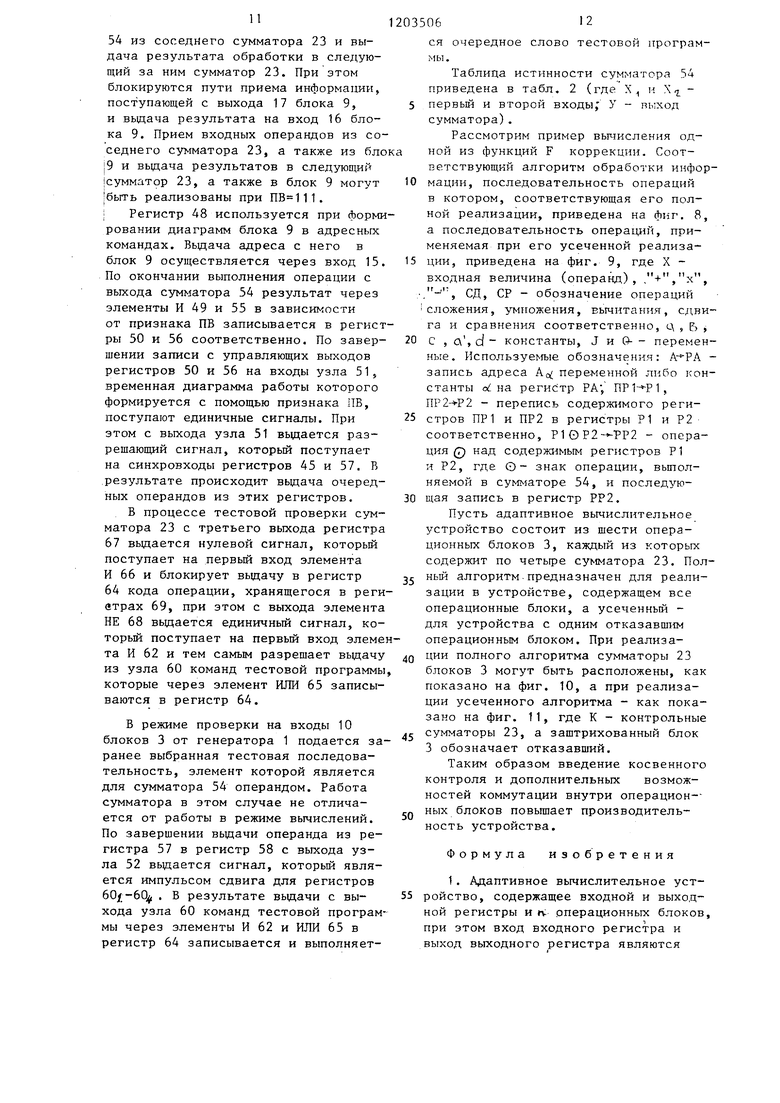

На фиг. 1 представлена структурная схема устройства5 на фиг. 2 - функциональная схема операционного блока; на фиг. 3 - функ1щональная схема блока микропрограммного управления; на фиг. Д - функциональная схема сумматора , на фиг. 5 - формат, команды; на фиг. 6 и 7 - временные диаграммы узлов синхронизации сумматора, на фиг. 8 - последовательность операп,ий, соответствующая реализация полного алгоритма коррекции , на фиг, 9 - последовательность операций, соответствующая реализации усеченного алгоритма коррекции;,на фиг. 10 - вариант реализации полного алгоритма коррекции в устройстве , на фиг. 11 - вариант реализации усеченного алгоритма коррекции в случае

отказа одного модуля устройства,

1

Адаптивное вычислительное устройство (фиг, 1) содержит генератор 1 импульсов, входной регистр 2, операционные блоки , первые группы

.элементов И , вторые группы элементов И ,, группы элементов ИЛИ , причем группы А-6 образуют соответствующие коммутаторы, выходной регистр 7, блок 8 микропрограммного управления, блок 9. памяти данных и имеет синхровходы операционных блоков, входы 11 - 11j кода операции операционных блоков, первые выходы ( признака результата операционных блоков, вторые выходы признака результата операционных блоков, вход 14 ввода программ, адресный 15 и информационный 16 входы блока 9, информационный выход 17 блока 9 и информационный вход 18 устройства. Выходы регистра 2 подключены к первым информационным входам блока и первым входам элементов И 5;( , выход генератора 1 подключен к входам (- бло- ков ,, входы 11,-11. которых соединены с одноименными выходами блока 8. Выходы , подключены к вторым входам одноименных элементов И ,и входам пуска блока 8, выходы подключены к вторым входам одноименных элементов И

03506

и входам логических условий блока 8 Первые информйДйонные выходы блоков 3j (1 ) подключены к первым входам элементов И А , выходы кото--5 рых подключены соответственно к первым входам элементов ИЛИ 6i, вторые входы которых соединены с выходами элементов И 5j , первые входы которых соединены с соответствующими

О первыми информационными входами бло-- ка 3 и выходом элемента ИЛИ (, (), выходы элементов ИЛИ 6 подключены к выходному регистру 7, Информационный вход 16, информацион 5 ный выход 17 и адресный вход 15 блока 9 подключены соответственно к вторым и третьим информационным выходам и вторым информационным входам операционных блоков 3j,-3p,. Генератор 1

20 является источником последовательно-, сти О, 1, О, 1,,,.. логических сигналов О или 1, предназначенных для проверки контролируемых операционных блоков.

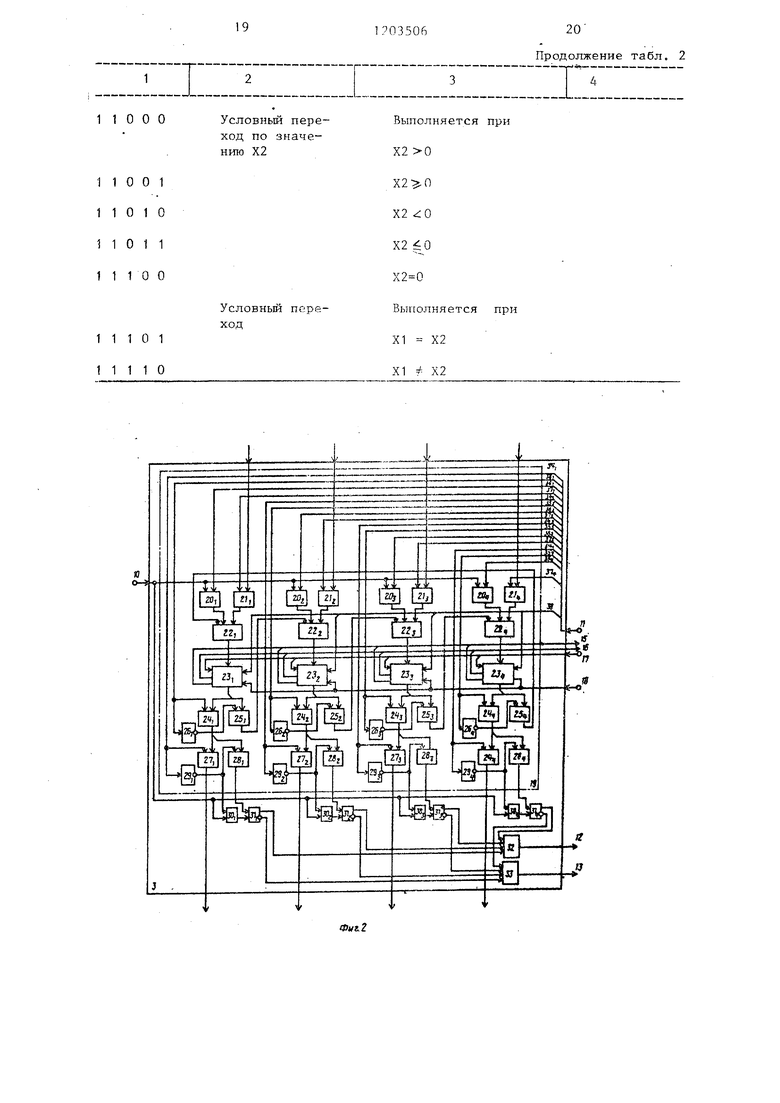

25 Операционный блок 3 (фиг. 2) состоит из модуля 19, выполненного в виде интегральной схемы, которьш в свою очередь содержит первую группу элементов И 20 t-20i,, вторую груп30 пу элементов И 21 -21 i, группу элементов ИЛИ , образующих группу коммутаторов данных, группу сум- маторив (5 третью группу элементов И ,, четвертую группу

;)5 элементов И 25/ -25ц , первую группу элементов НЕ , образующих пер вую группу коммутаторов результата, пятую группу элементов И 27, -27iy , шестую группу элементов И 28/|-28i,

40 вторую группу элементов НЕ 29,-29ц, образующих вторую группу коммутаторов результата , седьмую группу элементов И (, группу элементов 31., -31i равнозначности и два элемен45 та И 32 и 33. Коммутация рабочих сумматоров 23 определяется управляющими сигналами 34-38.

Блок 8 микропрограммного управления (фиг. 3) содержит перв.ую группу

элементов И 39,,-39(,, вторую группу элементов И 40.j-40j,, регистр 41 настройки, память 42 микрокоманд, регистр 43 состояния, триггер RS-типа 44, Входы 12,,-12ti пуска блока 8 под55 ключены к первым входам элементов И соответственна, а также к одноименным информационным входам триггера 44, выход которого подкяю3

чен к его синхровходу н nepiibiM входам элементов И , вторые входы которых подключены соответственно к выходам элементов , вторые входы которых подключены к выходам регистра 41. Входы регистра 41 подключены к информационным выходам .памяти 42 микрокоманд, входы которой подключены к входам логических условий блока 8.

Сумматор 23 содержит (фиг. 4) первый пре варительньй регистр 45 данных (ПР1), nepBbtti регистр 46 данных (Р1), первый элемент И 47, регистр 48 адреса, второй элемент И 49, лер- вьй регистр 50 результата (РР1), первый узел 51 синхронизации, второй узел 52 синхронизапии, третий элемент И 53, универсальный комбинационный сумматор 54, четвертый элемент И 55, второй регистр 56 результата (РР2), второй предварительный регистр 57 данных (ПР2), второй регистр 58 данных (Р2), пятьш элемент И 59, узел 60 памяти, кольцевые сдвиговые регистры 61-y-61(t/ с последовательной вьщачей, шестой элемент И 62 одноразрядный регистр 63 признака, регистр 64 кода операции, первый элемент РШИ 65, седьмой элемент И 66, трехразрядный регистр 67 признака, элемент-НЕ 68, регистр 69 команды, элемент 70 равнозначности, регистр 7 номера сумматора.

При этом входы 17 блока 23 подключены к информационным входам регистра 45, синхровход которого подключен к синхровкоду регистра 57 и выходу узла 51. Информационные выходы регистров 45 и 57 подключены к информационным входам регистров 46 и 58 соответственно, а управляющие выходы регистров 45 и 57 подключены к первому и второму входам узла 52 соответственно . Выход узла 52 подключен к синхровходам регистров 46 и 58, тактирующим входам регистров 61у-61и блока 60 и первому входу элемента И 53. Второй вход элемента И 53 подключен к выходу регистра 63, а выход - к синхровходу регистра 64, выходы которого подключены к управляющим входам сумматора 54, первые и вторые входы операндов которого подключены к выходам элементов И 47 и 59 соответственно. При этом первые входы элементов И 47 и 59 подключены соответственно к выходам регистров

П350Г1

4Ь р :;8, а кх вторые входы - к пер- ЕЫ и вторым Е ;оц,-м регттстра 67. Первый вьгход реги, тг,- о7 ночк.гп-г чен к первому входу ,4iCMo::i a И 49, гервому вхо5 ду узла 51 и третьему входу узла 52, а второй выход регистра подключен к первому Еходу элемента И 55, второму входу узла 51 и гетвертому йкоду узла 52.

0 Вторые вхс,-.ц-ы элементов И 49 и 55 подключены к информашюнному выходу сут-1матора 54, который также подключен к регистру 48 адреса, соединенному с выходом 15 сумматора 23,

15 а их выходы - к входам регистров 50 к 56 соответственно. Управляю1цие выходы регистров 50 и 56 подключены к третьему и четвертому входам узла 51 соответственно, а их информацион0 Hbie выходы - к соответствуюптим информационным выходам сумматора 23, При этом синхровхпд регистра 48 подключен к первому выходу регистра 69, второй выход которого подключен к

5 входу регистра 67, третий выход кото- роге подключен к первому входу элемента И 66 и ЕХОДУ элемента НЕ 68, Выход элемента НЕ 68 подключен к первому входу элемента И 62, второй

0 вход которого подключен к выходам регистров , блока 60, а вьгход- к первому входу элемента ИЛИ 65. Выход элемента ИЛИ 65 подключен к входу регистра 64, второй вход - к выходу элемента И 66, второй вход ко5

0

5

торого подключен к третьему выходу регистра 69, четвертый выход которого подключен к входу регистра 63. Информационный вход регистра 69 подключен к входу 38 и первому входу элемента 70,второй вход которого подключен к выходу регистра 71, выход - к синхровходу регистра 69 а информационные входы регистров , блока 60 подклк чены к входу 18 устройства .

команды предусматривает пять полей: НЭ - поле номера сумма- тора 23, КОП - поле кода операции,

ПС - поле запрета/разрешения сигналов начала вьшолнения операции, на выполнение которой настроен сумматор 23; ПВ - поле выбора; А - адресное поле; ПК - поле коммутации. Поле

НЭ слуткит для указания номера сумматора 23, для которого предназначается данная команда. Поле КОП используется для зад.ания кода опера

,

111,

ции, на выполнение которой настраивается данный сумматор 23. Список возможных операций, на вьтолнение которых может быть настроен сумматор 23, включает операции пересылок (АУ АУ, ЗУ данных)5 арифметические, логические и разовые операции, операции условных переходов. Поле ПС используется для управления вьщачей сигналов начала выполнения операции. При не нулевом значении ПС выполнение начинается после окончания записи операндов на входные регистры 46 и 58 при наличии сигнала разрешения, которьш является для сумматора 54 синхронизирующим. При нулевом з.наче- нии ПС синхронизирующий сигнал игнорируется .

Поле ПВ используется для задания характера обмена следующим образом; 011, операция выполняется с использованием адресного поля, операция выполняется с использованием коммутационного поля,

операция выполняется с исползованием адресного и коммутационного полей, 100, разовые операции (тестовые

команды). Адресное поле используется для задания адреса при вьшолнении адресных команд (например, при умножении на константу, которая находится в блоке 9). Поле коммутации ПК используется для коммутации сумматора 23 в модуле 19. В этом поле задаются сигналы, которые при распшфровке команды поступают на входы 34-37.

Устройство работает следзтощим образом.

Перед началом работы в зави:9имо- сти от выполняемой функции F , .. .e блок 8 по входу 14 вводятся уп- равляющие сигналы и команды, соответствующие программе выполнения последовательности функции f ,..,., f. Данные команды с выходов блока 8 поступают на входы 11 соответствующих операционных блоков 3 3,..,, 3.. С помощью управляющих сигналов, поступающих на входы 34-37,, в каждом блоке 3 происходит выделение контрольных и рабочих сумматоров 23 Контрольные сумматоры 23 каждого модуля 19 используются для косвенного контроля данного модуля, так

0

5

0

5

О

5

5

0

как наличие корреляционных связей между отказами различных частей модуля делает возможным применение косвенного контроля. Комт 1утация рабочих сумматоров 23 блока 3 также определяется управляющими сиг 1алами, подаваемыми на входы 34-37.

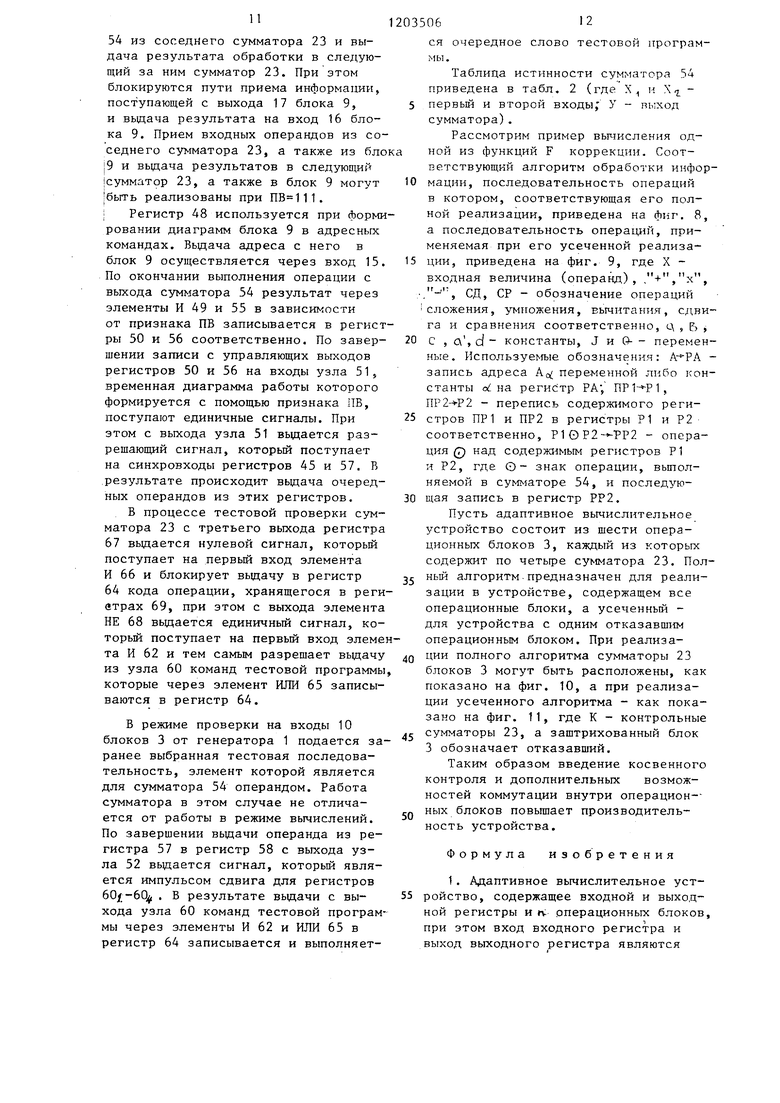

В табл. 1 приведены значения сигналов-, подаваемых на эти входы, для вьщеления контрольных и рабочих сумматоров 23 модуля и задания режимов их работы (параллельный или последовательный) .

С.помощью подачи различных управляющих сигналов на указанные входы могут быть вьщелены другие комбинации контрольных и рабочих сумматоров 23 и заданы различные режимы их работы. При контроле модуля 19 соответствующие контрольные сум1- аторы 23 используются для выполнения тестовой программы. На вход 10 с выхода генератора 1 подается тестовая информация, которая через соответствующие элементы И,20 и ИЛИ 22 поступает на входы блоков 23, являющихся контрольными для данного модуля, С выхода, контрольного сумматора 23 информация через соответствзпощие элементы И 24 и 28 попадает на первьш вход элеме};.та И 30, на второй вход кото- рог о с входа 10 через элемент И 30 также поступает тестовая информация.

В случае совпадения информации дан- ньш модуль рассматривается как исправный и с прямого выхода элемента ЗГ выдается 1, которая поступает на вход элемента И 32. При зтом с инверсного выхода элемента 3Г выдается О, который через элемент И 33 поступает на выход 13 блока 3. В слу- чае несовпадения информации данный модуль расценивается как неисправ- ньм и с прямого выхода элемента 31 вьщается О, который через элемент И 32 поступает на выход 12, при этом с инверсного выхода элемента 31 выдается 1, которая поступает на вход элемента И 33.

Тестовая программа, используемая для контроля проверяемых блоков мо- дуля 19, выполняется независимо от штатной работы рабочих сумматоров 23 данного блока 3. Способы построения тестовых программ могут быть различными. В частности, тестовая программа может быть сравнима по

/

сложности с контрольно-проверочной программой ЭВМ (охватывая все узлы контрольных су 1маторов 23 операционного блока 3). Достоверность косвенного контроля зависит от числа контрольных блоков модуля, вьиеленньк из общего количества сумматоров 23 модуля, а именно: чем больше сумматоров 23 контролируется, тем выше достоверность контроля всего модуля.

При организации параллельного функционирования рабочих сумматоров 23 к в блоке 3/1 входная информация через элементы И 2, и ИЛИ 22 поступает на вход рабочего сумматора 23Кэ с выхода которого информация через элементы И,.24(.и 27| выдается на информационные выходы блока 3, В этом случае в блоке 3, в частности может выполняться параллельная обработка входного слова, соответствующая какой-ли.бо элементарной операции при выполнении потоковой функции, Ан логично может быть организовано параллельное функционирование рабочих сумматоров 231, в любом другом операционном блоке устройства.

I

При организации последовательного

функционирования рабочих сумматоров i 23| в блоке 3 входная информация через элементы И 21 к, и ИЛИ 22к пает на вход рабочего сумматора 23 с выхода которого информация через элементы И 25| и ИЛИ 221 поступает на вход следующего рабочего сумматора ., а информация с выхода последнего рабочего сумматора 23г; через элементы И 24, и 27, вьщается на соответствуюпщй информационный выход блока 3. В этом случае в блоке 3-, может быть выполнена более сложная последовательная обработка входного слова, соответствующая какой-либо операции при вьтолнении потоковой функции. Аналогично может быть организовано последовательное функционирование рабочих сумматоров 23к в любом другом операционном блоке устройства.

В случае исправности блока 3 с выхода 12 этого блока вьдается 1, которая поступает на входы элементов И 4;,. Таким образом, выходной операнд, предварительно записанный во входном регистре 2, через элементы И 4j и ИЛИ 6{ последовательно проходит обработку в блоках ь. При

03506«

этом с выхода 13 вьщается О, который блокирует путь обхода блока З; ,

В случае возникновения отказа блока 3j с выхода 12 этого блока выда5 ется О, 1 оторьй поступает на входы элементов И 4j и блокирует вьвдачу информации с выхода данного блока . при этом с выхода 13 вьщается 1, которая поступает на входы элементов

О И 5д и тем самым открывает путь обхода отказавшего блока З,; , В результате информация с выхода блока ЗL- через элементы И , ЮТИ 6/--( , а затем через элементы И З и RiTH

15 попадает на входы блока 3 +;,

Блок 8 работает следующим образом. При отсутствии отказов на ин- формационные входы триггера А4 и пер- Еые входы элементов И поступают 1. При этом на входы (п блока 8 поступают О, которые записы- Баются в регистр 43. Содержимое регистра 43 интерпретируется как ад25 рее к поступает в- память 42 микроко- манд в которой по нулевому адресу записаны команды, соответствующие пути вычисления функции F в трех (в общем случае ft h) операционных блоках, С выходов памяти 42 комавды записываются в регистр 41, с выходов которого через элементы И 39 и 40 они поступают на входы 11.--ll. операционных блоков.

При возникновении отказа (напри35 мер, блока Зг) на .вход 12,j блока 8 и, соответствег но, на второй информационный вход триггера 44 поступает О, а с выхода триггера 44 выдается О, который поступает на

О вторые входы элементов И 39 -39vi. В результате на входы 11,-11 блоков 3 подается О, настройка блоков 3 сбрасывается и информация, находящаяся в этих блоках, разрушается. С

5 выхода триггера 44 по линии обратной связи О попадает на синхровход триггера, триггер 44 снова устанавливается в состояние 1 и на первые входы элементов И , поступает

50 1. При этом на вход 13 блока 8 поступает 1, в соответствующий разряд регистра 43 записывается 1 и содержимое регистра 43, интерпретируемое как адрес, поступает на

55 вход памяти 42, с выхода которой команды, соответствующие пути в,ычисле- ния функции F в двух исправных операционных блоках, поступают на вход

30

регистра настрсчйки. Кроме того, на первый вход элемента И 40, также поступает О, который блокирует выдачу команды и управляющих сигналов с соответствующих разрядов регистра 41 на входы 11 отказавшего блока 3i. Та

ким образом, при отказе какого-либо блока 3 происходит обращение к ячейке памяти 42, в которой записаны команды, соответствующие пути вычисления функции F при данном отказе. Перед началом работы по входу 14 в память 42 осуществляется запись команд, соответствующих путям вычисления функции F при различных отказах.

Сумматор 23 работает следующим образом. Перед началом штатной работы в регистр 71 заносится математический номер данного сумматора, через вход 18 в узел 60 записывается тестовая программа таким образом, что в первых разрядах регистров , содержится первое командное слово программы, во вторых - второе и т.д. В процессе штатной работы через вход 38 на регистр 69 записывается команда поступающая из памяти 42, при этом на первый вход элемента 70 поступает информация, содержащаяся в поле НЭ данной команды. При совпадении номе- ра, записанного в регистре 71, и номера, содержащегося в поле НЭ, с выхода элемента 70 на вход регистра 69 выдается сигнал, который является разрешающим для выдачи команды, записанной в регистре 69, для дальнейщего исполнения. В противном случае команда игнорируется. При наличии такого разрешающего сигнала с выходов регистра 69 выдается содержимое полей ПС, КОП, ПВ и А данной команды.

Адрес, содержащийся в команде, с первого выхода регистра 69 записывается в регистр 48. Информация, соответствующая полю ПВ, с второго выхода регистра 69 поступает на регистр 67. Информация, соответствующая полю КОП, с третьего выхода регистра 69 через элементы ИЛИ 65 и И 66 поступает на регистр 64. Информация, соответствующая полю ПС, с четвертого выхода регистра 69 поступает на регистр 63.

В режиме вычислений с третьего выхода регистра 67 выдается 1, которая открывает элементы И 66 и код операции через элементы ИЛИ 65 и И 66 проходит на регистр 64, при этом с

s

0350610

выхода элемента НЕ 68 на первые входы элементов И 62 поступает нулевой сигнал, который блокирует вьщачу тестовой информации из узла 60 через элементы ИЛИ 65 в регистр 64. Входной операнд, поступающий из соседнего сумматора 23, принимается на регистр 57, а информация, поступающая из блока 9, - на регистр 45, после чего при наличии разрешающего сигнала, вьщаваемого с выхода узла 51, с выходов регистров 45 и 57 на первьш и второй входы узла 52 выдается сигнал окончания приема опе- 15 рандов. Информация, записанная в

этих регистрах, переписывается соответственно в регистры 46 и 58, откуда при наличии разрепиющего сиг10

нала, выдаваемого с выхода узла 52, информация через элементы И 47 и 59 соответственно поступает в сумматор 54. При этом сигнал, выдавае- мьш узлом 52, через элемент И 53 поступает на вход регистра 64, с выхода которого код операции выдается на входы команд сумматора 54, после чего производится необходимая операция .

При наличии выдача сигнала с выхода элемента И 53 блокируется Подобная возможность расценивается как ;;: ;обходимая при организации операций ожидания по условию. При с второго выхода регистра 67 выдается нулевой сигнал, которьш поступает на первьй вход элемента И 55 и на второй вход элемента И 59. Тем самым блокируется поступление информации в сумматоре 54 из соседнего сумматора 23 и вьщача результата обработки через регистр 56 в следую- дий за ним сумматор 23. С первого выхода регистра 62 выдается единичный сигнал,, которьш поступает на первый вход элемента И 49 и на второй вход элемента И 47, тем самым разрешается поступление информации в су1-{матор 54 и выдача результата обработки через регистр 50 на вход блока 8,

Кроме того, с помощью сигналов, выдаваемых с первого и второго выходов регистра 67, формируется временная диаграмма работы узлов 51 и 55 52, как показано на фиг. 6 и 7 соответственно. Аналогично при .происходит разрешение приемЗ обра- батьгеаемой информации сумматором

11

54 из соседнего сумматора 23 и выдача результата обработки в следующий за ним сумматор 23. При этом блокируются пути приема информации, поступающей с выхода 17 блока 9, и вьщача результата на вход 16 блока 9. Прием входных операндов из соседнего сумматора 23, а также из бл |9 и выдача результатов в следующий {сумматор 23, а также в блок 9 могут ;быть реализованы при . I Регистр 48 используется при формровании диаграмм блока 9 в адресных командах. Вьщача адреса с него в блок 9 осуществляется через вход 15 По окончании выполнения операции с выхода сумматора 54 результат через элементы И 49 и 55 в зависимости от признака ПВ записывается в регисры 50 и 56 соответственно. По завершении записи с управляющих выходов регистров 50 и 56 на входы узла 51, временная диаграмма работы которого формируется с помощью признака ПВ, поступают единичные сигналы. При этом с выхода узла 51 вьщается разрешающий сигнал, который поступает на синхровходы регистров 45 и 57. В результате происходит вьщача очередных операндов из этих регистров.

В процессе тестовой проверки сумматора 23 с третьего выхода регистр 67 выдается нулевой сигнал, который поступает на первый вход элемента И 66 и блокирует выдачу в регистр 64 кода операции, хранящегося в рег атрах 69, при этом с выхода элемент НЕ 68 выдается единичный сигнал, ко торьй поступает на первый вход элемта И 62 и тем самым разрешает вьвдач из узла 60 команд тестовой программ которые через элемент ИЛИ 65 записываются в регистр 64.

В режиме проверки на входы 10 блоков 3 от генератора 1 подается заранее выбранная тестовая последовательность, элемент которой является для сумматора 54 операндом. Работа сумматора в этом случае не отличается от работы в режиме вычислений. По завершении вьщачи операнда из регистра 57 в регистр 58 с выхода узла 52 вьщается сигнал, который является импульсом сдвига для регистров 60/-60 j, . В результате вьщачи с выхода узла 60 команд тестовой программы через элементы И 62 и ИЛИ 65 в регистр 64 записывается и выполняет12

ся очередное слово тестовой программы.

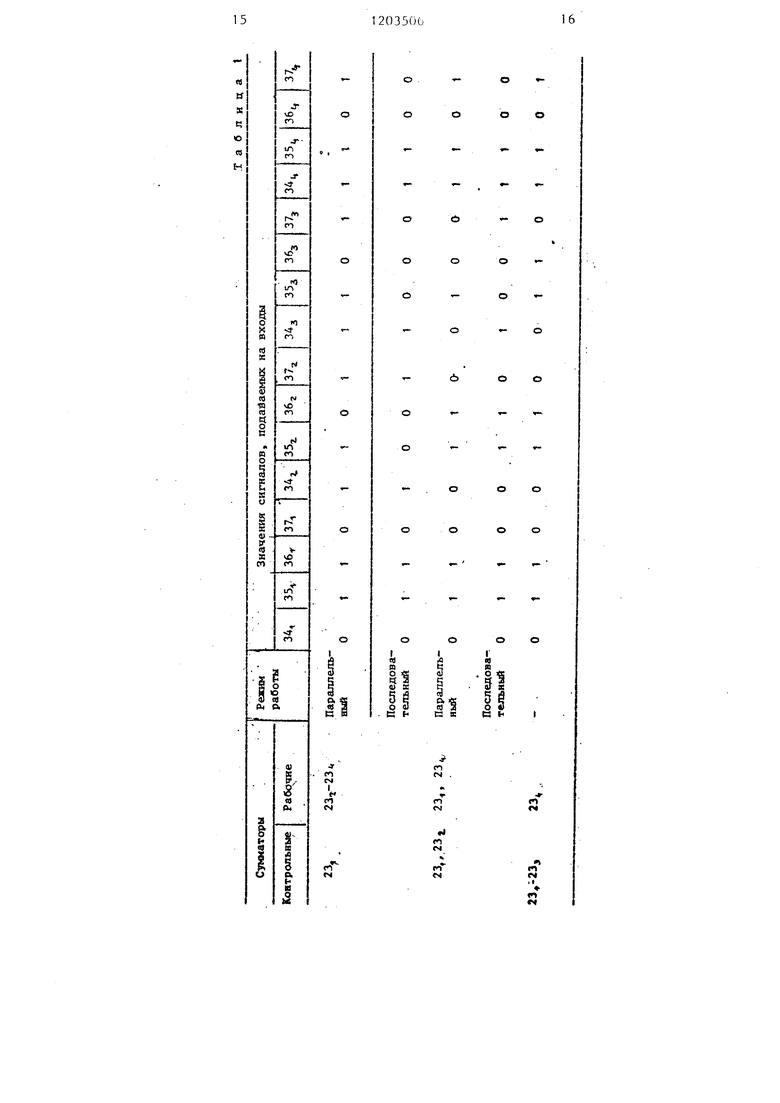

Таблица истинности сумматора 54 приведена в табл. 2 (где Х и - первый и второй входы, У - выход сумматора).

Рассмотрим пример вьтисления одной из функций F коррекции. Соответствующий алгоритм обработки информации, последовательность операций в котором, соответствующая его полной реализации, приведена на фиг. 8, а последовательность операций, применяемая при его усеченной реализации, приведена на фиг. 9, где X - входная величина (операнд), ,+,х, , СД, СР - обозначение операций сложения, умножения, вычитания, сдвига и сравнения соответственно, Q, Ь , С , а , d константы, J и О- - перемен- ньге. Используемые обозначения: - запись адреса АО переменной либо константы с на регис тр РА; , - перепись содержимого реги- стров ПР1 и ПР2 в регистры Р1 и Р2 соответственно, Р1ОР2- -РР2 - операция Q над содержимым регистров Р1 и Р2, где О- знак операции, выполняемой в сумматоре 54, и последующая запись в регистр РР2.

Пусть адаптивное вычислительное устройство состоит из щести операционных блоков 3, каждый из которых содержит по четыре сумматора 23. Пол- ньм алгоритм.предназначен для реализации в устройстве, содержащем все операционные блоки, а усеченный - для устройства с одним отказавшим операционным блоком. При реализации полного алгоритма сумматоры 23 блоков 3 могут быть расположены, как показано на фиг. 10, а при реализации усеченного алгоритма - как показано на фиг. 11, где К - контрольные сумматоры 23, а заштрихованный блок 3 обозначает отказавший.

Таким образом введение косвенного контроля и дополнительных возможностей коммутации внутри операцион- ных блоков повышает производительность устройства.

Формула изобретения

1. Адаптивное вычислительное уст- ройство, содержащее входной и выходной регистры и ГУ операционных блоков, при этом вход входного регистра и выход выходного регистра являются

13

соответственно информационным входом и информационным выходом устройства, отличающееся тем, что, с целью повышения производительности,, оно содержит vi коммутаторов, блок памяти данных, блок микропрограммного управления и генератор импульсов, причем первый информационный выход, первый и второй выходы признака результата i -fo операционного блока () соединены соответственно с первым информационным входом и первым и вторым управляющими входами. 1-го коммутатора, второй информационный вход первого коммутатора подключен к выходу входного регистра, второй информационный вход (i+1)-ro коммутатора соединен с выходом i-ro коммутатора, а выход п-го коммутатора подключен к входу выходного регистра, второй и третий информационные выходы, второй и третий информационные входы и синхровход каждого операционного блока подключены соответственно к информационному и адресному входам и информационному выходу блока памяти данных, информационному входу устройства и выходу генератора импульсов, первьй и второй выходы признака результата и вход кода опера- ;),ии i. -го операционного блока соединены соответственно с I.-M входом пуска t-м входом логических условий и I -м выходом блока микропрограммного управления, вход настройки которого подключен к входу ввода программ устройства, при этом операционный бл.ок содержит группу коммутаторов данных, группу сумматоров, две группы коммутаторов результата, группу элементов И, группу элементов равнозначности и два элемента И, выходы которых соединены соответственно с первым и вторым выходами признака результата блока, входы первого элемента И подключены к прямым выходам соответствующих элементов равнозначности группы, входы второго элемента И соединены с инверсньми выходами соответствующих элементов равнозначности группы, управляющие входы, первые, вторые и третьи информационные входы и выходы коммутаторов данных группы подключены соответственно к син- хровходу, первому информационному входу и входу кода операции блока.

203506

14

первым выходам одноименных коммутаторов результата первой группы и первым информационным входам одноименных сумматоров группы, вторые и тре- тьи информационные входы, управляющие входы, первые, вторые и третьи информационные выходы которых соединены соответственно с вторым и третьим информационными входами и входом кода операции блока, инфо эмацион- ными входами одноименных коммутаторов результата первой группы, вторым и третьим информационными выходами блока, управляющие входы и вторые выходы коммутаторов результата первой группы подключены соответственно к входу кода операции блока и информационным входам одноименных коммутаторов результата второй группы, управляющие входы, первые, вторые и третьи выходы которых соединены соответственно с входом кода операции и первым информационным выходом блока, первыми входами одноименных элементов И

группы и первыми входами одноименных элементов равнозначности, а вторые входы и выходы элементов И группы подключены соответственно к синкро- входу блока и вторым входам одно- .

именных элементов равнозначности группы.

2 Устройство по п. 1, отличающее с я тем, что блок микропро- rof.MMHoro управления содержит регистр

настройки, регистр состояния, память микрокоманд, триггер и две группы элементов И, при этом 1-й информационный вход триггера соединен с (-м входом пуска блока, выход триггера

подключен к его синхровходу и первым входам элементов И первой группы, второй вход и выход i-ro элемента И первой группы соединены соответственно с выходом элемента И второй

группы и (-м выходом блока, первый и второй входы L-FO элемента И вто- рой группы подключены соответственно к L-му входу пуска блока и выходу регистра настройки, вход которого

соединен с выходом памяти микрокоманд, вход и выход регистра состояния подключены соответственно к входам логических условий блока и адресному входу памяти микрокоманд, информационный вход которой соединен с

входом настройки блока.

с

jr

т е

en «Ч

П СМ

о оО

-О

о о

о о

о о

о о

&1

Ц к

я

я

и а;

1§

е h

п см

ri ч

гГ

П4

10

00

01 11 101 110

100 111

110

101 10

о 1 1

0 о о

001 010 011 00

Арифметическое сложение

Арифметическое сложение с перет носом в младвше разряды

Арифметическое вычитание

Арифметическое умножение

Логическое сложение

Логическое умножение

Сдвиг влево

Сдвиг право

Инверсия XI Инверсия Х2

Условный переход по значению XI

J C-CWIi-lO у

как -где исполнительный адрес

У-XI + Х2

+ Х2 + С

С - бит переноса

и При выполнении условия , с информационного выхода

23 вьщается сигнал uj, в противном случае -uJ.

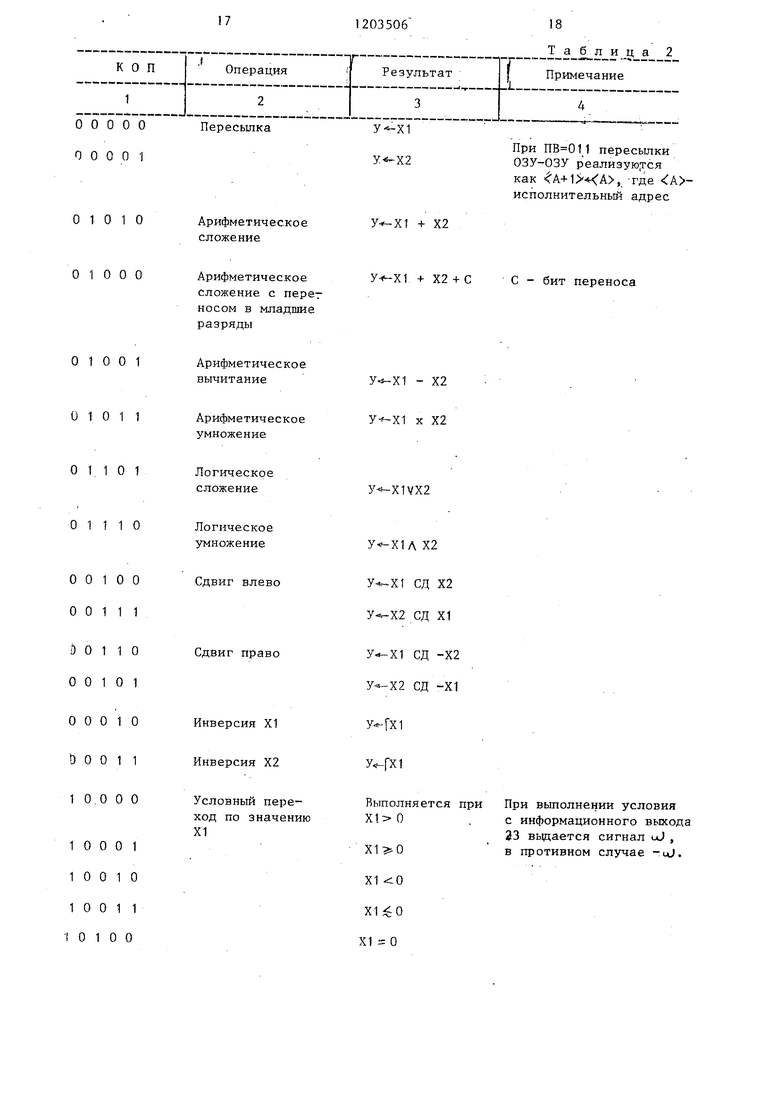

19

Условный переход по значению Х2

Условньй переход

1203506

20 Продолжение табл. 2

IIIL

Выполняется

Х2 с:0

Х2 ,0

Выполняется

XI Х2

XI Ф Х2

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционное устройство с самоконтролем | 1986 |

|

SU1339546A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Устройство для тестового контроля процессора | 1986 |

|

SU1408438A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

Изобретение относится к устройствам для обработки данных. Целью изобретения является повышение производительности устройства. Для этого в устройство введены коммутаторы, выполненные из элементов И , элементов И 5( -5.t и элементов ШШ 6, 6hs блок 9 памяти данных, блок 8 микропрограммного управления и генератор 1 импульсов. Коммутаторы используются для передачи информации из входного регистра 2 в операционные блоки 3 и выходной регистр 7 под управлением сигналов с выхода блока 8. Блок 9 используется для хранения промежуточных данных в процессе вычислений. 11 ил. § (Л

(SS

фиг. 5

ПР1

Y////7//A

Фиг. 6

PPi

/777///)

PPZ

II

V//////} V777777

Фиг. 7

приПВ-fH

ч, t при /73 ffff

ч, t при ПВ-fOl t при Л В fff

Т

0at. iO

фиг. H

| ВСЕСОЮЗиАЙ ПАТЕНТКО-ТЕХШЧЕ^^КД/БИБЛИОГгкд j | 0 |

|

SU363091A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Леннартц Г., Таэгер В | |||

| Конструирование схем на транзисторах: Перев | |||

| с нем | |||

| М.:,Энергия, 1964, с, 203-218 | |||

| Адаптивное вычислительное устройство | 1974 |

|

SU528564A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-07—Публикация

1984-01-16—Подача