Изобретение относится к вычислительной технике и может быть использовано в составе специализированных управляющих или универсальных цифровых вычислительных машин, а также в качестве базового элемента при разработке различного типа распределенных вычислительных структур с повышенной достоверностью получения результата и высоким быстродействием , при отработке малых приращений входных данных.

Цель изобретения - повышение дос товерности вычисления результата.

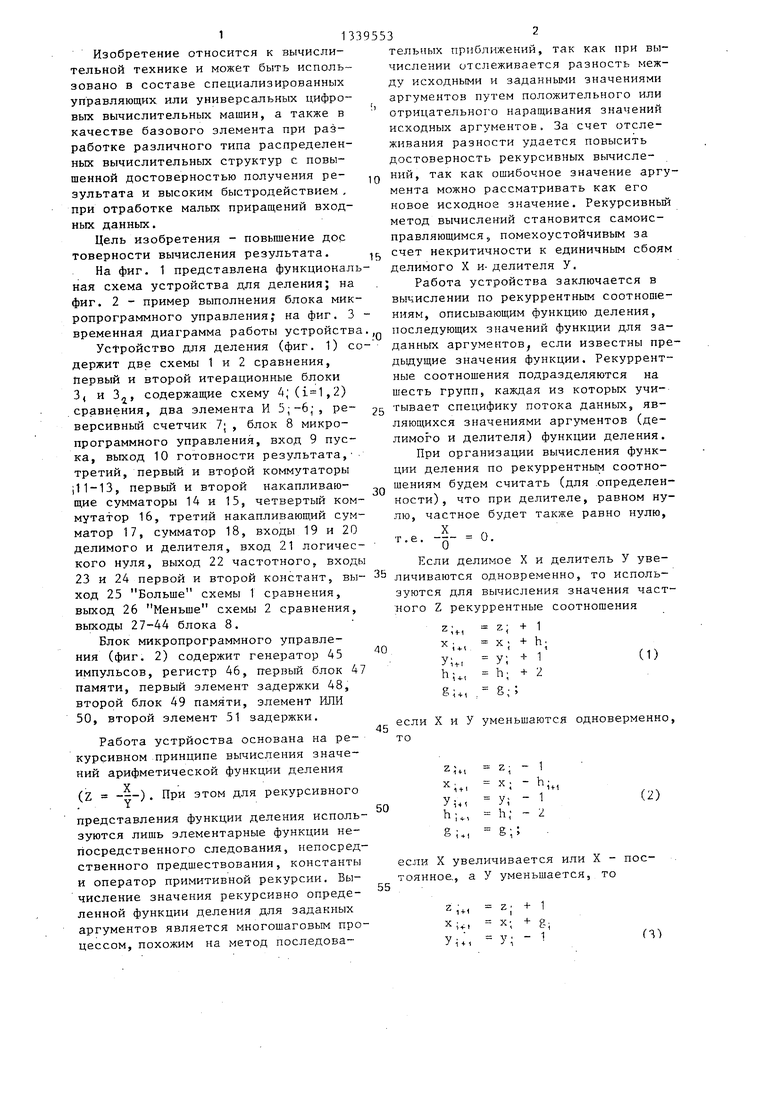

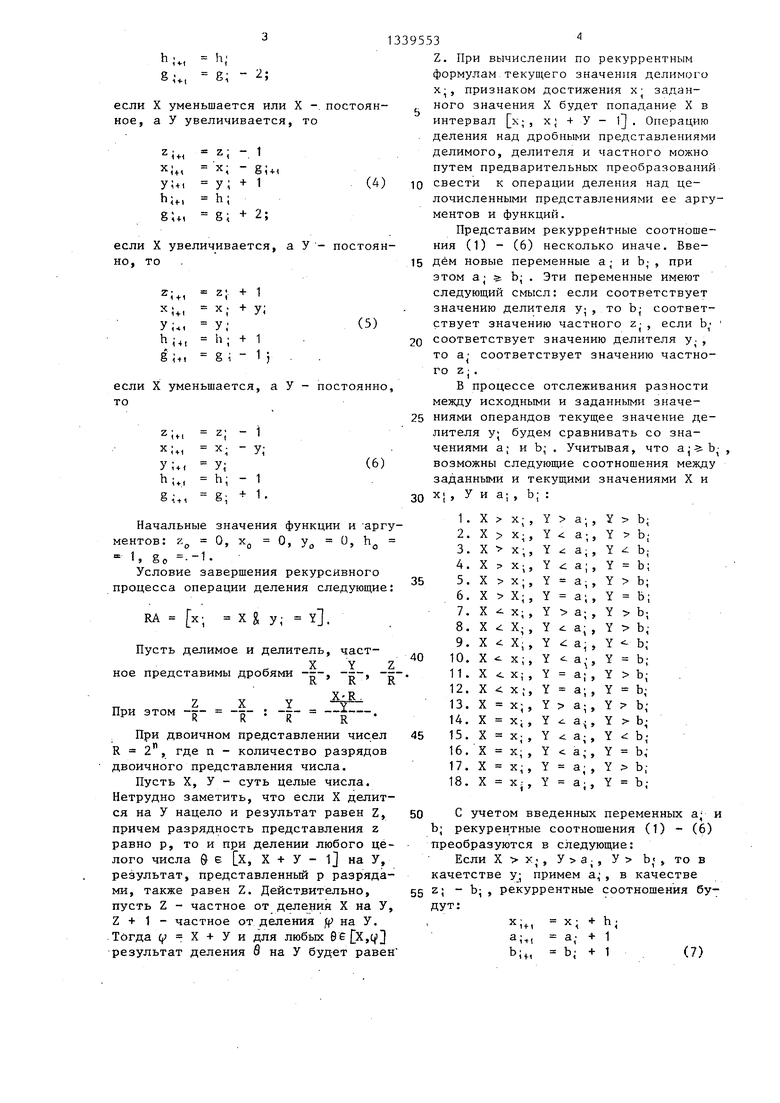

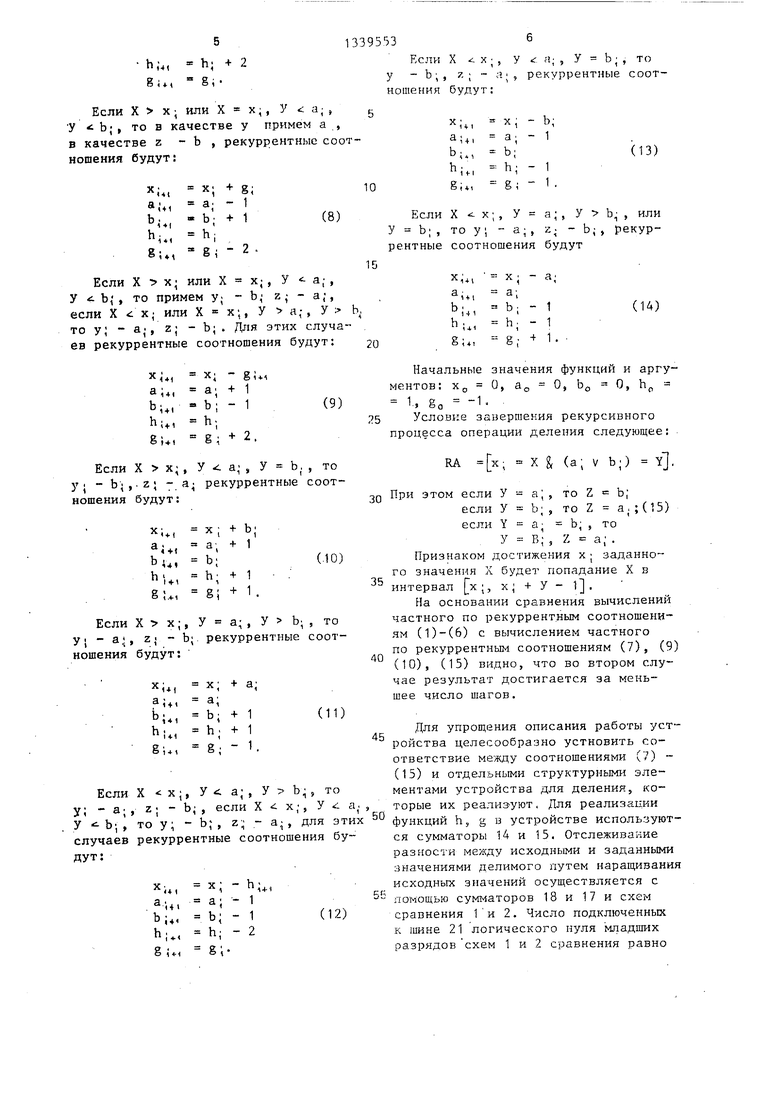

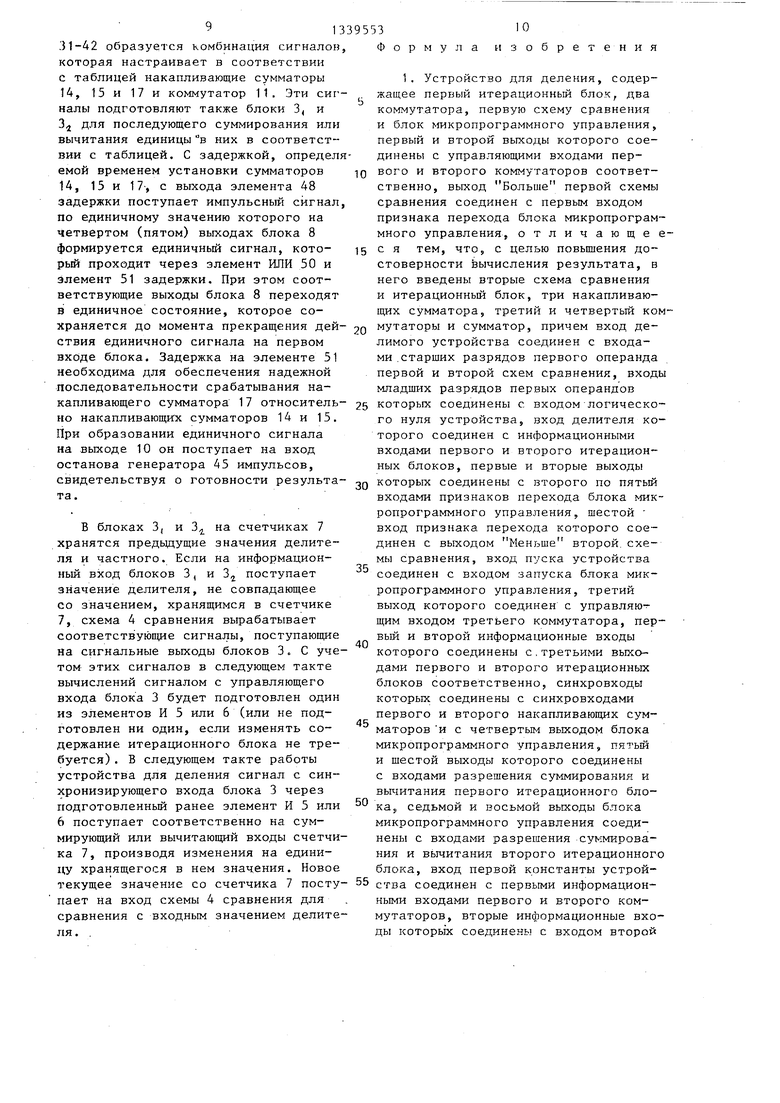

На фиг. 1 представлена функциональная схема устройства для деления; на фиг. 2 - пример выполнения блока микропрограммного управления; на фиг. 3 временная диаграмма работы устройства

Устройство для деления (фиг. 1) содержит две схемы 1 и 2 сравнения, Первый и второй итерационные блоки 3, и 3,, содержащие схему 4; (1 1,2) .сравнения, два элемента И 5;-6;, реверсивный счетчик 7; , блок 8 микропрограммного управления, вход 9 пуска, выход 10 готовности результата, третий, первый и вто15ой коммутаторы 111-13, первьш и второй накапливающие сумматоры 14 и 15, четвертый коммутатор 16, третий накапливающий сумматор 17, сумматор 18, входы 19 и 20 делимого и делителя, вход 21 логического нуля, выход 22 частотногоS входы 23 и 24 первой и второй констант, выход 25 Больше схемы 1 сравнения, выход 26 Меньше схемы 2 сравнения, выходы 27-44 блока 8.

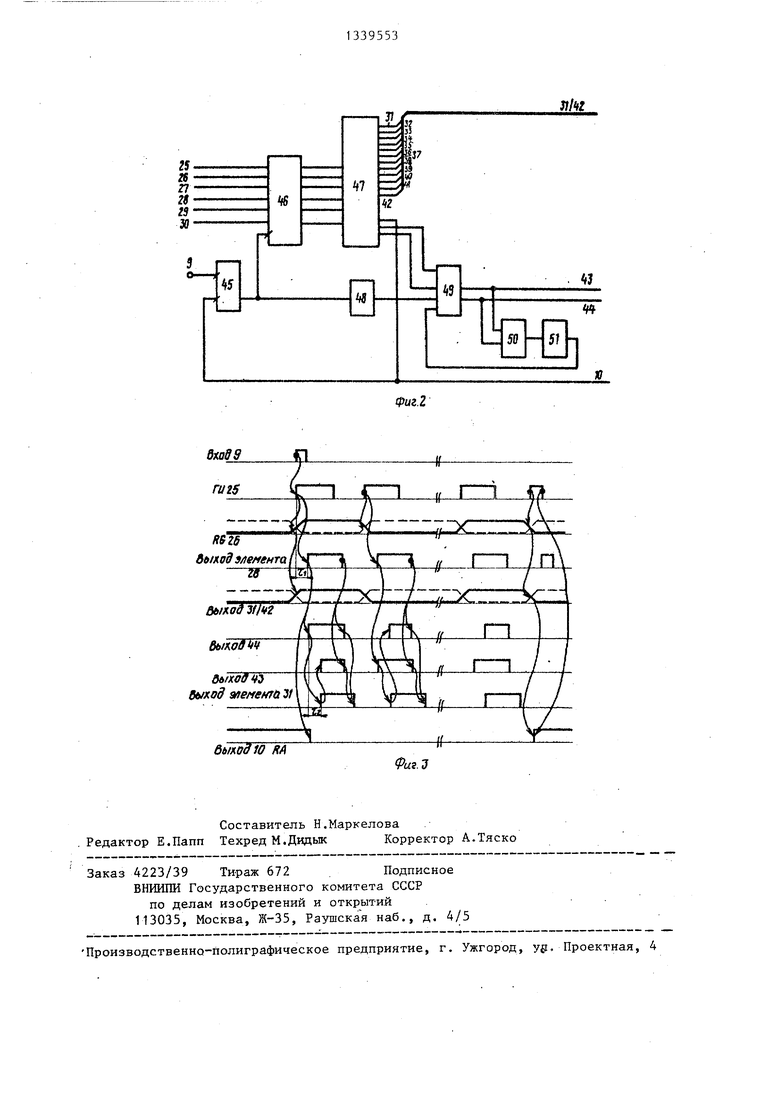

Блок микропрограммного управления (фиг. 2) содержит генератор 45 импульсов, регистр 46, первый блок 47 памяти, первый элемент задержки 48, второй блок 49 памяти, элемент ИЛИ 50, второй элемент 51 задержки.

Работа устрйоства основана на рекурсивном принципе вычисления значений арифметической функции деления

у

(Z ---). При этом для рекурсивного

представления функции деления используются лишь элементарные функции непосредственного следования, непосредственного предшествования, константы и оператор примитивной рекурсии. Вычисление значения рекурсивно определенной функции деления для заданных аргументов является многошаговым процессом, похожим на метод последова

5

0

тельных приближений, так как при вычислении отслеживается разность между исходными и заданными значениями аргументов путем положительного или отрицательнот о наращивания значений исходных аргументов. За счет отслеживания разности удается повысить достоверность рекурсивных вычислений, так как ошибочное значение аргумента можно рассматривать как его новое исходное значение. Рекурсивный метод вычислений становится самоисправляющимся, помехоустойчивым за счет некритичности к единичным сбоям делимого X и- делителя У,

Работа устройства заключается в вычислении по рекуррентным соотношениям, описывающим функцию деления, последующих значений функции для заданных аргументов, если известны предыдущие значения функции. Рекуррентные соотношения подразделяются на шесть групп, каждая из которых учитывает специфику потока данных, яв- значениями аргументов (делимого и делителя) функции деления.

При организации вычисления функции деления по рекуррентным соотношениям будем считать (для .определенности) , что при делителе, равном нулю, частное будет также равно нулю.

т.е.

-I- - о35

Если делимое X и делитель У увеличиваются одновременно, то используются для вычисления значения частного Z рекуррентные соотношения

0

уи,

hu, S 1 + 1

; у;

h

+1

h;

+1

-t-2

(1)

45

если X и У уменьшаются одноверменно.

то

Уь

h

У; h;

(2)

55

если X увеличивается или X - постоянное., а У уменьшается, то

г; + 1 х| + g.

у, - 1

(3)

равно р, то и при делении любого целого числа & е х, X + У - 1 на У, результат, представленный р разрядами, также равен Z. Действительно, пусть Z - частное от деления X на У, Z + 1 - частное от деления на У. .Тогда С( X + У и для любых ,q)j результат деления б на У будет равен

39553

Z. При вычислении по рекуррентным формулам.текущего значения делимого х, признаком достижения х заданного значения X будет попадание. X в интервал х;, х; + У - ij . Операцию . деления над дробными представлениями делимого, делителя и частного можно путем предварительных преобразований 1Q свести к операции деления над целочисленными представлениями ее аргументов и функций.

Представим рекуррентные соотноше- ния (1) - (6) несколько иначе, Вве- 15 Дём новые переменные & и Ь; , при этом а; 5; Ь; . Эти переменные имеют

преобразуются в следующие:

Если X X., У а;, У Ь, то в качетстве у; примем а;, в качестве 55 Z; - b; , рекуррентные соотношения будут:

3; Ь;

-Ь h, + 1 + 1

(7)

числу n разрядов двоичного представления входных операндов и частного.

Это связано с необходимостью предварительного сдвига делимого на n разрядов влево.

Отслеживание разности между исходным и заданным значением делителя- .путем наращивания исходного значения делителя осуществляется с помощью блоков 3, и 3 .

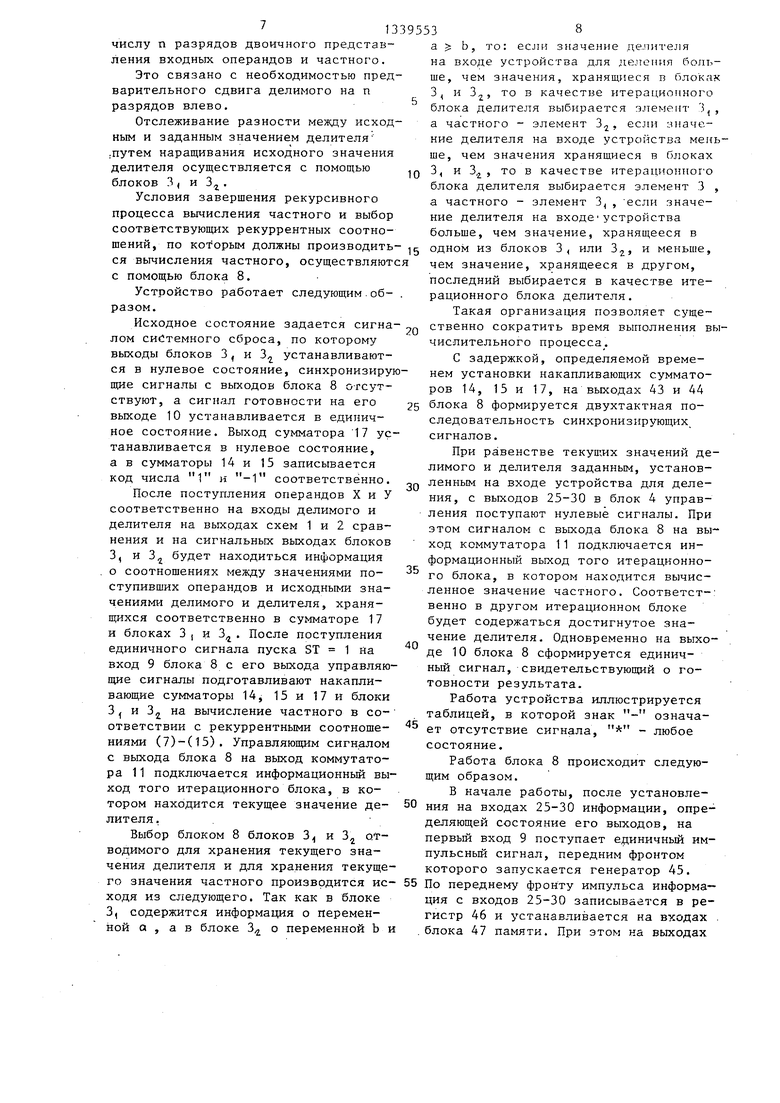

Условия завершения рекурсивного процесса вычисления частного и выбор соответствующих рекуррентных соотношений, по которым должны производить- ся вычисления частного, осуществляютс с помощью блока 8.

Устройство работает следующим.об- разом.

Исходное состояние задается сигналом системного сброса, по которому выходы блоков 3, и 3 устанавливают

щие сигналы с выходов блока 8 отсутствуют, а сигнал готовности на его выходе 10 устанавливается в единичное состояние. Выход сумматора 17 устанавливается в нулевое состояние, а в сумматоры 14 и 15 записывается код числа 1 и -1 соответственно.

После поступления операндов X и У соответственно на входы делимого и делителя на выходах схем 1 и 2 сравнения и на сигнальных выходах блоков 3, и 3 будет находиться информация о соотношениях между значениями поступивших операндов и исходными значениями делимого и делителя, хранящихся соответственно в сумматоре 17 и блоках 3 , и 3. После поступления единичного сигнала пуска ST 1 на вход 9 блока 8 с его выхода управляющие сигналы подготавливают накапливающие сумматоры 14, 15 и 17 и блоки 3( и 3ji на вычисление частного в соответствии с рекуррентными соотношениями (7)-(15). Управляющим сигналом с выхода блока 8 на выход коммутатора 11 подключается информационный выход того итерационного блока, в котором находится текущее значение делителя.

Выбор блоком 8 блоков 3 и 3 о.тВ начале работы, после установления на входах 25-30 информации, определяющей состояние его выходов, на первый вход 9 поступает единичньй импульсный сигнал, передним фронтом которого запускается генератор 45.

водимого для хранения текущего значения делителя и для хранения текущего значения частного производится ис- 55 По переднему фронту импульса информа- ходя из следующего. Так как в блоке ция с входов 25-30 записывается в ре- 3, содержится информация о перемен- гистр 46 и устанавливается на входах ной а , а в блоке 3 о переменной b и блока 47 памяти. При этом на выходах

а j: Ь, то: если значение делителя на входе устройства для деления больше, чем значения, хранящиеся в блокак

10

с

0

30

35

40

50

2

ТО В качестве итерационного

3, и 3

блока делителя выбирается элемент 3,, а частного - элемент 3,, если значение делителя на входе устройства меньше, чем значения хранящиеся в блоках 3, и 3 , то в качестве итерационног о блока делителя выбирается элемент 3 , а частного - элемент 3 , если значение делителя на входе устройства больше, чем значение, хранящееся в одном из блоков 3, или 3j, и меньше, чем значение, хранящееся в другом, последний выбирается в качестве итерационного блока делителя.

Такая организация позволяет существенно сократить время выполнения вычислительного процесса.

С задержкой, определяемой временем установки накапливающих сумматоров 14, 15 и 17, на выходах 43 и 44 25 блока 8 формируется двухтактная последовательность синхронизирующих сигналов.

При равенстве текущих значений делимого и делителя заданным, установленным на входе устройства для деления, с выходов 25-30 в блок 4 управления поступают нулевые сигналы. При этом сигналом с выхода блока 8 на вы - ход коммутатора 11 подключается информационный выход того итерационного блока, в котором находится вычисленное значение частного. Соответст-: венно в другом итерационном блоке будет содержаться достигнутое значение делителя. Одновременно на выходе 10 блока 8 сформируется единичный сигнал, свидетельствующий о готовности результата.

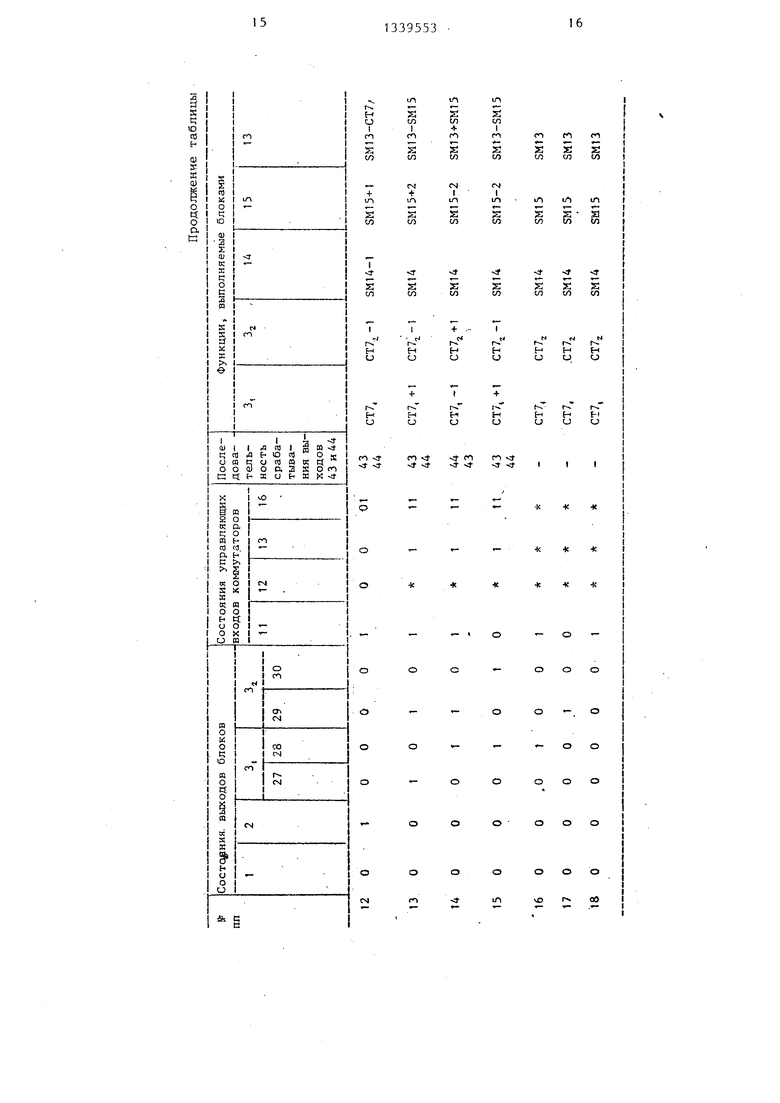

Работа устройства иллюстрируется таблицей, в которой знак - означа- ет отсутствие сигнала, - любое состояние.

Работа блока 8 происходит следующим образом.

В начале работы, после установления на входах 25-30 информации, определяющей состояние его выходов, на первый вход 9 поступает единичньй импульсный сигнал, передним фронтом которого запускается генератор 45.

55 По переднему фронту импульса информа- ция с входов 25-30 записывается в ре- гистр 46 и устанавливается на входах блока 47 памяти. При этом на выходах

913

31-42 образуется комбинация сигналон которая настраивает в соответствии с таблицей накапливающие сумматоры 14, 15 и 17 и коммутатор 11. Эти сигналы подготовляют также блоки 3 и 3 для последующего суммирования или вычитания единицы °в них в соответствии с таблицей. С задержкой, определяемой временем установки сумматоров 14, 15 и 17-, с выхода элемента 48 задержки поступает импульсный сигнал, по единичному значению которого на четвертом (пятом) выходах блока 8 формируется единичный сигнал, кото- рый проходит через элемент ИЛИ 50 и Элемент 51 задержки. При этом соответствующие выходы блока 8 переходят в единичное состояние, которое сохраняется до момента прекращения дей- ствия единичного сигнала на первом входе блока. Задержка на элементе 51 необходима для обеспечения надежной Последовательности срабатывания накапливающего сумматора 17 относитель- но накапливающих сумматоров 14 и 15. При образовании единичного сигнала на выходе 10 он поступает на вход останова генератора 45 импульсов, свидетельствуя о готовности результа- та.

В блоках 3, и 3 на счетчиках 7 хранятся предьщущие значения делителя и частного. Если на информационный вход блоков 3, и 3j поступает значение делителя, не совпадающее со значением, хранящимся в счетчике 7, схема 4 сравнения вырабатывает соответствуюпще сигналы, поступающие йа сигнальные выходы блоков 3. С уче- ТОМ этих сигналов в следующем такте вычислений сигналом с управляющего входа блока 3 будет подготовлен один из элементов И 5 или 6 (или не подготовлен ни один, если изменять содержание итерационного блока не требуется) . В следующем такте работы устройства для деления сигнал с синхронизирующего входа блока 3 через подготовленньй ранее элемент И 5 или 6 поступает соответственно на суммирующий или вычитающий входы счетчика 7, производя изменения на единицу хранящегося в нем значения. Новое текущее значение со счетчика 7 посту- пает На вход схемы 4 сравнения для сравнения с входным значением делителя . .

5 5 n

5

5

0

5

5310

Формула изобретения

1. Устройство для деления, содержащее первый итерационный блок, два коммутатора, первую схему сравнения и блок микропрограммного управления, первый и второй выходы которого соединены с управляющими входами первого и второго коммутаторов соответственно, выход Больше первой схемы сравнения соединен с первым входом признака перехода блока микропрограммного управления, отличающее- с я тем, что, с целью повьщ1ения достоверности вычисления результата, в него введены вторые схема сравнения и итерационный блок, три накапливающих сумматора, третий и четвертый коммутаторы и сумматор, причем вход делимого устройства соединен с входами .старших разрядов первого операнда первой и второй схем сравнения, входы младщих разрядов первых операндов которых соединены с входом логического нуля устройства, вход делителя которого соединен с информационными входами первого и второго итерационных блоков, первые и вторые выходы которых соединены с второго по пятый входами признаков перехода блока микропрограммного управления, шестой вход признака перехода которого соединен с выходом Меньше второй, схемы сравнения, вход пуска устройства соединен с входом запуска блока микропрограммного управления, третий выход которого соединен с управляющим входом третьего коммутатора, первый и второй информационные входы которого соединены с,третьими выходами первого и второго итерационных блоков соответственно, синхровходы которых соединены с синхровходами первого и второго накапливающих сумматоров и с четвертыг выходом блока микропрограммного управления, пятьм и щестой выходы которого соединены с входами разрешения суммирования и вычитания первого итерационного блока, седьмой и восьмой выходы блока микропрограммного управления соединены с входами разрешения суммирования и вычитания второго итерационного блока, вход первой константы устройства соединен с первыми информационными входами первого и второго коммутаторов, вторые информационные входы KOTOpbix соединены с входом второй

константы устройства, выходы первого и второго коммутаторов соединены с информационными входами первого и второго сумматоров соответственно, выходы которых соединены с первыми вторым информационными входами четвертого коммутатора, третий информационный вход -которого соединен с выходом третьего коммутатора, с выходом частного устройства и с первым информационным входом сумматора, второй информационный вход которого соединен с входом второго операнда второй схемы сравнения и выходом третьего накапливающего сумматора, информационный вход которого соединен с выходом четвертого коммутатора, первый и второй управляющие входы которого соединены с девятым и десятым выходами блока микропрограммного управления, одиннадцатый и двенадцатый выходы которого соединены с входами разрешения работы первого и второго накапливающих сумматоров соответственно , тринадцатый и четырнадцатый выходы блока микропрограммного управления соединены с входом разрешения работы и синхровходом соответственно

Q

5

0

третьего накапливающего сумматора, вход второго операнда первой схемы сравнения соединен с выходом сумматора, пятнадцатый выход блока микропрограммного управления соединен с выходом готовности результата устройства.

2. Устройство по п. 1, о т л и - ч а ю щ е е с я тем, что каждьй итерационный блок содержит схему сравнения, два элемента И и реверсивный счетчик, причем информационный вход блока является входом первого операнда схемы сравнения, выходы Больше и Меньше которой соединены с первым и вторым выходами блока соответственно, синхровход блока соединен с первыми входами первого и второго элементов И, выходы которьк соединены со счетным и вычитающим входами соответственно реверсивного счетчика, выход которого соединен с входом второго операнда схемы 5 сравнения и является третьим выходом блока,,входы разрешения суммирования и вычитания блока соединены с вторыми входами первого и второго элементов И соответственно.

f4

(Л

чО

со

о

4ro

S

to I

го

-

S ел

s:

to

(Л

s

СЛ

SI

I

in

s

CO

(М 1Л

i

1Л

i

Й

s

to

S to

;s s: s

СЛ(Л V5

H

о

H

u

-.Г--rНИНU U О

и о

H

и

f- c r H H H

и cj cj

ч)- сЛ -

ro «

-3- - I

о о о

0-0

- о о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1986 |

|

SU1388852A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для нахождения экстремума аддитивной функции многих переменных | 1990 |

|

SU1765830A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| Устройство для деления | 1990 |

|

SU1728862A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018933C1 |

| Устройство для деления | 1986 |

|

SU1390608A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение достоверности вычисления результата. Сущность изобретения заключается в использовании рекурсивного принципа вычисления значений арифметической функции деления. Устройство для деления содержит две схемы сравнения 1-2, итерационные блоки , в состав которых входят схемы сравнения 4;, элементы И 5,--6; и реверсивные счетчики 7; , коммутаторы 11-13, 16, накапливающие сумматоры 14-15, 17 сумматор 18, входы .пуска 9, делимого 19, делителя 20, логического нуля 21, кбнстант 23-24. Устройство обеспечивает высокое быстродействие при отработке -малых приращений входных данных. 1 з.п., 3 ил., 1 табл. в (/) С у I

Oxaffff

ru2S

RSZ6 быхад злеиенгй

Выпад yfitt

6ым1Г

йьТшГЩ Выход aaeffefffd У

бьмдю КА

(риг.-З

Составитель Н.Маркелова Редактор Е.Папп Техред М.Дидык Корректор А.Тяско

Заказ 4223/39 Тираж 672 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

-Производственно-полиграфическое предприятие, г, Ужгород, yfi. Проектная, 4

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1978 |

|

SU781813A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1985-12-24—Подача