Изобретение относится к вычислительной технике и может быть использовано в арифме тическнх устройствах специализированных ЭВМ Известны устройства для деления двоичных чисел, в которых частное вычисляется путем последовательных сложений-вычитаний и сдвигов. Известные устрйоства содержат регистры делимого, делителя и частного, сумматор-вычи татепь, схему анализа знака остатка и схему управления 1). Недостатком известных устройств является невысокое быстродействие. Наиболее близкое по технической сущности к предлагаемому - устройство для деления двоичных чисел, содержащее регистры множимого и множителя, коммутаторы, пирамидальный умножитель, блок хранения множителя, регистр результата, блок управления, причем первый вход первого коммутатора соединен с входной шиной устройства, выход первого ком мутатора - со входом регистра множимого, выход регистра множимого - с первым входом пирамидального умножителя и со входом блока хранения множителя, выход блока хр нения множителя - с первым входом второго коммутатора, выход второго коммутатора - со входом регистра множители выход регистра множителя - со вторым входом пирамидального умножителя, выход умножителя соединен со входом регистра результата, выход регистра результата - со вторыми входами первого и второго коммутаторов и с выходной шиной устройства, выход блока управления - с управляющими входами первого коммутатора, второго коммутатора и пирамидального умножителя. Деление в данном устройстве осуществляется по методу последовательных приближений Гильмана 2. Данное устройство также отличается недостаточным быстродействием, так как время выполнения деления зависит от точности выбора начального приближения обратной величины и, в общем случае, довольно велико. Цель изобретения - повышение быстродействия устройства при решении определенных классов задач, для которых значения аргументов от одного шага вычислений к другому изменяются плавно.

Поставленная цель достигается тем, что в устойство для деления, содержащее регистры множимого и множителя, коммутаторы, пирамидальный умножитель, регистр результата, лок управления, схему сравнения, причем перый и второй входы первого коммутатора соеинены соответственно с входными шинами деимого и делителя устройства, выход первого оммутатора соединен с входом регистра мноимого, выход регистра множимого соединен с первым входом пирамидального умножителя, второй вход пирамидального умножителя соединен с выходом регистра множителя, выход пирамидального умножителя соединен со входом регистра результата, выход регистра результата соединен с первым входом второго коммутатора, с третьим входом первого коммутатора и с выходной шиной устройства, выход второго коммутатора соединен со входом регистра множителя, входы схемы сравнения соединены с выходами регистра множителя и регистра результата, а выход схемы сравнения - со входом блока управления, выход блока управления соединен с управляющими входами первого коммутатора,второго коммутатора и пирамидального умножителя, введен блок экстраполяции, причем выход блока экстраполяции соединен со вторым входом второго коммутатора, выход регистра результата соединен со входом экстраполяции.

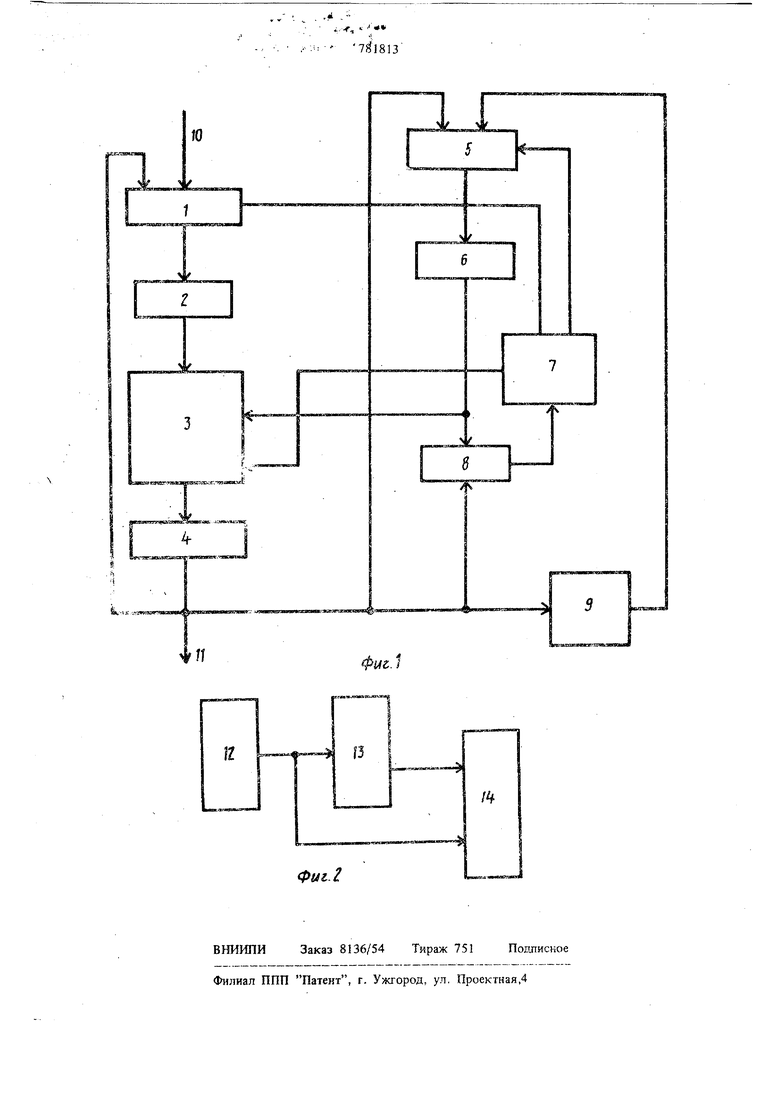

Кроме того, блок экстраполяции содержит п буферных регистров и п -входовой сумми рующий узел, причем выход каждого буферного регистра соединен со входом следующего буферного регистра и с одним из входов суммирующего узла, вход первого буферного регистра является входом блока экстраполяции, а выход суммирующего узла является выходом блока экстраполяции.

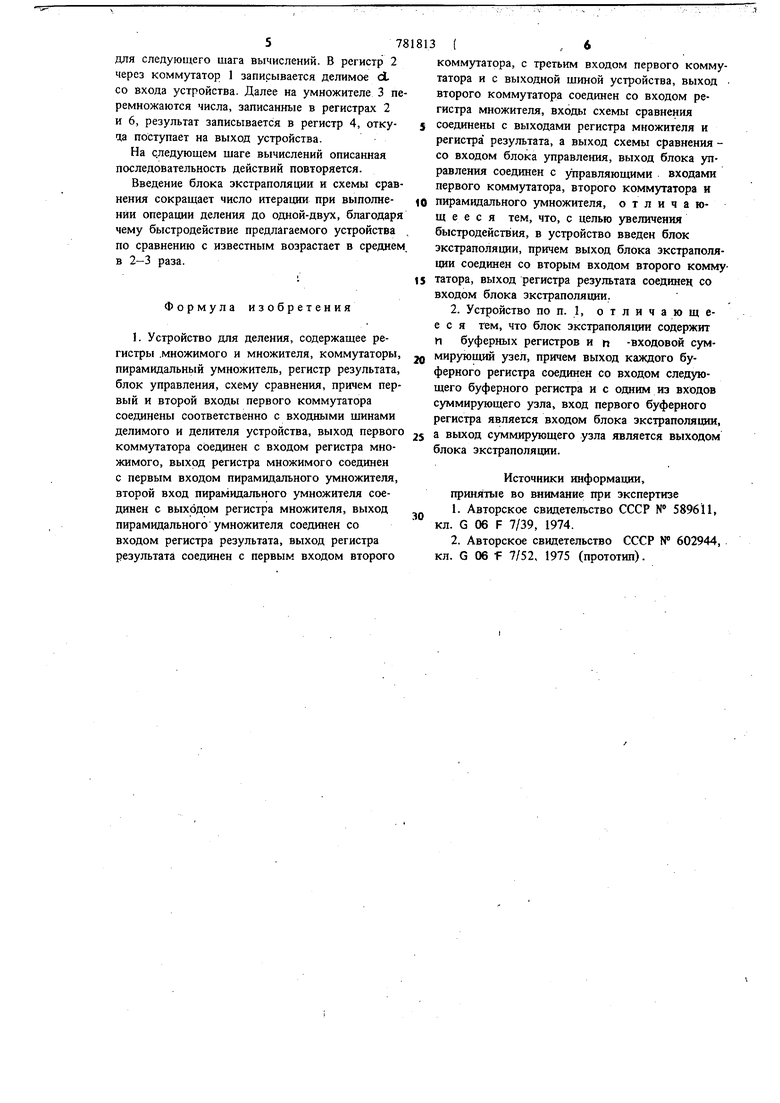

На фиг. 1 изображена функциональная схема устройства для деления; на фиг. 2 - схема блока экстраполяции.

Устройство содержит коммутатор 1, регистр -2 множимого, пирамидальный умножитель 3, регистр 4 результата, коммутатор 5, регистр 6 множителя, блок 7 управления, схему 8 сравнения, блок 9 -эkcтpaпoляции, входные шИны 10 и 11 делимого и делителя, выходную шину 12. Блок9 экстраполяции содержит буферные регистры 13 и многовходовой суммирующий узел 14.

В устройстве реализуется итеративный метод деления, основанный на предварительном вычислении обратной величины делителя и последующем умножении ее на делимое. Обратная величина определяется по итерационной формуле

ч.-(2.-с,-1),()

Ъ делитель;с.значения величины 1/в, полученные

х соответственно на i -и и + 1-й итерации.

Блок 9 экстраполяции позволяет для определения начального приближения искомой обратной величины использовать экстраполяцию по ее значени 1м на предыдущих шагах вычислений. Например, при экстраполяции по 2-м или 3-м точкам используются соответственно формулы

CD

iS-i

(ъ)

.-зс

+ С

j2 j-a

экстраполированное значение С

где С

J на j -ом шаге вычислений, используемое в качестве начального приближения в формуле (1); С: Ci С- значения С на предыдущих шагах

J-

вычислении.

К началу очередной операции в регистрах 13 блока 9 экстраполяции записаны п значений обратной величины делителя, полученные в предыдущих операциях. На суммирующем узле 14 формируется экстраполированное значение обратной величины делителя С, по соответствующим формулам экстраполяции.

Выполнение операции деления в устройстве начинается с того, что делитель через комк 1утатор 1 записывается в регистр множимого 2, а С- через коммутатор 5 поступает в регистр множителя 6. На умножителе 3 формируется величина (2- С ) равная разности числа два и произведения сомножителей, записанных в регистрах 1 и 6 соответственно. Эта величина через регистр 4 результата и коммутатор 1 поступает в регистр 2. Затем на умножителе 3 формируется и записывается в регистр 4 произведение содержимого регистров 2 и 6, соответствующее следующему приближению величины С ж /jb, Полученное значение схемой 8 сравнения сравнивается с предыдущим значением С , записанным в регистре 6. Если разность между сравниваемыми значениями больше допустимой величины, содержимое регистра 4 через коммутатор 5 записывается в регистр 6, а в регистр 2 вновь записывается делитель, после чего аналогичным образом выполняется следующая итерация.

Если сравниваемые значения достаточно мало отличаются друг от друга, то схема 8 сравнения вырабатывает сигнал, по которому блок 7 упраления реализует следующую последовательность действий. Полученное значение С из регистра 4 поступает через коммутатор 5 в регистр 6 и в блок экстраполяции, где вычисляется С 578 для следующего шага вычислений. В регистр 2 через коммутатор 1 записывается делимое Л со входа устройства. Далее на умножителе 3 пе ремножаются числа, записанные в регистрах 2 и 6, результат записывается в регистр 4, откуча поступает на выход устройства. На следующем шаге вычислений описанная последовательность действий повторяется. Введение блока экстраполяции и схемы сравнения сокращает число итерации при выполнении операции деления до одной-двух, благодаря чему быстродействие предлагаемого устройства по сравнению с известным возрастает в среднем в 2-3 раза. Формула изобретения 1. Устройство для деления, содержащее регистры .множимого и множителя, коммутаторы, пирамидальный умножитель, регистр результата, блок управления, схему сравнения, причем первый и второй входы первого коммутатора соединены соответственно с входными шинами делимого и делителя устройства, выход первого коммутатора соединен с входом регистра множимого, выход регистра множимого соединен с первым входом пирамидального умножителя, второй вход пирамидального умножителя соединен с выходом регистра множителя, выход пирамидального умножителя соединен со входом регистра результата, выход регистра результата соединен с первым входом второго коммутатора, с третьим входом первого коммутатора и с выходной шиной устройства, выход второго коммутатора соединен со входом регистра множителя, входы схемы сравнения соединены с выходами регистра множителя и регистра результата, а выход схемы сравнения со входом блока управления, выход блока управления соединен с уттравляющими входами первого коммутатора, второго коммутатора и пирамидального умножителя, отличающееся тем, что, с целью увеличения быстродействия, в устройство введен блок экстраполяции, причем выход блока зкстраполяции соединен со вторым входом второго коммутатора, выход регистра результата соединен со входом блока экстраполяции. 2, Устройство по п. 1, отличающееся тем, что блок экстраполяции содержит п буферных регистров и п -входовой суммирующий узел, причем выход каждого буферного регистра соединен со входом следующего буферного регистра и с одним из входов суммирующего узла, вход первого буферного регистра является входом блока экстраполяции, а выход суммирующего узла является выходом блока экстраполяции. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 589611, кл. G 06 F 7/39, 1974. 2.Авторское свидетельство СССР N« 602944, кл. G 06 f 7/52, 1975 (прототип).

ю

f f

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Вычислительное устройство | 1987 |

|

SU1456949A1 |

| Устройство для деления | 1975 |

|

SU602944A1 |

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

| Устройство для деления 48-разрядных чисел | 1984 |

|

SU1239712A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

Авторы

Даты

1980-11-23—Публикация

1978-09-12—Подача