Изобретение относится к вычисли- гельной технике и может использоваться при построении микропрограммных процессоров.

Цель изобретения - расширение области применения за счет организации механизма косвенной адресации.

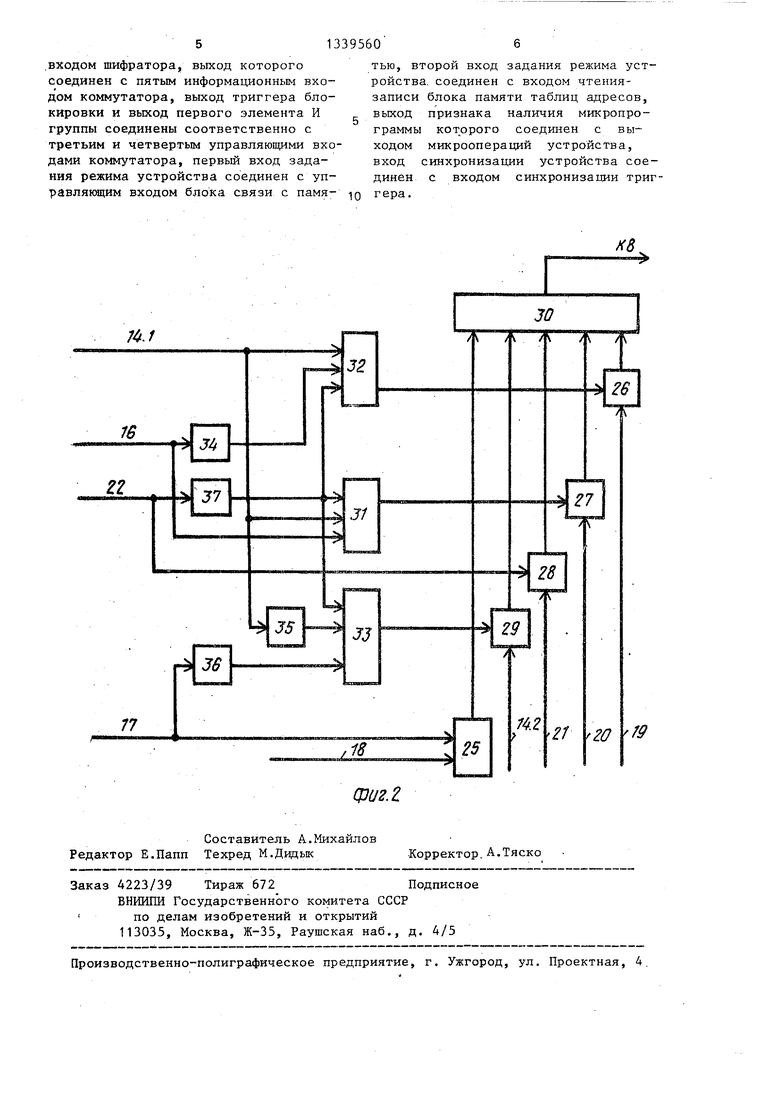

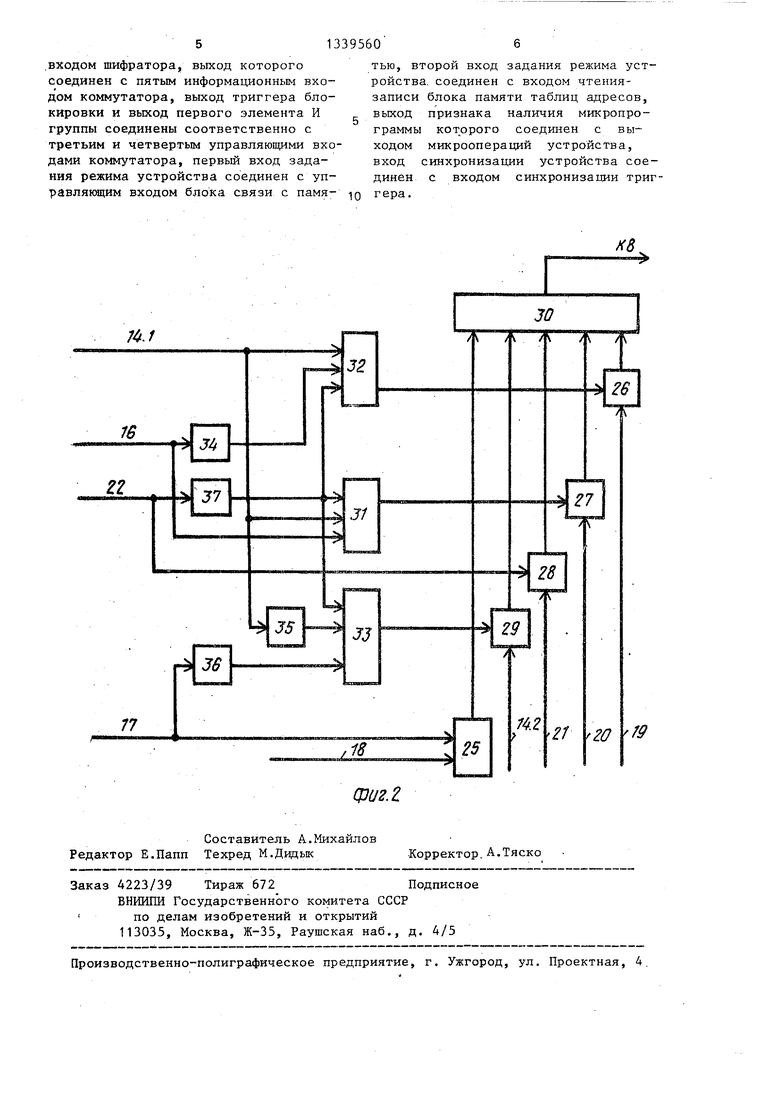

На фиг. 1 приведена функциональная схема устройства микропрограммного управления; на фиг. 2 - функциональная схема коммутатора.

Устройство (фиг. 1) содержи блок 1 памяти микропрограмм (управляющая

память) , блок 2 связи с памятью, ре- выполнение требуемой микропрограммы. гистр 3 микрокоманды,группу 4элемен- Если микропрограмма не загружена.

тов И, регистр 5 адреса, триггер 6 блокировки, элемент ИЛИ 7, блок В памяти таблиц адресов, коммутатор 9, триггер 10 и шифратор 11, первый вход 12 логических условий устройства (шина Запросы), первый вход 13 данных устройства (шина Данные СП), выходы 14 микроопераций устройства

по сигналу из памяти 8 таблиц устанавливаются триггер 10 и через схему ИЛИ 7 триггер 6 блокировки, который запрещает распространение микрокоманды, только что прочитанной по выбранному адресу.-Потенциал-с выхода триггера, 10 поступает на шифратор 11 для формирования адреса строки памя- (шина Микрокоманда), выходы 25 таблиц, где хранится начальный

14 группы 4 элементов И, выход 15, микроопераций- устройства (шина Состояние УП), второй вход 15/, задания режима устройства, второй вход

16логических условий устройства (вход Расширение КОП), третий вход

17логических условий устройства (вход Управление ЦП), первый вход |18 кода команды-устройства (шина

Данные ЦП), второй вход 19 кода ко30

адрес микропрограммы загрузки требуемого блока микропрограмм.

Во время выполнения микропрограммы возможен переход, из, одного блока в другой (если микропрограмма занимает несколько блоков). В текущий момент не все блоки могут находиться в УП и место расположения блоков.

кроме того, произвольно. Поэтому адреса переходов за пределы того блока,г

манды устройства (шина Код операции 35 в котором работает текущая микро- третий вход 20 кода команды устройст- программа, преобразуются в реальные ва (шина Расширенный код операции), выход 21 шифратора, выход 22 триггера блокировки, вход 23 синхронизации устройства, первый вход 24 зада ния режима устройства.

Коммутатор 9 (фиг. 2) содержит

40

адреса блоков УП. Таблица реальных адресов блоков по объему рассчитана на максимальное количество блоков, размещаемых в СП. В рассматриваемом примере 512 таких блоков и соответственно в таблице 512 строк. Запись реальных адресов блоков УП осуществляется микропрограммно во 45 время подкачки блока по требованию микрокоманды. Если блок не загружен в УП, в соответствующей ему строке записан признак наличия блока, по которому происходит выход на микрогруппы 25-29 элементов И, группу 30 элементов ИЛИ,- группы 31-33 элементов И и 34-37 элементов НЕ.

ваемом примере 512 таких блоков и соответственно в таблице 512 строк. Запись реальных адресов блоков УП осуществляется микропрограммно во 45 время подкачки блока по требованию микрокоманды. Если блок не загружен в УП, в соответствующей ему строке записан признак наличия блока, по которому происходит выход на микроУстройство работает следуюш;им образом.

С помощью специадьных микропрограмм загружаются все таблицы в память до программу подкачки этого блока, как 8 таблиц (перед началом работы), Изменение информации во время работы в этой памяти доступно только специальным микропрограммам и осущеэто описано вьше.

Номер блока из регистра 3 микрокоманд через группу 4 элементов И и

ствляется с помощью шины 18 Данные gg коммутатор 9 поступает на адресные

входы памяти 8 таблиц, а прочитан- ньш реальньй адрес блока и младшая часть адреса микрокоманды поступает в регистр 5 адреса микрокоманд.

ЦП. При этом адрес поступает через группу 25 элементов И и группу 30 элементов, ИЛИ, а информация - непосредственно в память 8 таблиц. При

переходе на выполнение текущей команды программы по коду операции (или расширенному коду операции) через коммутатор 9 происходит обращение к таблице начальных адресов микропрограмм и выбирается из памяти 8 таблиц строка, .содержащая адрес, признак на ишну 15 Состояние УП и приз- нак наличия искомой микропрограммы в управляющей памяти 1 (УП),-Если микропрограмма загружена в УП, адрес из памяти 8 таблиц передается в регистр 5 адреса микрокоманд и начинается

адрес микропрограммы загрузки требуемого блока микропрограмм.

Во время выполнения микропрограммы возможен переход, из, одного блока в другой (если микропрограмма занимает несколько блоков). В текущий момент не все блоки могут находиться в УП и место расположения блоков.

35 в котором работает текущая микро- программа, преобразуются в реальные

40

адреса блоков УП. Таблица реальных адресов блоков по объему рассчитана на максимальное количество блоков, размещаемых в СП. В рассматри35 в котором работает текущая микро- программа, преобразуются в реальные

ваемом примере 512 таких блоков и соответственно в таблице 512 строк. Запись реальных адресов блоков УП осуществляется микропрограммно во 45 время подкачки блока по требовани микрокоманды. Если блок не загружен в УП, в соответствующей ему строке записан признак наличия блока, по которому происходит выход на микродо программу подкачки этого блока, как

программу подкачки

это описано вьше.

Коммутатор 9, предназначенный для формирования адреса обращения к памяти 8 таблиц, работает следующим образом,

Управляющий код из микрокоманды, обозначающий конец предьщущей микропрограммы, с выхода группы 4 элементов И поступает на элементы И 32 и 31 и элемент НЕ 35 для формирования разрешающих потенциалов. При поступлении этого кода на выходе элемента И 32 появляется разрешающий потенциал на группу элементов И 26 и выдается адрес обращения по коду операции на группу элементов ИЛИ 30.

При появлении разрешающего потенциала на входе 16 Расширение КОП с выхода схемы И 31 поступает разрешающий потенциал на выдачу адреса по расширенному коду операции через групу 27 элементов И и группу 30 элементов ИЛИ.

По разрешающему потенциалу с выхода 22 триггера 6 блокировки через группу 28 элементов И на группу 30 элементов ИЛИ вьщается адрес по внешним запросам с выхода 21 шифратора 1

По разрешающему потенциалу с входа 17 Управление ЦП через группу 25 элементов И и группу 30 элементов ШШ выдается адрес обращения памяти таблиц для чтения или записи информации

Если отсутствуют перечисленные Bbmie разрешения на вьщачу адресов, на выходе схемы И 33 появляется разрешение на выдачу адреса из микрокоманды для преобразования его в реальный адрес управляющей памяти. Этот адрес с выхода 14 2 группы 4 элементов И

выдается на группу 29 элементов И и далее на группу 30 элементов. РШИ.

Запись информации во все элементы памяти производится по сигналам внешней синхронизации.

Формула изобретения

Устройство микропрограммного управления, содержащее блок памяти микропрограмм, блок связи с памятью, регистр микрокоманды, группу элементов -И, регистр адреса, триггер блокировки, элемент ИЛИ, шифраторj причем первый вход данньк устройства соединен с первым информационным входом блока связи с памятью, первый информационный выход которого соеди

нен с информагрионным входом блока памяти микропрограмм, выход микроопераций которого соединен с вторым информаЦионным входом блока связи с памятью, второй информационный выход которого соединен с информационным входом регистра микрокоманд,, группа

-выходов поля микроопераций которого Q соединена соответственно с первыми

входами элементов И группы, кроме первого элемента И, выходы которых соединены с выходами микроопераций устройства, управляющий выход блока

g связи-,с памятью соединен с входом чтения-записи блока памяти микропрограмм, выход признака конца микропрограммы регистра микрокоманд соединен с первым входом первого элемейта И группы, первый вход логических условий устройства соединен с первым входом шифратора и с первым входом элемента ИЛИ, вьрсод которого соединен с информационным входом

5 триггера блокировки, выход которого соединен с вторыми входами элементов И группы, вход синхронизации устройства соединен с входами синхронизации триггера блокировок, регистра микрокоманд, блока связи с памятью, регистра адреса, выход регистра адреса соединен с адресным входом блока памяти микропрограмм, отличающееся тем, что, с целью расширения области применения за счет орга& низации косвенной адресации, оно

содержит блок памяти таблиц адресов, коммутатор, триггер, причем первый, второй и третий входы кода команды устройства соединены соответственно с первым, вторым и третьим информационными входами коммутатора, второй и третий входы логических условий устройства соединены соответственно с первым и вторым управляющими входами

5,коммутатора, выходы элементов И группы объединены и соединены с первым информационным входом регистра адреса и с четвертым информационным входом коммутатора, ыход которого сое0 динен с адресным входом блока памяти таблиц, выход которого соединен с вторым информационным входом регистра адреса, второй вход данных устройства соединен с информационным

5 входом блока памяти таблиц адресов, выход признака блокировки которого соединен с информационным входом триггера, выход которого соединен с вторым входом элемента ИЛИ и с вторым

0

.входом шифратора, выход которого соединен с пятым информационным входом коммутатора, выход триггера блокировки и выход первого элемента И группы соединены соответственно с третьим и четвертым управляющими входами коммутатора, первый вход задания режима устройства соединен с уп- равлякмцим входом блока связи с памяСоставитель А.Михайлов Редактор Е.Папп Техред М.ДвдыкКорректор. А.Тяско

Заказ 4223/39 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

тью, второй вход задания режима устройства, соединен с входом чтения- записи блока памяти таблиц адресов, выход признака наличия микропрограммы которого соединен с выходом микроопераций устройства, вход синхронизации устройства соединен с входом синхронизации триггера.

Фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1170457A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

Изобретение относится к вычисли- .тельной технике и может использоваться при построении микропрограммных процессоров. Цель изобретения - расширение области применения за счет организации механизма косвенной адресации. Устройство содержит блик 1 памяти микропрограмм, блок 2 связи с памятью, регистр 3 микрокоманд, группу элементов И 4, регистр 5 адреса, -триггер 6 блокировки, злемент ИЛИ 7, блок 8 памяти таблиц, коммутатор 9, триггер 10 и шифратор 11. Устройство обеспечивает динамическое преобразование логических адресов микрокоманд в реальные адреса управляющей памяти и динамическую загрузку микропрограмм в процессе вьтолне- ния программы. 2 ил. u.f

| Микропрограммный процессор | 1978 |

|

SU752341A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1185331, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1986-02-28—Подача