1

Г Изобретение относится к цифровой вычислительной технике и может быть использовано . в процессорах и блоках управления, использующих микро- j программный принцип работы.

Известно устройство микропрограммного управления,применяемое в IBM-360 модели 40, в котором используется постоянное запоминающее JQ устройство для хранения микропрограмм 1 .

Недостатком этого устройства является жесткий, неизменяемый набор микропрограмм.

Наиболее близким техническим решением к изобретению является устройство, которое содержит микропрограммный блок обработки данных, основную оперативную память и управляющую 2Q память 2 .

Вход микропрограммного блока обработки данных связан со входами управляющей памяти и основной оперативной памяти, а выходы основной 25 и управляющей памятей связаны соответственно с первым и вторым входами блока обработки данных, возможность (Перезагрузки управляющей памяти в процессоре используется для загруз-хл

ки разделов диагностических тестов с пультового накопителя.

Недостатком является неэффективное использование управляющей памяти в рабочем режиме.

Цель изобретения - расширение функциональных возможностей за счет осуществления пересылки микропрограмм из оперативной памяти в управляющую и увеличение быстродействия.

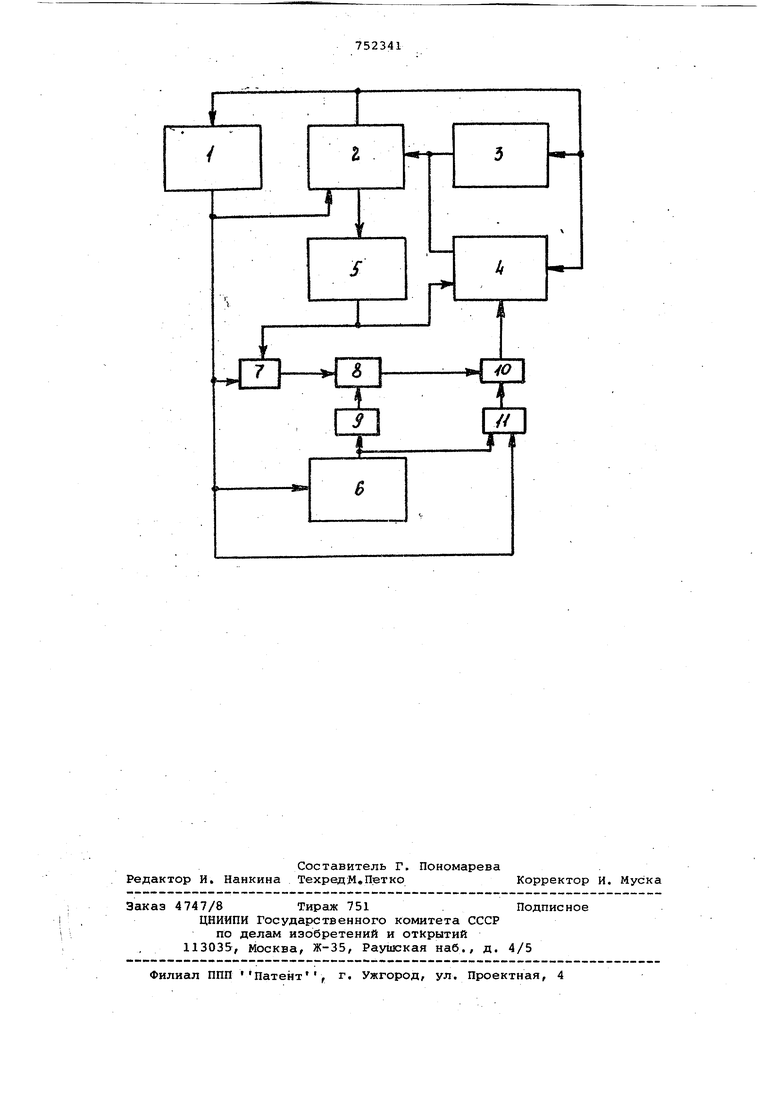

Эта цель достигается тем, что в микропрограммный процессор, содержащий блок обработки данных, первый вход которого соединен с выходом . основной оперативной памяти, второй вход блока обработки данных соединен с выходом управляющей памяти, управляющий вход которой соединен с управляющим выходом блока обработки данных и с управляющим входом основной оперативной памяти, введены дополнительная управляющая память, регистр указателя зоны, дешифратор настройки адресов, сумматор, элементы НВ, ИЛИ, первый и второй элементы И, причем выход блока обработки данных соединен со входом регистра указателя зоны, разрядный :выход которого соединен с первым входом сумматора и первым управляющим входом дополнительной управляющей памяти, второй управляющий вход которого соединен с управляющим выходом блока обработки данных, выход дополнительной управляющей памяти соединен со вторым входом блока обработки данных, а вход загрузки - с выходом элемента ИЛИ, первый и второй входы которого соединены с выходами первого и второго элементов И соответственно, первый вход первого элемента И соединен с выходом сумматора, второй вход которо го соединен с выходом основной оперативной памяти, с входом дешифратора настройки адресов и с первым входом второго элемента И, второй вход которого соединен с выходом дешифратора настройки адресов и через элемент НЕ - со вторым входом первого элемента И. На чертеже приведена схема устро ства. Микропрограммный процессор включает, основную оперативную память 1, блок 2 обработки данных, управляюаду память 3, дополнительную управляющую память 4, регистр 5 указателя зоны,i дешифратор 6 настройки адресо сумматор 7, элемент 8 И, элемент 9 НЕ, элемент 10 ИЛИ, элемент 11 И. Управляющая память 3 хранит микропрограммы базовой системы команд и различные управляквдие микропрограммы, например обработки программных прерываний, обслуживаниезапро сов от каналов, и другие. Выходные данные из управляющей памяти 3 поступают в блок 2 обработки данных. Блок 2 обработки данных производит выборку команд по счетчику из основ ной оперативной памяти 1 и передает управление по коду операции через микропрограмму выборки команд соответствующим микропрограммам-обработ команд. Дополнительная управляющая память 4 представляет оперативное запоминающее устройство, имеющее общую систему адресации с управляющей памятью 3. Эта память разделена на зоны фиксированной длины, в каждую из которых может быть загружена микропрограмма со своим идентификат ром из основной оперативной памяти 1. загрузка микропрограмм в дополнительную управляющую память 4 производится под управлением блока обработки данных и регистра 5 указателя зоны. в основной оперативной памяти 1 содержатся массивы программ и данных. Программы составлены из команд системы команд и кроме,того, вклю1чают подпрограммы/ состав ленные из микрокоманд, которые реализуют некоторые процедуры и.алгори мы. В эту базовую систему команд введена специальная команда Выполнить микропрограмму (ВМ), кото рая обеспечивает обращение к подпрограмме, в заголовке которой соержится идентификатор микропрограмы. Этот идентификатор представляет обой шестнадцатеричный код, однозначно определяющий данную микропрограмму, в команде ВМ имеется поле кода операции, поле начального адеса подпрограммы в основной операивной памяти 1 и поле длины подпрограммы. Команда ВМ, как и все другие коанды, выполняется микропрограммно од управлением блока 2 обработки анных. Команда ВМ считывает из основной оперативной памяти 1 идентификатор загружаемой микропрограммы и сравнивает с идентификаторами микропрограмм, размещенных в зонах дополнительной управляющей памяти 4. В случае совпадения идентификатора загружаемой микропрограммы с одним из идентификаторов зон дополнительной управляющей памяти 4 загрузка этой микропрограммы не производится, а управление непосредственно передается микропрограмме в дополнительной управляющей памяти 4. При несовпадении идентификаторов команда ВМ производит сканирование зон дополнительной управляющей памяти 4 на выбор зоны, в которую будет загружаться массив микроходов из основной оперативной памяти 1. Далее формируется указатель зоны, выбранной для загрузки, который засылается в регистр 5 указателя зоны. Идентификатор загружаемой микропрограммы передается дополнительной управляющей памяти 4 по адресу, который формируется из разрядов префикса, определяемых выходом регистра 5 указателя зоны, и разрядов относительного адреса в зоне, поступающих из блока 2 обработки данных. После каждой записи в дополнительную управляющую память 4 блок 2 обработки данных модифицирует на длину микрокоманды относительный адрес в зоне для последующей записи. Затем из основной оперативной памяти 1 последовательно считываются микрокоды в сумматор 7 и дешифратор 6 настройки адресов. Сумматор 7, элементы 8 и 11 И, элемент 9 НЕ и элемент 10 ИЛИ производят замещение части адресного поля микрокода префиксом из регистра 5 указателя зоны для микрокоманд передачи управления, определенных дешифратором 7 настройки еадресов, т.е. загружаемая мик,ропрограмма настраивается на нужную зону дополнительной управлякшей памяти 4. После загрузки микрокодов управление передается блоком обработки данных 2 3 агруженной микропрограмме.После выполнения микропрограммы управление, передается микропрограмме выборки команд в управляющей памяти 3. Использование подпрогра лм, соста ленных в микрокомандах, в теле рабочих и управляющих программ, повышает системную производительность ЭВМ. Это происходит потому, что язы микропрограммирования является языком самого низкого уровня и позво.чет эффективно использовать воз .можности аппаратуры устройства: сокращается интенсивность обраще ний к медленной оперативной памяти .(отсутствие выборки команд, для хранения данных и промежуточных результатов используются более быстро действующие запоминающие средства); имеется возможность работы со структурами данных малой размерности;имеется возможность организации групповых ветвлений; имеется достаточно высокая опера ционная плотность микрокоманд ( в одной микрокоманде реализуется несколько операций); микропрограммы выполняются из быстродействующей управляющей памяти. Возможность пересылки микропрограмм из оперативной в управ ляющую позволяет динамически изменять содержимое управляющей памяти и помещать туда микропрограммы, реа лизующие различные функции, ранее не входящие в комплект микропрограм Это является расширением функции микропрограммного управления. Формула изобретения Микропрограммный процессор, содержащий блок обработки данных, первый вход которого соединен с вы ходом основной оперативной памяти, второй вход блока обработки данных соединен с выходом управляющей памяти, управляющий вход которой соединен с управляющим выходом блока обработки данных и управляющим входом основной оперативной памяти, отличающийся тем, что, с целью повыиюния быстродействия и расширения функциональных возможностей за счет осуществления пересылки микропрограмм из основной оперативной памяти iS управлйющую, в него введены дополнительная управлянмдая память, регистр указателя зоны, дешифратор настройки адресов, сумматор, элементы НЕ, ИЛИ, первый и второй элементы И, причем выход блока обработки данных соединен со входом регистра указателя зоны, разрядный выход которого соединен с (Первым входом сукматора и первым управляющим входом дополнительной управляющей памяти, второй управляющий вход которого соединен с управляющим выходом блока обработки данных, выход дополнительной управляющей памяти соединен со вторым входом блока обработки данных, а вход загрузки - с выходом элемента ИЛИ, первый и второй входы которого соединены с выходами первого и второго элементов И соответственно, первый вход первого элемента И соединен с выходом сумматора, второй вход которого соединен с выходом основной оперативной памяти, с входом дешифратора настройки адресов и с первым входом второго элемента И, второй вход которого соединен с выходом дешифратора настройки адресов и через элемент НЕ - со вторым входом первого элемента И. Источники информации, принятые во внимание при экспертизе 1.Хассон С. Микропрограммное управление. Вып. 2, Мир,М., 1974, гл. 7. 2.Патент США; 3656123, кл; 340-172. 5, 11.04.72 (прото-тип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Процессор | 1976 |

|

SU670935A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1256036A1 |

Авторы

Даты

1980-07-30—Публикация

1978-07-17—Подача