Изобретение относится к преобра- зевательной технике и может быть использовано в системах управления преобразователями частоты модуляционног типа.

Целью изобретения является расширение функциональных возможностей устройства.

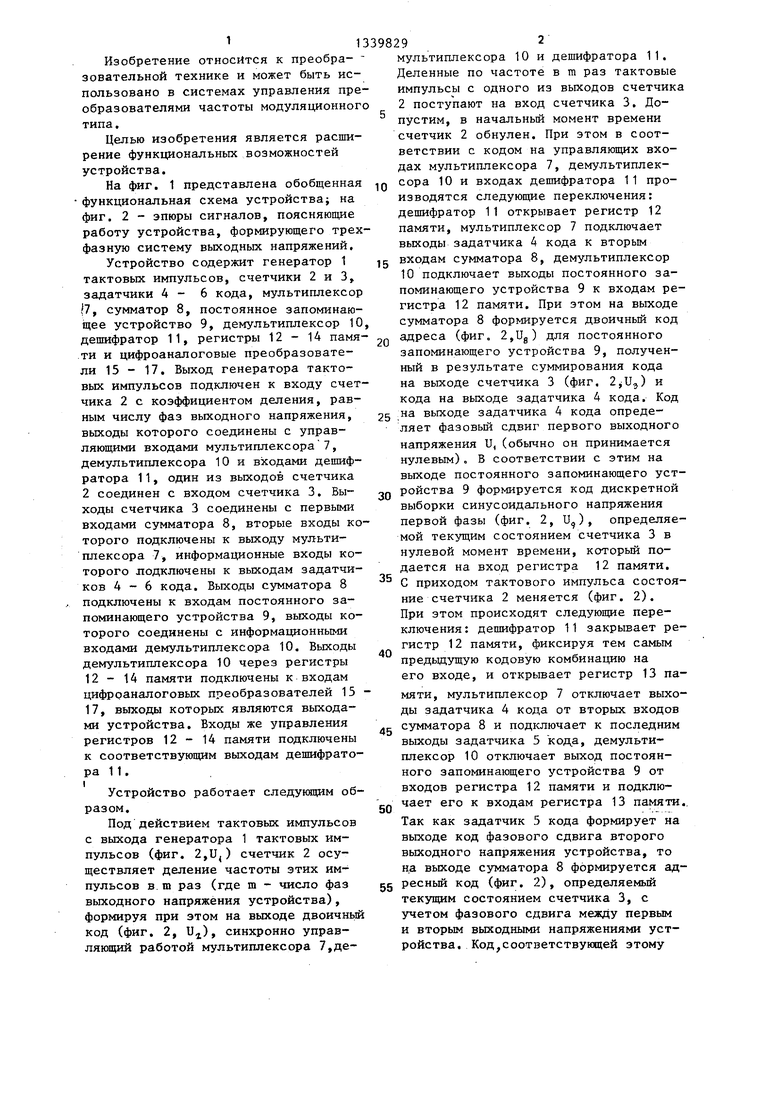

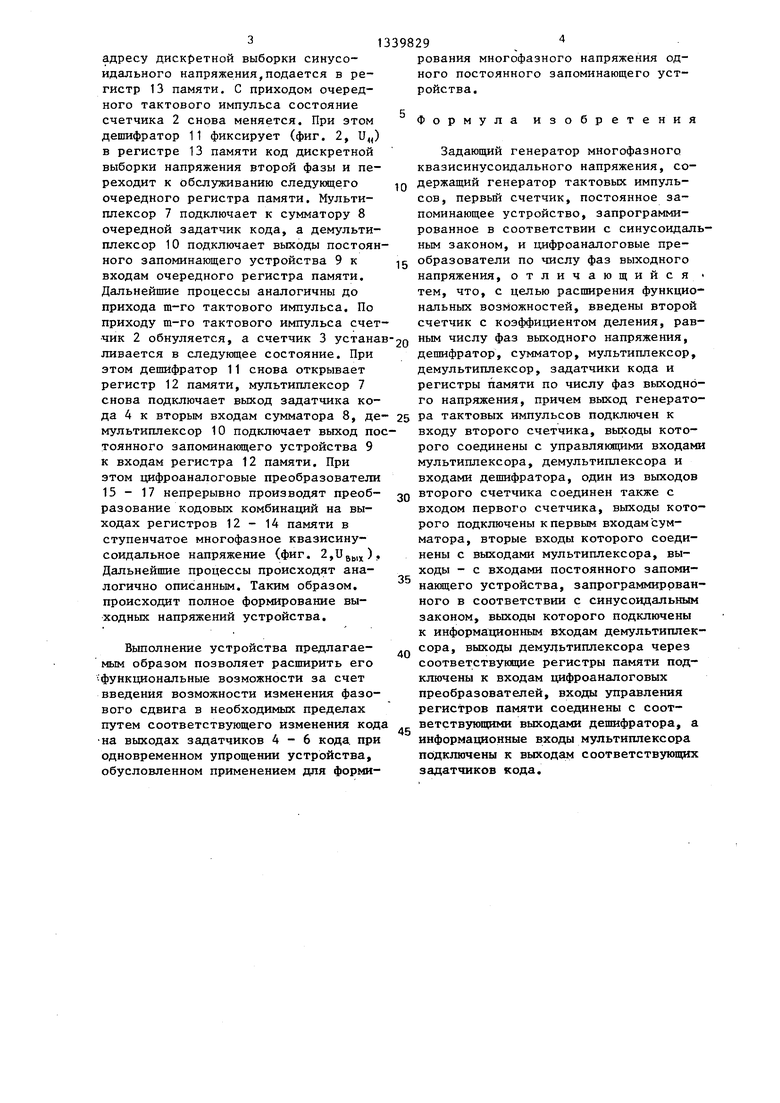

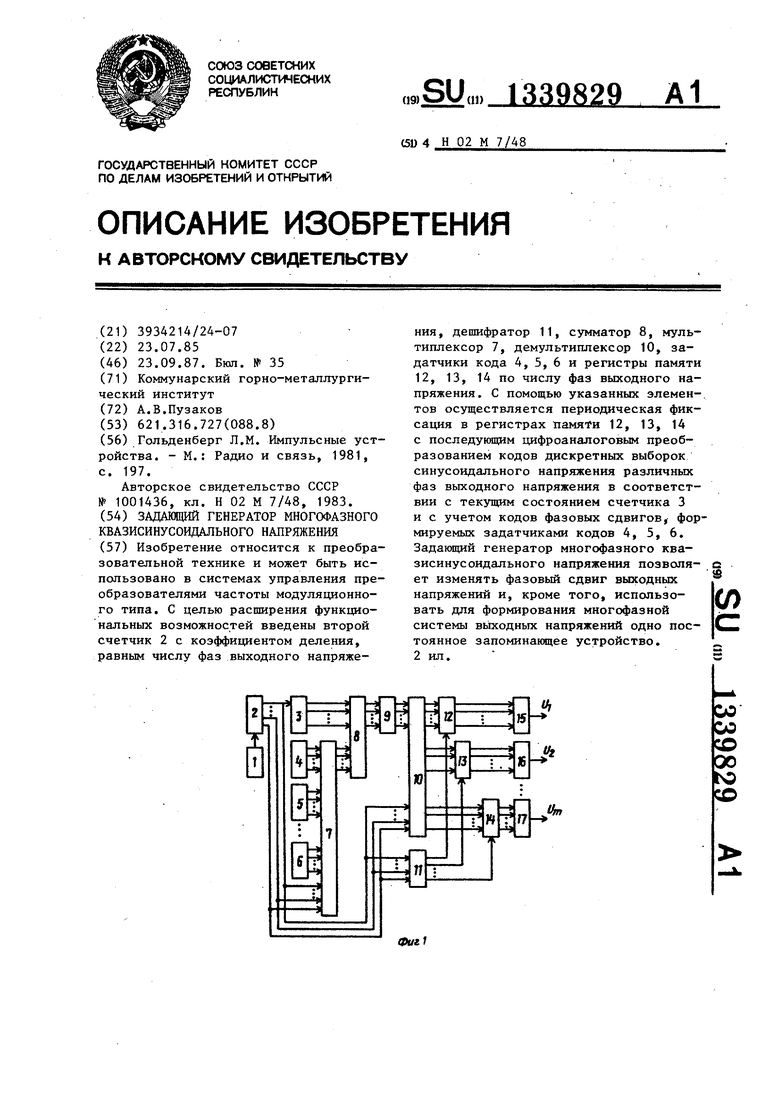

На фиг. 1 представлена обобщенная функциональная схема устройства; на фиг. 2 - эпюры сигналов, поясняющие работу устройства, формирующего трехфазную систему выходньк напряжений.

Устройство содержит генератор 1 тактовых импульсов, счетчики 2 и 3, задатчики 4-6 кода, мультиплексор 17, сумматор 8, постоянное запоминающее устройство 9, демультиплексор 10 дешифратор 11, регистры 12-14 памяти и цифроаналоговые преобразователи 15 - 17. Выход генератора тактовых импульсов подключен к входу счетчика 2 с коэффициентом деления, равным числу фаз выходного напряжения, выходы которого соединены с управляющими входами мультиплексора 7, демультиплексора 10 и входами дешифратора 11, один из выходов счетчика 2 соединен с входом счетчика 3. Выходы счетчика 3 соединены с первыми входами сумматора 8, вторые входы которого подключены к выходу мультиплексора 7, информационные входы которого лодключены к выходам задатчи- ков 4-6 кода. Выходы сумматора 8 подключены к входам постоянного запоминающего устройства 9, выходы которого соединены с информационными входами демультиплексора 10. Выходы демультиплексора 10 через регистры 12 - 14 памяти подключены к входам цифроаналоговых преобразователей 15 17, выходы которых являются выходами устройства. Входы же управления регистров 12 - 14 памяти подключены к соответствующим выходам дешифратора 1 1 .

Устройство работает следунищм образом.

Под действием тактовых импульсов с выхода генератора 1 тактовых импульсов (фиг. 2,Uj) счетчик 2 осуществляет деление частоты этих импульсов в. m раз (где m - число фаз выходного напряжения устройства), формируя при этом на выходе двоичньй код (фиг. 2, и), синхронно управляющий работой мультиплексора 7,де0

0

5

0

мультиплексора 10 и дешифратора 11. Деленные по частоте в m раз тактовые импульсы с одного из выходов счетчика 2 поступают на вход счетчика 3. Допустим, в начальный момент времени счетчик 2 обнулен. При этом в соответствии с кодом на управляющих входах мультиплексора 7, демультиплексора 10 и входах дешифратора 11 производятся следующие переключения: дешифратор 11 открывает регистр 12 памяти, мультиплексор 7 подключает выходы задатчика 4 кода к вторым

g входам сумматора 8, демультиплексор 10 подключает выходы постоянного запоминающего устройства 9 к входам регистра 12 памяти. При этом на выходе сумматора 8 формируется двоичный код адреса (фиг. 2,Ug) для постоянного запоминающего устройства 9, полученный в результате суммирования кода на выходе счетчика 3 (фиг. ) и кода на выходе задатчика 4 кода. Код .на выходе задатчика 4 кода определяет фазовый сдвиг первого выходного напряжения U, (обычно он принимается нулевым), В соответствии с этим на выходе постоянного запоминающего устройства 9 формируется код дискретной выборки синусоидального напряжения первой фазы (фиг. 2, U), определяемой текущим состоянием счетчика 3 в нулевой момент времени, который подается на вход регистра 12 памяти. С приходом тактового импульса состояние счетчика 2 меняется (фиг. 2). При этом происходят следующие переключения : дешифратор 11 закрывает регистр 12 памяти, фиксируя тем самым предыдушую кодовую комбинацию на его входе, и открьгоает регистр 13 памяти, мультиплексор 7 отключает выходы задатчика 4 кода от вторых входов

g сумматора 8 и подключает к последним выходы задатчика 5 кода, демультиплексор 10 отключает выход постоянного запоминающего устройства 9 от входов регистра 12 памяти и подклюQ чает его к входам регистра 13 памяти..

Так как задатчик 5 кода формирует на выходе код фазового сдвига второго выходного напряжения устройства, то н,а выходе сумматора 8 формируется ад- 5 ресный код (фиг. 2), определяемый текущим состоянием счетчика 3, с учетом фазового сдвига между первым и вторым выходными напряжениями устройства. Код,соответствующей этому

5

0

адресу дискретной выборки синусоидального напряжения,подается в регистр 13 памяти. С приходом очередного тактового импульса состояние счетчика 2 снова меняется. При этом дешифратор 11 фиксирует (фиг. 2, U,,) в регистре 13 памяти код дискретной выборки напряжения второй фазы и переходит к обслуживанию следующего очередного регистра памяти. Мультиплексор 7 подключает к сумматору 8 очередной задатчик кода, а демульти- плексор 10 подключает выходы постоянного запоминающего устройства 9 к входам очередного регистра памяти. Дальнейшие процессы аналогичны до прихода т-го тактового импульса. По приходу т-го тактового импульса счетчик 2 обнуляется, а счетчик 3 устаналивается в следующее состояние. При этом дешифратор 11 снова открывает регистр 12 памяти, мультиплексор 7 снова подключает выход задатчика кода 4 к вторым входам сумматора 8, де мультиплексор 10 подключает выход потоянного запоминакядего устройства 9 к входам регистра 12 памяти. При этом цифроаналоговые преобразователи 15 - 17 непрерывно производят преобразование кодовых комбинаций на выходах регистров 12-14 памяти в ступенчатое многофазное квазисинусоидальное напряжение (фиг. 2,Ug|,,),, Дальнейшие процессы происходят аналогично описанным. Таким образом, происходит полное формирование выходных напряжений устройства.

Выполнение устройства предлагаемым образом позволяет расширить его

функциональные возможности за счет введения возможности изменения фазового сдвига в необходимых пределах путем соответствующего изменения кода

на выходах задатчиков 4-6 кода, при одновременном упрощении устройства, обусловленном применением для формив- 25 с1339829

рования многофазного напряжения одного постоянного запоминающего устройства.

Формула изобретения

Задающий генератор многофазного квазисинусоидального напряжения, содержащий генератор тактовых импульсов, первый счетчик, постоянное запоминающее устройство, запрограммированное в соответствии с синусоидальным законом, и цифроаналоговые преобразователи по числу фаз выходного напряжения, отличающийся- тем, что, с целью расширения функциональных возможностей, введены второй счетчик с коэффициентом деления, рав- ным числу фаз выходного напряжения, дешифратор, сумматор, мультиплексор, демультиплексор, задатчики кода и регистры памяти по числу фаз выходного напряжения, причем выход генератора тактовых импульсов подключен к входу второго счетчика, выходы которого соединены с управлякицими входами мультиплексора, демультиплексора и входами дешифратора, один из выходов второго счетчика соединен также с входом первого счетчика, выходы которого подключены к первым входам сумматора, вторые входы которого соединены с выходами мультиплексора, выходы - с входами постоянного запоми- накнцего устройства, запрограммированного в соответствии с синусоидальным законом, выходы которого подключены к информационным входам демультиплексора, выходы демудьтиплексора через соответствую1цие регистры памяти подключены к входам цифроаналоговых преобразователей, входы управления регистров памяти соединены с соответствующими выходами дешифратора, а информационные входы мультиплексора подключены к выходам соответствующих задатчиков кода.

и

Фиг. 2

Составитель А.Меркулова

Редактор С.Пекарь Техред М.Дидык

Заказ 4241/52 Тираж 659Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производствен о-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для формирования базисно-тригонометрических функций | 1990 |

|

SU1792542A3 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Регулируемая мера фазовых сдвигов | 1986 |

|

SU1352401A2 |

| Фазовый модулятор | 1986 |

|

SU1388974A2 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Цифровой многофазный генератор | 1990 |

|

SU1750032A1 |

| ЦИФРОВОЙ МНОГОФАЗНЫЙ ГЕНЕРАТОР | 1992 |

|

RU2066918C1 |

| Цифровой регулятор температуры | 1986 |

|

SU1352470A1 |

Изобретение относится к преобразовательной технике и может быть использовано в системах управления преобразователями частоты модуляционного типа. С целью расширения функциональных возможностей введены второй счетчик 2 с коэффициентом деления, равным числу фаз выходного напряжения, дешифратор 11, сумматор 8, мультиплексор 7, демультиплексор 10, за- датчики кода 4, 5, 6 и регистры памяти 12, 13, 14 по числу фаз выходного напряжения. С помощью указанных элементов осуществляется периодическая фиксация в регистрах памяти 12, 13, 14 с последуницим цифроанапоговым преобразованием кодов дискретных выборок синусоидального напряжения различных фаз выходного напряжения в соответствии с текущим состоянием счетчика 3 и с учетом кодов фазовых сдвигов формируемых задатчиками кодов 4, 5, 6. Задающий генератор многофазного ква- зисинусоидального напряжения позволяет изменять фазовый сдвиг выходных напряжений и, кроме того, использовать для формирования многофазной системы вьпсодных напряжений одно постоянное запоьшнающее устройство. 2 ил. (Л DO :о 1 Ф(/гГ

| Гольденберг Л.М | |||

| Импульсные устройства | |||

| - М.: Радио и связь, 1981, с | |||

| Способ утилизации отработанного щелока из бучильных котлов отбельных фабрик | 1923 |

|

SU197A1 |

| Задающий генератор многоступенчатого трехфазного напряжения | 1980 |

|

SU1001436A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-09-23—Публикация

1985-07-23—Подача