устройство 27 отображения информации, Введение- новых элементов и образование новьгх связей между элементами устр-ва позволяют компенсировать сисИзобретение относится к измерительной технике и может найти применение в заводских и научно-исследовательских лабораториях для измерения скольлсенИя.

Целью изобретения является повышение точности измерения скольжения за счет компенсации систематической составляющей погрешности, вызванной нестабильностью питающего напряжения и уменьшения ее динамической .составляющей.

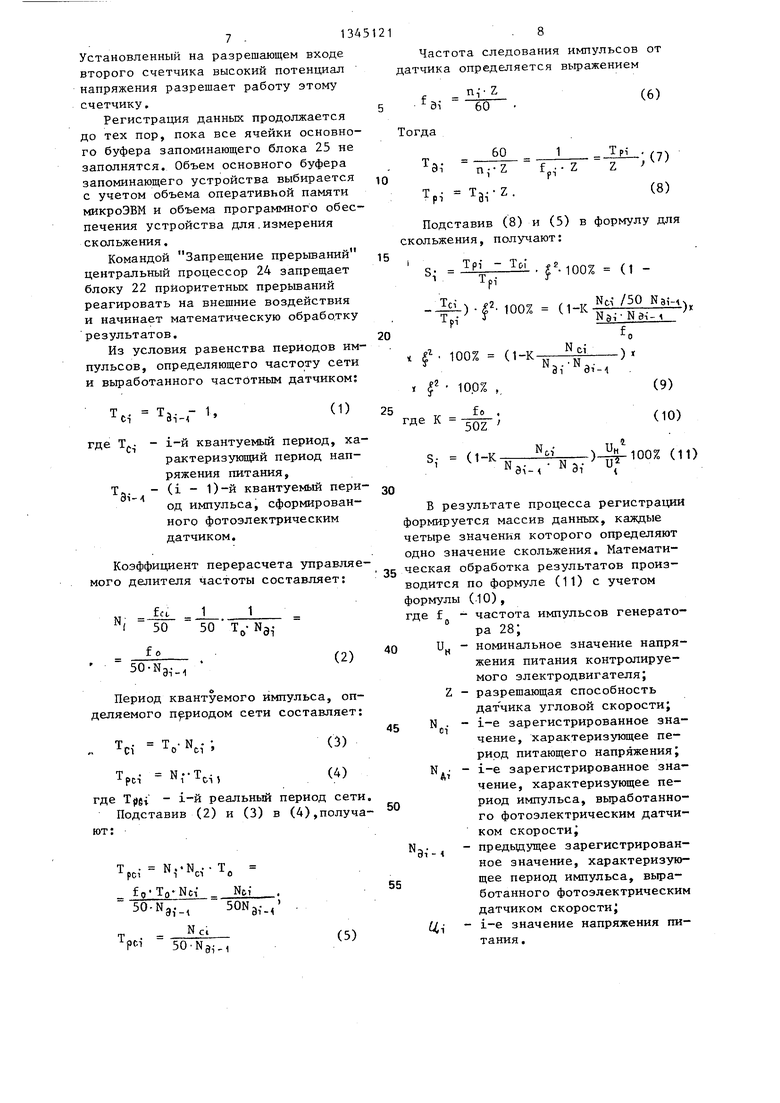

На фиг. 1 представлена структурна схема устройства для измерения сколь женин асинхронных электродвигателей, на фиг. 2 - алгоритм его работы, на фиг, 3 - временные диаграммы работы скользиметра,

Устройство для измерения скольже- ния асинхронных электродвигателей содержит фотоэлектрический датчик 1 скорости, который механически связан с валом контролируемого электродвигателя, первый формирователь 2, вход которого подключен к выходу фотоэлектрического датчика, а выход - к тактовому входу С первого триггера 3, прямой выход которого подключен к первому входу первой схемы 4 логического умножения, а инверсный - к первому входу второй схемы 5 логического умножения и к информационному входу D первого триггера 3, выход первой схемы 4 логического умножения соединен со входом четвертого счетчика ,6, а выход второй схемы логического .умножения 5 - со входом пятого счетчика 7, первый блок 8 выд.еле- ния положительного перепада, вход которого подключен к прямому выходу первого триггера 3, второй блок 9 вьщеления положительного перепада, вход которого соединен с инверсным выходом первого триггера 3, схему 10 логического сложения,, первый вход.

тематическую составляющую погрешности, -вызванную нестабильностью питающего напряжения, а также уменьшить ее динамическую составляющую, 6 лл.

5

0 5 о

5

5

которой подключен к выходу первого блока 8 вьщеления положительного перепада и к входу обнуления первого счетчика 6, а второй вход к выходу второго блока 9 выделения положительного перепада и к входу обнуления -ПЯТОГО счетчика 7, второй формирователь 11, вход которого подключен к промышленной электрической сети,, а выход - ко входу дискретного умножителя 12 частоты, управляемый делитель 13 частоты, вход которого соединен с выходом .дискретного умножителя 12 частоты, а выход - с тактовым входом второго триггера 14, масштабный делитель 15 напряжения, вход которого подключен к входу второго формирователя 11, а выход - к входу аналого- цифрового преобразователя 16, первый ;шинный формгдрователь 17, информационный вход которого соединен с выходом четвертого счетчика 6, а вход Выборка кристалла - с выходом второго блока 9 выделения положительного пе- репада, второй шинный формирователь 18, информационный вход которого под-, ключен к выходу пятого счетчика 7, а вход Выборка кристалла - к выходу схемы вьщеления положительного перепада, информационный вьгход аналого-цифрового преобразователя 16 соединен с каналом А, а сигнальный - Конец преобразования - с четвертым разрядом канала С первого параллельного интерфейса 19, выходы первого 17 и второго 18 шинньк формирователей подключены к управляющему входу управляемого делителя 13 частоты,а также к каналам А. и В второго параллельного интерфейса 20, а второй и четвертый разделы кан;ала с этого ин- терфейса соединены с выходом схемы 10 логического сложения, прямой выход второго триггера 14 подключен к разрешающему входу второго счетчика программируемого таймера 21 и к вто10

15

20

3 .1345121

рому входу блока 22 приоритетных прерываний, а инверсный-- к разрешающему входу первого счетчика программируемого таймера 21 и к первому входу блока 22 приоритетных прерьша- ний, нулевой вход соединен с выходом схемы 10 логического сложения, системную шину 23, посредством которой центральный процессор 24 связан с запоминающим блоком 25, блоком 26 отображения информации и другими блоками, входящими в состав микроЭВМ 27, и генератор 28 импульсов, выход которого подключен к вторым входам первой 4 и второй 5 схем логического умножения, а также к тактовым входам счетчиков программируемого таймера 21,

Устройство для измерения скольжения асинхронных электродвигателей работает в соответствии с алгоритмом, представленным на фиг. 2, и временными диаграмтчгами, представленными на фиг. 3.

При подаче напряжения питания на устройство.центральный процессор 24 согласно программе инициализации дает команду Запрещение прерываний и . осуществляет программирование внешних устройств, так что канал А первого параллельного интерфейса, 19 работает на стробируемый ввод, каналы А и В второго параллельного интерфейса 20 работают на стробируемый .ввод . Счетчики СТ1 и СТ2 программируемого таймера 21 работают в режиме счета импульсов тактовой частоты.

При работе каналов параллельного интерфейса в стробируемом режиме (режим 1) разделы канала С играют роль шин управления. Четвертый разряд является входом строба записи канала А, второй разряд - входом стро

буфер канала А первого параллельног интерфейса 19, стирая предьщущее за писанное в нем значение. Циклы изме рения напряжения промышленной элект рической сети идут непрерывно, след вательно, буфер канала А первого параллельного интерфейса 19 хранит последнее зарегистрированное значение реального напряжения питания контролируемого электродвигателя. В одной из ячеек вспомогательного буф ра запоминающего блока 25 хранится код номинального напряжения питания контролируемого электродвигателя.

Дискретный умножитель 12 частоты настроен на умножение частоты сети с коэффициентом, равным f./50, таки образом на вход управляемого делителя 13 поступают импульсы частотой „,/50.

Подпрограмма инициализации завер шается выводом сообщения Включите контролируемый электродвигатель и 25 командой Разрешение прерываний, после чего центральный процессор 2 переходит в режим ожидания.

Первый импульс, поступивший на тактовый вход С первого триггера 3, переводит его в состояние, противоположное исходному, например, из О в 1. Фронт этого импульса, вьщеле ный первой схемой 8 выделения положительного перепада, обнуляет четвертый счетчик 6. Установившийся ур вень высокого напряжения на первом входе первой схемы логического умно жения 4 разрешает прохождение импул сов тактовой частоты на вход четвертого счетчика 6 в течение времени, определяемого периодом первого импульса, сформированного фотоэлектрическим датчиком 1 угловой скорости.

Первый импульс, поступивший на

30

35

40

ба записи канала В. При записи инфор- тактовый вход второго триггера 14,мации в буферы каналов параллельным интерфейсом формируются сигналы Подтверждение записи и Запрос прерывания .

Напряжение питания контролируемо- 50 то электродвигателя, преобразуясь масштабным делителем 15 напряжения и аналого-цифровым преобразователем 16 в цифровой код, по сигналу Конец преобразования, формируемому 55 аналого-цифровым, преобразователем 16 и поступающему на вход четвертого разряда канала С первого параллельного интерфейса, переписывается в

также переводит его в состояние, противоположное исходному, например из О в 1. Установившийся высокий уровень напряжения на прямом выходе второго триггера дает разрешение на работу второму счетчику программируемого таймера 21 в течение периода первого импульса, поступившего на вход второго триггера 14.

Второй импульс, поступивший на тактовый вход С первого триггера 3, переводит его в нулевое состояние. Фронтом этого импульса вьщеленным вторым блоком 9 вьщеления положитель

0

5

0

буфер канала А первого параллельного . интерфейса 19, стирая предьщущее записанное в нем значение. Циклы измерения напряжения промышленной электрической сети идут непрерывно, следовательно, буфер канала А первого параллельного интерфейса 19 хранит последнее зарегистрированное значение реального напряжения питания контролируемого электродвигателя. В одной из ячеек вспомогательного буфера запоминающего блока 25 хранится код номинального напряжения питания контролируемого электродвигателя.

Дискретный умножитель 12 частоты настроен на умножение частоты сети с коэффициентом, равным f./50, таким образом на вход управляемого делителя 13 поступают импульсы частотой „,/50.

Подпрограмма инициализации завершается выводом сообщения Включите контролируемый электродвигатель и 5 командой Разрешение прерываний, после чего центральный процессор 24 переходит в режим ожидания.

Первый импульс, поступивший на тактовый вход С первого триггера 3, переводит его в состояние, противоположное исходному, например, из О в 1. Фронт этого импульса, вьщелен- ный первой схемой 8 выделения положительного перепада, обнуляет четвертый счетчик 6. Установившийся уровень высокого напряжения на первом входе первой схемы логического умножения 4 разрешает прохождение импульсов тактовой частоты на вход четвер . того счетчика 6 в течение времени, определяемого периодом первого импульса, сформированного фотоэлектрическим датчиком 1 угловой скорости.

Первый импульс, поступивший на

0

5

0

также переводит его в состояние, противоположное исходному, например из О в 1. Установившийся высокий уровень напряжения на прямом выходе второго триггера дает разрешение на работу второму счетчику программируемого таймера 21 в течение периода первого импульса, поступившего на вход второго триггера 14.

Второй импульс, поступивший на тактовый вход С первого триггера 3, переводит его в нулевое состояние. Фронтом этого импульса вьщеленным вторым блоком 9 вьщеления положительного перепада обнуляется пятый счетчик 7. В счетчике 6 фиксируется число N. Tj - fj,, где Та - период первого импульса, сформировапного частотным датчиком 1. Одновременно с описанным сформированный блоком 9 выделения положительного перепада импульс, поступивший на вход Выборка кристалла первого шинного формирователя 17J переписывает зафиксированное число N3, на вход каналов А и В второго параллельного интерфейса 20. Этот же импульс через схему 10 логического сложения поступает на стробирующие входы записи и переписывает информацию в буферы каналов А и В, Это же число поступает

на информационный вход управляемого делителя 13 частоты. Высокий уровень напряжения, установившийся на первом входе схемы 5 логического умножения, разрешает прохождение импульсов тактовой частоты с выхода генератора 28 импульсов на вход второго счетчика 7 в течение периода второго импульса, пришедшего на тактовый вход С втброго триггера 14. Обрабатывая прерывание, вызванное по нулевому входу блока 22 приоритетных прерываний, центральный процессор 24 считывает содержимое буферов каналов А и В второго параллельного интерфейса в ячейки основного буфера запоминающего блока 25, отведенного под регистрируемые значения. В третью ячейку центральный процессор 24 пересьшает код реального напряжения электрической сети, хранящийся в буфере канала А. первого параллельного интерфейса 19. После этого центральный процессор 24 возвращается в режим ожидания.

Второй импульс, поступивший на вход второго триггера 14, переводит его в состояние О. Установившийся на инверсном выходе этого триггера высокий потенциал фиксирует во счетчике программируемого таймера 21 число Nj, Tj, 50Z и дает

.разрешение на работу первому счетчику программируемого таймера 21 в течение периода второго импульса, поступившего на вход второго триггера 14. Обрабатывая вызванное опрокидыванием триггера 14 прерывание по первому входу блока 22 приоритетных прерываний, центральный процессор 24 пересьшает в ячейки блока 25 па

мяти содержимое второго счетчика программируемого таймера 21. Перегрузив счетчик, центральный процессор 24 возвращается к режим ожидания. Третий импульс, поступивший на вход С первого триггера 3, снова переводит его в состояние 1. Фронтом импульса четвертый счетчик 6 обнуляQ ется, а установившийся на первом входе схемы 4 логического умножения высокий уровень напряжения- разрешает работу счетчика 6 на период следования третьего импульса, выработанно5 го частотным датчиком 1 . В счетчике

7фиксируется число Nj ТЗг о

8момент опрокидывания триггера 3 из О в 1 формируется импульс, который, поступив на вход Выборка

0 кристалла второго шинного, формиро- вателя 18, переписывает зарегистрированное значение на информационный вход управляемого делителя 13 частоты и на входы каналов А и В второго

5 параллельного интерфейса 20. Этот же импульс через схему 10 логического сложения поступает на стробирующие входы каналов, записывает зафиксированное значение Ng; в буферы

0 каналов А и В второго параллельного интерфейса 20. Он же вызывает прерывание по нулевому входу блока 22 приоритетных прерываний. Следуя этому сигналу, центральный процессор 24 переносит содержимое буферов каналов А и В второг о параллельного интерфейса 20 ячейки основного буфера запоминающего блока 25 в следующую ячейку, считывает содержимое каВ

нала А первого параллельного интерфейса 19, после чего возвращается к режиму ожидания.

Третий импульс, поступивший на вход второго триггера 14, переводит

его в состояние 1 на время следования третьего импульса, характеризующего период питающего напряжения. Установившийся на прямом выходе триггера 14 уровень логической 1

фиксирует в первом счетчике програм мируемого таймера 21 число Т(,2 50 Обрабатывая прерывание, вызванное по второму входу блока 22 приоритетных прерываний,

центральный процессор 24 пересылает зафиксированное значение в основной буфер запоминающего блока 25. Перезагрузив счетчик, центральный процессор 24 возвращается в режим ожидания,

7 .13А

Установленный на разрешающем входе второго счетчика высокий потенциал напряжения разрешает работу этому счетчику.

Регистрация данных продолжается до тех пор, пока все ячейки основного буфера запоминающего блока 25 не заполнятся. Объем основного буфера запоминающего устройства выбирается с учетом объема оперативной памяти микроэвм и объема программного обеспечения устройства для.измерения скольжения.

Командой Запрещение прерьшаний центральный процессор 24 запрещает блоку 22 приоритетных прерываний реагировать на внещние воздействия и начинает математическую обработку результатов.

Из условия равенства периодов импульсов, определяющего частоту сети и вьфаботанного частотным датчиком;

ci Зт-Г

(1)

i-й квантуемый период, характеризующий период напряжения питания,

(1-1)-й квантуемый пери- ,„ . ,

од импульса, сформированного фотоэлектрическим датчиком.

Коэффициент перерасчета управляемого делителя частоты составляет:

N;

fa 1 1

50 50 Т,-N9,- fo

SO-Ng..,

(2)

Период квантуемого импульса, оп- деляемого периодом сети составляет:

(3) (4)

где Tjjgi - i-й реальный период сети. Подставив (2) и (3) в (4),получа- °

ют:

Т N . N Т

РС1 т С1 0

- fp Tp-NcT Nbi

50-N

3i-i

N.

50«э,ч,

Pf-i 50. N9.,,

Частота следования импульсов от датчика определяется выражением

Пт Z

(6)

Тогда

60

n--z р. Z

-т pi . ,,ч

-7 Л

(8)

Подставив (8) и (5) в формулу для скольжения, получают:

S- . 100% (1 - J- pi

-)-f400% (i-K-l i- l bhi),

т pi JNa-i N Эт- л

- 100% ()

« 100% ,

где К

fo . 50Z

(9) (10)

S (1-к-- iii--)iioo% (11)

Ng.,- N9,- Uf

35

40

45

°

55

в результате процесса регистрации формируется массив данных, каждые четьфе значения которого определяют одно значение скольжения. Математическая обработка результатов производится по формуле (11) с учетом формулы (-10) ,

где f - частота импульсов генератора 28;

Uj, - номинальное значение напряжения питания контролируемого электродвигателя; Z - разрешающая способность

датчика угловой скорости; N. - i-e зарегистрированное значение, характеризующее период питающего напряжения N. - i-e зарегистрированное значение, характеризующее период импульса, вьфаботанного фотоэлектрическим датчиком скорости

Ng- - предыдущее зарегистрированное значение, характеризующее период импульса, выработанного фотоэлектрическим датчиком скорости; - i-e значение напряжения питания .

По окончании математической обработки полученная информагдия выводится на потребитель.

Формула изо б.р е т е и и я Устройство для измерения скольже- -ния асинхронных .электродвигателей, содержащее фотоэлектрический датчик первый формирователь, генератор импульсов, второй формирователь, два вентиля и вычислительный блок, о т- личающееся тем, что, с целью уменьшения погрешности измерения, в него дополнительно введены два триггера, два счетчика, два блока выделения положительного перепада,; схема логического сложения, два шинных формирователя, дискретный ум- :ножитель частоты, управляемый дели-. .тель частоты, масштабный дели- . тель напряжения, аналого-гщфровой преобразователь, а вычислительный блок выполнен в виде микроЭВМ, причем выход механически связанного с контролируемым электродвигателем фотоэлектрического датчика соединен с входом первого формирователя, выход ifcoToporo подключен к тактовому входу первого триггера, прямой выход первого триггера соединен с входом первого блока вьщеления положитель- ного перепада и с первым входом первой схемы логического умножения, а инверсньй - с входом второго блока выделения положительного перепада, с первым входом второй схемы логического умножения и с информационным входом первого триггера, вход, первого счетчика подключен к выходу первой схемы логического умножения, а выход - к входу первого шинного формирователя, вход второго счетчика соединен с выходом второй схемь логического умножения, а выход с входом второго шинного формирователя, выход первого блока вьщеления положительного перепада подключэн к первому входу схемы логического сложения, к входу обнуления первого счетчика и к входу Выборка кристалла второго шинного формирователя, а выход второго блока вьщеления цоложи0

5

0

5

0

5

0

5

0

тельного перепада - к второму входу схемы логического сложения, к входу обнуления второго счетчика и к входу Выборка кристалла первого шинного формирователя, выходЫ шинных формирователей соединены с каналами А и В второго параллельного интерфейса и с управляющим входом управляемого делителя частоты, вход второго формирователя подключен к входу масштабного делителя напряжения и к промьшшенной электрической сети, а выход - к тактовому входу дискретного умножителя частоты, выход которого в свою очередь подключен к тактовому входу управляемого делителя частоты, тактовый вход второго триггера соединен с выходом управляемого делителя частоты, прямой выход - с разрешающим входом второго счетчика

программируемого таймера и с. вторым входом блока приоритетных прерываний,

а инверсный - с разрешающим входом первого счетчика программируемого таймера, с первым входом блока приоритетных прерывателей и с информа- . ционным входом второго триггера, выход схемы логического сложения подключен ко второму и четвертому разрядам канала С второго параллельного интерфейса и к нулевому входу блока приоритетных прерываний, вход аналого-цифрового преобразователя.соединен t выходом масштабного делителя напряжения, информационный выход - с- каналом А первого параллельного интерфейса, а сигнальньш Конец преобразования - с четвертым разрядом канала С этого же интерфейса, выход генератора импульсов подключен к вторым входам схем логического унножения, а также к тактовьм входам первого и второго Счетчиков программируемого таймера, посредством системной шины центральный процессор связан с запоминающим блоком, блоком отображения информации, параллельными интерфейсами, программируемым таймером и блоком приоритетных прерьюаний, входящими в состав микро - ЭВМ.

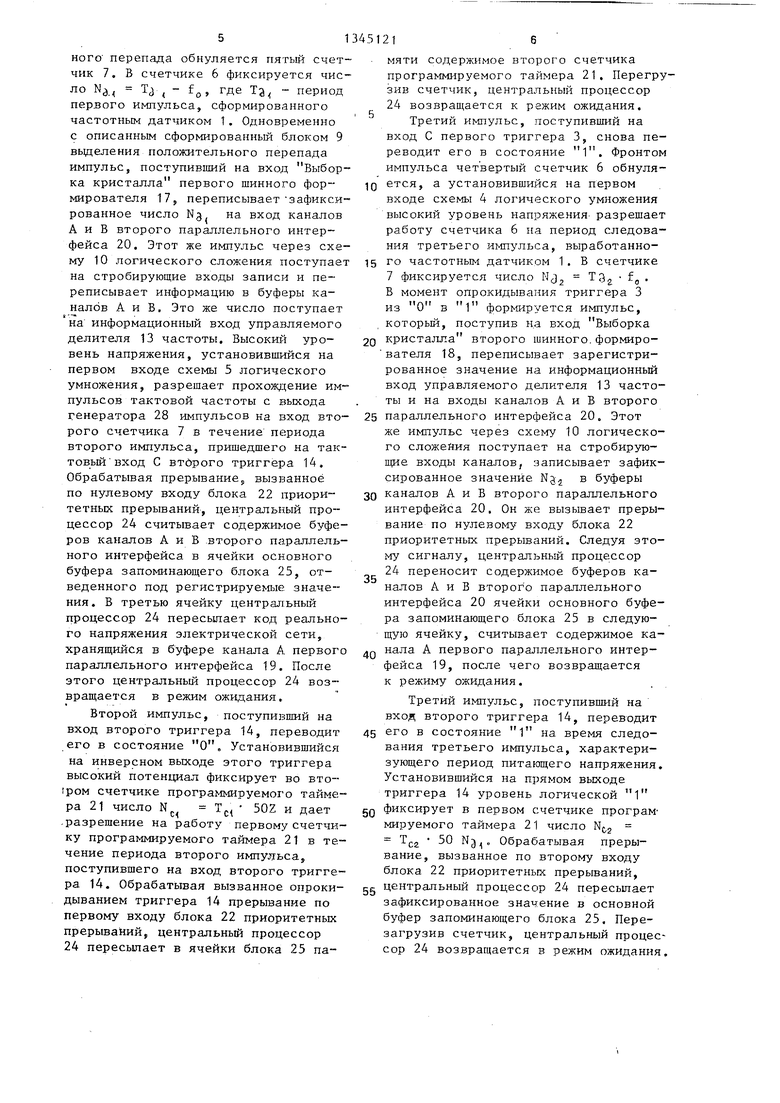

С

Начала

nodnpotpama инициализации

Ожидание

О;кидание

Считывание содержа- нога KS пи г

ало работы yc/npoucmSo

I

Ожидание

зпрг

yi

Уйелтение адреса ЗУ

CvumtiSoHue содержимого КАЛИ г

ySejiuveffue адреса

CvumbiSoHue совер- тиноео KAfMI

Запись Б 3У сод ер- жипого СТ1ПТ

Увели кние оареса

ЗУ

ySemveHoe овреса

П ерузно СП Пт

ЭПР1

.1 jiifi

ОжаЯание К

ЗЛРО

Зопхь S ЗУ содержиHOtO СТ2 ПТ

увеличение адреса ЗУ

Перегрузка сгг ПТ

Прекращение petucmpatfuu

1

{Нагпематииеская I обрадо/п№О заре- I ifuc/nflupoScrHH jr I зтуений у

1

Вывов pfjy Mxrmut МО ycmpoi/cmSo от}фа ге/л/л fififm- нации

С

I

Конец

л

ЭПР1

jiifi

.l

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения разности частот вращения | 1986 |

|

SU1613959A1 |

| Устройство для измерения скольжения | 1988 |

|

SU1615617A1 |

| Устройство для измерения скольжения | 1988 |

|

SU1658098A1 |

| Устройство для измерения параметров вращения | 1986 |

|

SU1613960A1 |

| Устройство для поиска информации на магнитной ленте | 1986 |

|

SU1597912A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1474635A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И ОБРАБОТКИ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2004 |

|

RU2260192C1 |

| Способ стабилизации толщины изоляции кабеля и устройство для его реализации | 1982 |

|

SU1302248A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| МИКРОПРОЦЕССОРНЫЙ ЭЛЕКТРОПРИВОД | 1998 |

|

RU2141164C1 |

Изобретение относится к измерительной технике. Цель изобретения - повышение точности измерения сколь-. жения. Устр-во содержит датчик 1 скорости, формирователи 2, 11, 17 и 18, триггеры 3, 14, схемы 4 и 5 логического умножения, счетчики 6 и 7, блоки 8 и 9 выделения положительного перепада, схему 10 логического сложения, умножитель 12 частоты, делитель 13 частоты, делитель 15 напряжения, аналого-цифровой преобразователь 16, интерфейсы 19 и 20, прог- раммируемьш таймер 21, блок 22 приоритетных прерываний, шину 23, процессор 24, запоминающее устр-во 25 и i СЛ

K1

X

К8,М

мг

Редактор Л.Повхан

Фиг:3

Составитель Ю.Мручко

Техред И. Попович Корректор М.Демчик

Заказ 4914/44Тираж 776Подписное

ВНИИПИ Государственного KOhfflTeTa СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ПЬ

П

Ь

,

| Dunnwald Johannes | |||

| Didi tale Drehzah lerfassung elektrischer Autriebe mit Mikrorectiner Techn | |||

| Mess, tm | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Ковалев A.M | |||

| Цифроаналоговый измеритель скольжения электрических машин | |||

| - Известия высших учебных заведений | |||

| Приборостроение, 1978, т | |||

| XXI, № 2, с | |||

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

Авторы

Даты

1987-10-15—Публикация

1986-01-12—Подача