Изобретение относится к электротехнике и может быть использовано в источниках вторичного электропитания электро- и радиоаппаратуры.

Целью изобретения является повышение надежности за счет увеличения допустимой кратности резервирования при снятии ограничений на общее число преобразовательных модулей.

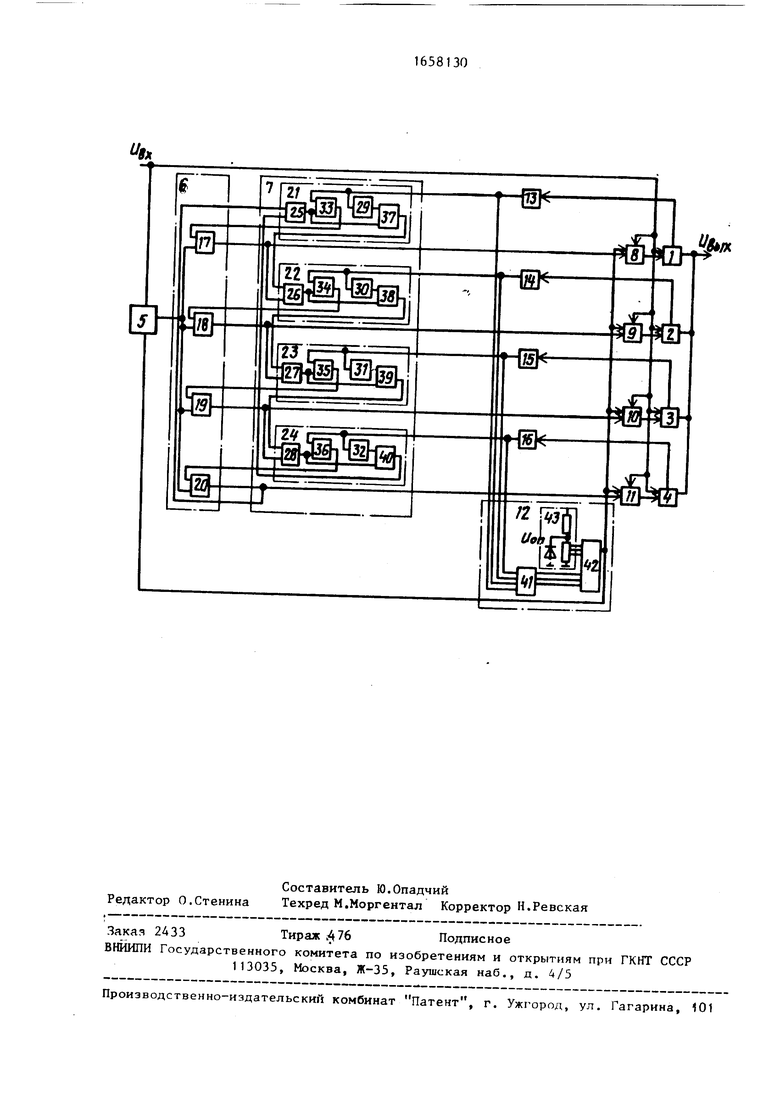

На чертеже приведена структурная схема многофазного параметрического стабилизатора постоянного напряжения.

Многофазный параметрический стабилизатор постоянного напряжения содержит преобразовательные модули 1...4 и блок управления. Блок управления включает генератор 5 тактовых импульсов, распределитель 6 тактовых импульсов, блок 7 логики, формирователи 8... 11 ширины импульсов, управляемый источник 12 опорного напряжения, датчики 13 - 16 отказов.

Каждый преобразовательный модуль 1...4 состоит из соединенных по понижающей схеме ключевого транзистора и LCD-фильтра. Дроссель фильтра имеет силовую и дополнительную обмотки.

о ел

00 СО

Распределитель 6 тактовых импульсов выполнен по схеме регистра сдвига на основе П-триггеров 17...20 и имеет п дополнительных входов, образованных подключением входов триггеров.

Клок 7 логики состоит из ячеек 21 ... 24 переключения. Каждая ячейка переключения содержит элемент ИЛИ 25 для ячейки 21 (26...28 для ячеек 22...24), элемент НЕ 29 (30...32) и два элемента И - первый 33 (34...36) и второй 37 (38...40) и снабжена тремя входами и двумя выходами.

Каждый формирователь ширины импульсов имеет три входа и один выход. Каждый из датчиков 12.„.15 отказов включает двухполупериодную схему выпрямления с емкостным фильтром и схему допускового контроля напряжения, реагирующую как на повышение, так и на снижение напряжения на дросселе фильтра. Датчик отказов имеет один выход.

Управляемый источник 12 опорного напряжения содержит постоянное запоминающее устройство 41, аналоговый мультиплексор 42 и задатчик 43 уровней опорных напряжений (в простейшем виде, приведенном на схеме, параметрический стабилизатор напряжения из последовательно включенных балластного резистора и стабилитрона и на- грузочного резистора, включенного параллельно стабилитрону).

Постоянное запоминающее устройство 41 имеет четыре адресных входа и три выхода, аналоговый мультиплексор 42 - три адресных входа и три входа канала коммутации, задатчик уровней опорного напряжения - три выхода. Управляемый источник 12 опорного напряжения имеет четыре входа и один выход Входы источника 12 образованы подключением адресных входов постоянного запоминающего устройства 41, а выход - подключением выхода аналогового мультиплексора 42.

Силовые входы и выходы преобразовательных модулей 1...4 подсоединены к входу и выходу стабилизатора параллельно. Входы генератора 5 тактовых импульсов соединены с входной шиной и с выходом управляемого источника 12 опорного напряжения, а выход генератора - с входом распределителя 6 тактовых импульсов. Выходы распределителя 6 подключены к первым ВХОДАМ фор мирователей 8... 11 ширины импульсов

0

5

0

5

0

5

0

5

0

5

и к вторым входам ячеек переключения блока / логики. Первые входы и выходы ячеек 21 ... 24 переключения использованы для их соединения в кольцо. Вторые входы формирователей 8 ... 11 ширины импульсов соединены с выходом управляемого источника 12 опорного напряжения, а третий - с входной шиной. Выходы формирователей 8... 11 ширины импульсов соединены с управляющими входами преобразовательных модулей 1-4. Входы датчиков 13...16 отказов подсоединены к дополнительным обмоткам дросселей фильтров модулей, а их выходы соединены одновременно с третьими входами ячеек 21...24 переключения и с входом управляемого источника 12 опорного напряжения. В источнике 12 опорных напряжений выходы постоянного запоминающего устройства 41 соединены с адресными входами аналогового мультиплексора 42, входы каналов коммутации мультиплексора соединены с выходами задатчика 43 опорного напряжения.

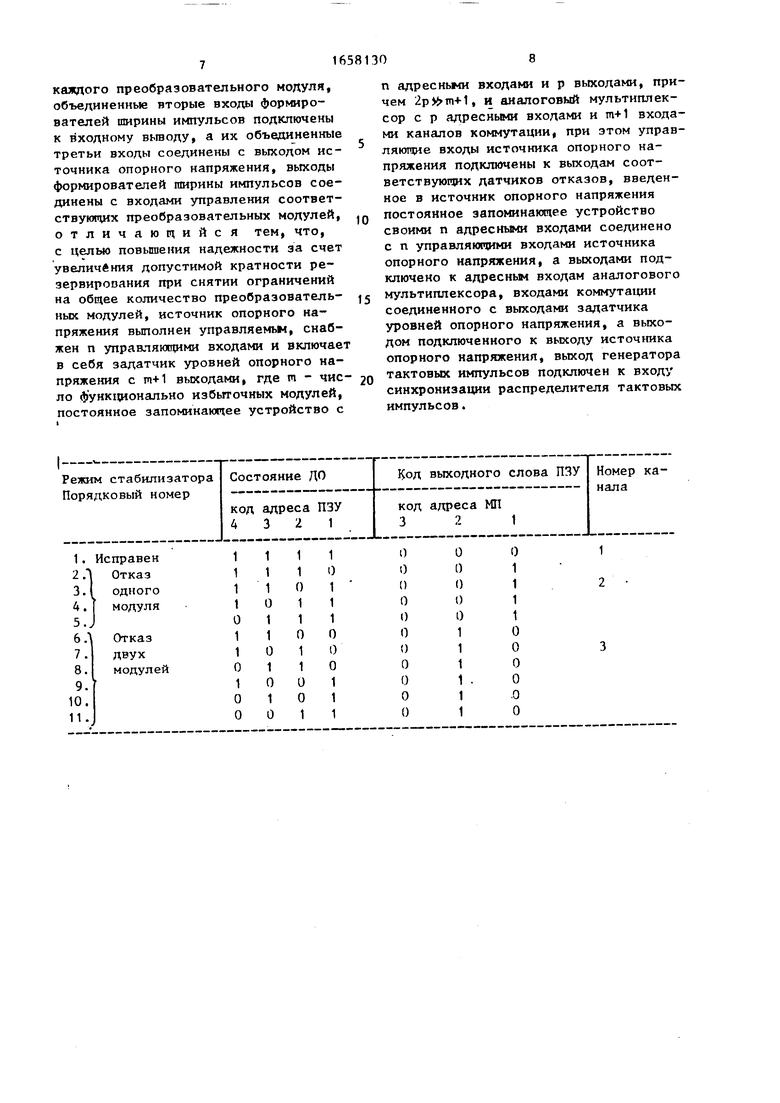

Соответствие между уровнями выходного напряжения датчиков отказов (ДО), кодом адреса постоянного запоминающего устройства (ПЗУ), кодом выходного слова ПЗУ, кодом адреса аналогового мультиплексора, номером включенного канала аналогового мультиплексора и величиной опорного напряжения Uon указано в таблице.

Работа многофазного параметрического стабилизатора постоянного напряжения рассматривается в режиме запуска и работы стабилизатора со всеми исправными модулями, и в режиме работы стабилизатора при отказе одного или нескольких модулей.

В режиме запуска устройство работает следующим образом. В исходном состоянии при исправных модулях выходное напряжение датчиков отказов имеет уровень логической единицы (лог.1), который сохраняется в течение всего времени нормальной работы модуля. При включении генератора 5 тактовые импульсы поступают на вход распределителя импульсов и последовательно распределяется по формирователям ширины импульсов с временным сдвигомЈ 1/4. Так как состояние всех датчиков отказов соответствует лог . 1, то включен первый канал аналогового мультиплексора и опорное напряжение иоп (по3 1 таблицы) .

При отказе одного из модулей, например модуля 2, датчик отказов 14 переходит в нулевое состояние (лог.О) Распределитель 6 и блок / логики распределяют импульсы последовательно по модулям, минуя отказавший модуль 2 Это происходит следующим образом. Так как на выходе датчика 14 появляется лог.О, то напряжение на входе элемента И 34 равно лог.О, а на входе элемента И 38 - лог. 1, которые сохраняются в течение всего времени работы стабилизатора с отказавшим модулем. Тогда напряжение с выхода триггера 17 поступает через элемент ИЛИ 26, элемент И 38, элемент ИЛИ 27, элемент 35 на вход триггера 19. На входе D-триг- гера 18 сохраняется лог.О. Следовательно, очередной тактовый импульс переводит триггер 17 в нулевое состояние, а в единичное переводится триггер 19. На третьем выходе распределителя 6 появляется импульс напряжения, а затем при поступлении очередных так товых импульсов - на четвертом и первом. Следовательно, при отказе одного модуля временной сдвиг между процессами изменяется и период переключения ключевых транзисторов исправных моду- лей становится равным . Одновременно с изменением состояния датчика отказов изменяется код адреса ПЗУ л соответственно код адреса аналогового мультиплексора. При этом вклю- чается канал 2 и опорное напряжение становится равным Uon /4 (поз.З таблицы).

Аналогичные процессы происходят при отказе любого модуля (поз. 2-5).

При отказе еще одного модуля, например модуля 4, датчик 16 отказов переходит в нулевое состояние. При этом распределитель 6 и блок 7 логики распределяют тактовые импульсы по исправным модулям 1 и 3. Период переключения ключевых транзисторов становится равным . Одновременно с изменением состояния датчика 16 из- меняется код адреса ПЗУ и соответственно код адреса диалогового мультиплексора. Включается канал 3 аналогового мультиплексора и на входы формирователей ширины импульсов и генератора тактовых импульсов поступает опорное напряжение, равное UQfl . Аналогичные процессы происходят при отказе любых двух модулей.

JQ 1520 2530 5

.Q

.с о

5

Формула изобретения

Многофазный параметрический стабилизатор постоянного напряжения, содержащий силовую цепь в виде п параллельно соединенных между входным и выходным выводами преобразовательных модулей, каждый из которых имеет информационный выход и управляющий вход и состоит из последовательно соединенных ключевого элемента и LCD-фильтра, блок управления, включающий в себя генератор тактовых импульсов, распределитель тактовых импульсов с п выходами, блок логики, п формирователей ширины импульсов, каждый из которых имеет три входа и выход, п датчиков отказов и источник опорного напряжения, при этом распределитель тактовых импульсов включает в себя n D-триггеров, выходами подключенных к соответствующим выходам распределителя тактовых импульсов, объединенными входами синхронизации соединенных с входом синхронизации, а D-входами с п дополнительными входами упомянутого распределителя тактовых импульсов, блок логики состоит из п одинаковых ячеек переключения, каждая из которых имеет три входа и два выхода и включает в себя элементы ИЛИ, НЕ и два элемента И, причем входы элемента ИЛИ соединены с первым и вторым входами каждой ячейки переключения, третий вход которой подключен к первому входу первого элемента И и через элемент НЕ - к первому входу второго элемента И, выход элемента ИЛИ соединен с вторыми входами элементов И, выходы элементов И соединены соответственно с первым и вторым выходами ячейки переключения, первый выход каждой ячейки переключения подключен к соответствующему дополнительному входу распределителя тактовых импульсов, второй выход каждой из ячеек переключения подсоединен к первому входу последующей ячейки переключения, каждый i-й выход распределителя тактовых импульсов подключен к первому входу 1-го формирователя ширины импульсов и второму входу каждой i+1 ячейки переключения, третий вход каждой ячейки переключения подключен к выходу соответствующего датчика отказов, выполненного на основе двухуровневого порогового элемента и входом подсоединенного к информационному выходу

каждого преобразовательного модуля, объединенные вторые входы формирователей ширины импульсов подключены к входному выводу, а их объединенные третьи входы соединены с выходом источника опорного напряжения, выходы формирователей ширины импульсов соединены с входами управления соответствующих преобразовательных модулей, отличающийся тем, что, с целью повышения надежности за счет увеличения допустимой кратности ре- зервиропания при снятии ограничений на общее количество преобразовательных модулей, источник опорного напряжения выполнен управляемым, снабжен п упраапяющими входами и включает в себя задатчик уровней опорного напряжения с гл+1 выходами, где m - число функционально избыточных модулей, постоянное запоминающее устройство с

5

0

п адресными входами и р выходами, причем , и аналоговый мультиплексор с р адресными входами и т+1 входами каналов коммутации, при этом управляющие входы источника опорного напряжения подключены к выходам соответствующих датчиков отказов, введенное в источник опорного напряжения постоянное запоминающее устройство своими п адресными входами соединено с п управляющими входами источника опорного напряжения, а выходами подключено к адресным входам аналогового мультиплексора, входами коммутации соединенного с выходами задатчика уровней опорного напряжения, а выходом подключенного к выходу источника опорного напряжения, выход генератора тактовых импульсов подключен к входу синхронизации распределителя тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный параметрический стабилизатор напряжения постоянного тока | 1988 |

|

SU1628057A1 |

| Многофазный импульсный стабилизатор напряжения | 1983 |

|

SU1156032A1 |

| Устройство для управления многофазным импульсным регулятором | 1981 |

|

SU957411A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1979 |

|

SU855639A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1386976A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935914A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1386977A1 |

| Устройство для управления многофазным импульсным преобразователем | 1990 |

|

SU1791943A1 |

Изобретение относится к источникам вторичного электропитания радиоэлектронной аппаратуры. Целью изобретения является повышение надежности за счет увеличения допустимой кратности резервирования при снятии ограничений на общее количество преобразовательных модулей. Моменты включения преобразовательных модулей 1...4, работающих на общую нагрузку, определяются коэффициентом деления распределителя 6 тактовых импульсов. /1ат- чики 13...16 отказов, подключенные к каждому преобразовательному модулю, контролируют его работу и в случае выхода из строя при помощи блока 7 логики запрещают подачу управляющих импульсов на отказавшие модули. Поэтому при отказе одного из модулей частота переключения оставшихся модулей возрастает, что при параметрическом способе стабилизации ведет к увеличению выходного напряжения. Чтобы этого не произошло, источник 2 опорного напряжения выполняется регулируемым таким образом, что его выходное напряжение пропорционально числу работающих преобразовательных ячеек. Поэтому при уменьшении числа работающих модулей реальная величина опорного напряжения уменьшается, а выходное напряжение остается на требуемом уровне. 1 ил. ,1 табл (Л

| Многофазный импульсный стабилизатор постоянного напряжения | 1979 |

|

SU855639A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Многофазный параметрический стабилизатор постоянного напряжения | 1987 |

|

SU1483439A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-06-23—Публикация

1989-03-09—Подача