Ичобретение относится к пычисли- тел).1(1Й технике и может быть нсполь- зоппно при создании аналого-цифровых устройств и систем лля моделирования динамических объектов и систем управ в реалр ном масштабе времени.

Целью изобретения является повышение точности вычислений па счет расширения диапазона задания временных сигналов If обеспечения непрерывного изменпния премер запуска программ цифровой чаг/ги в процессе решения .

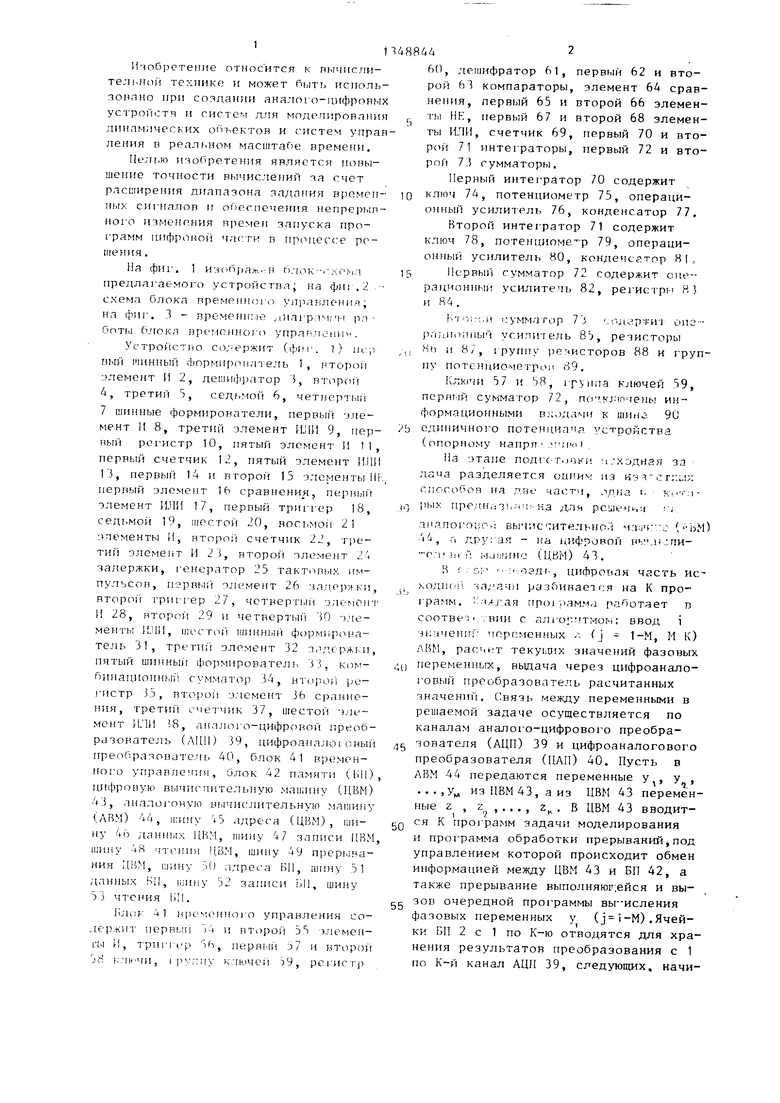

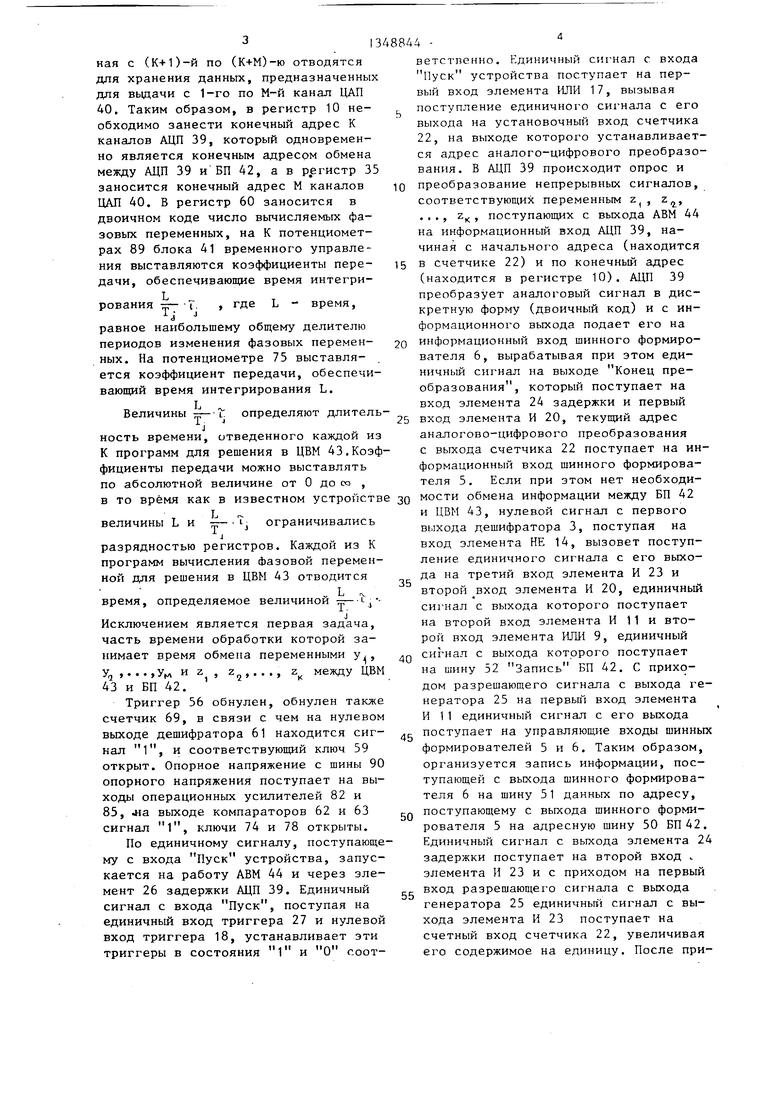

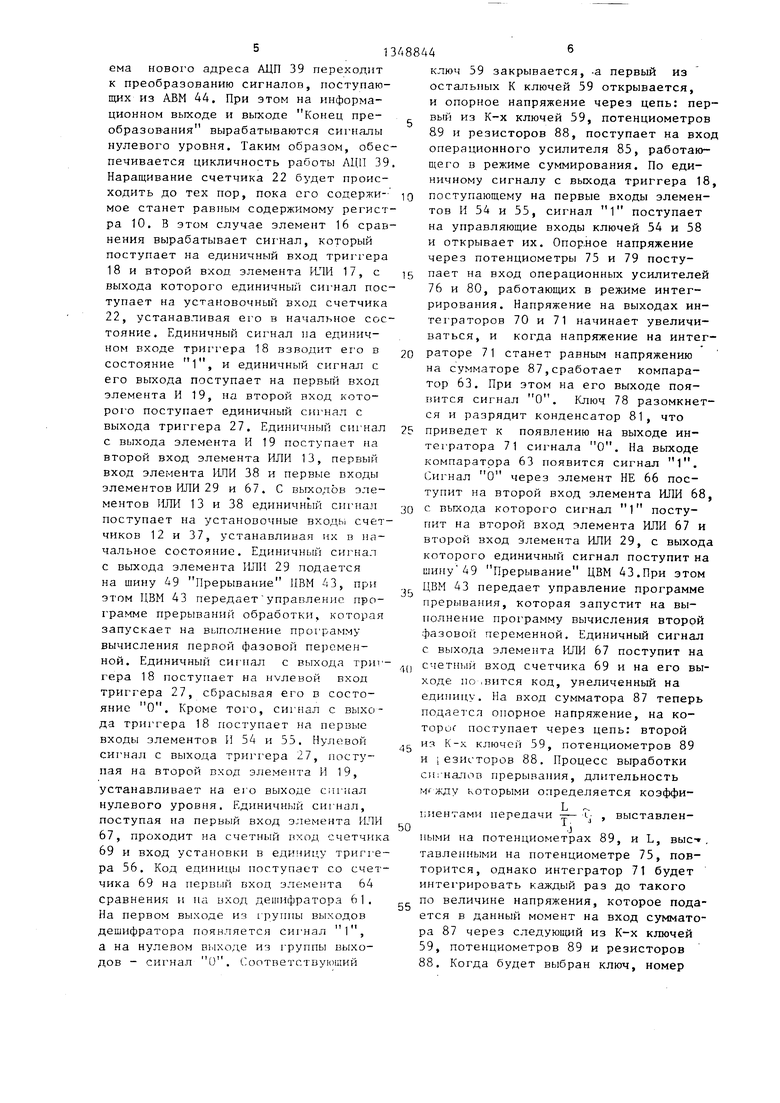

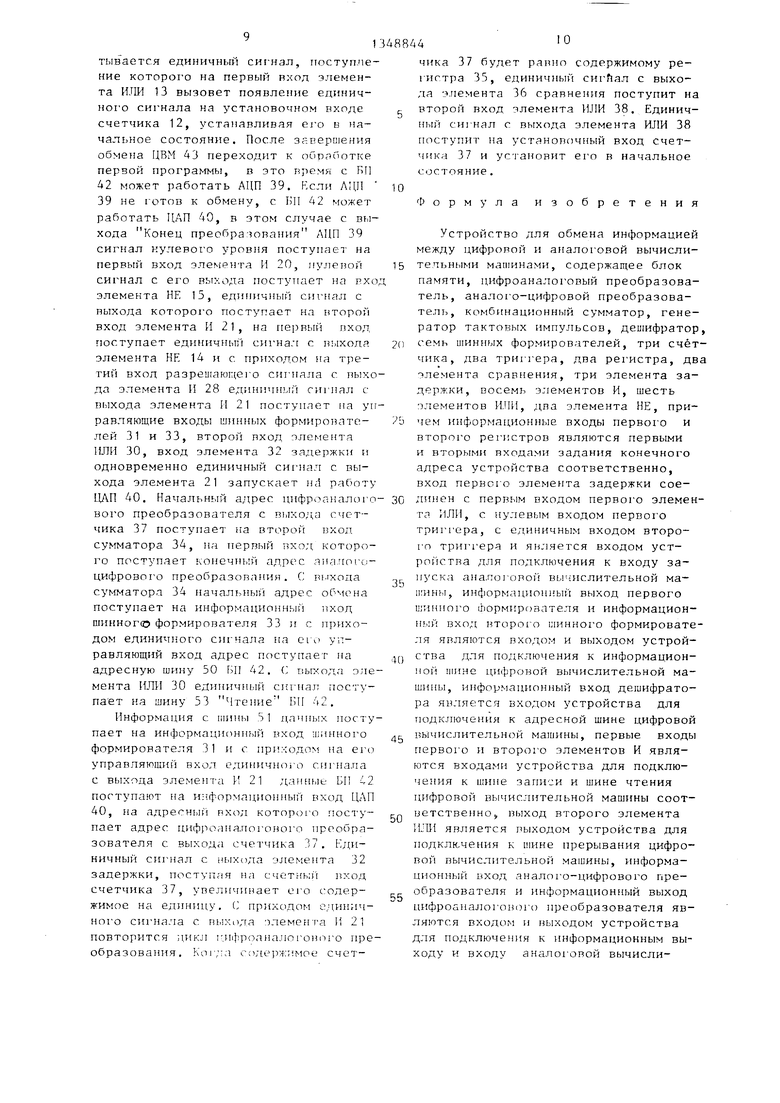

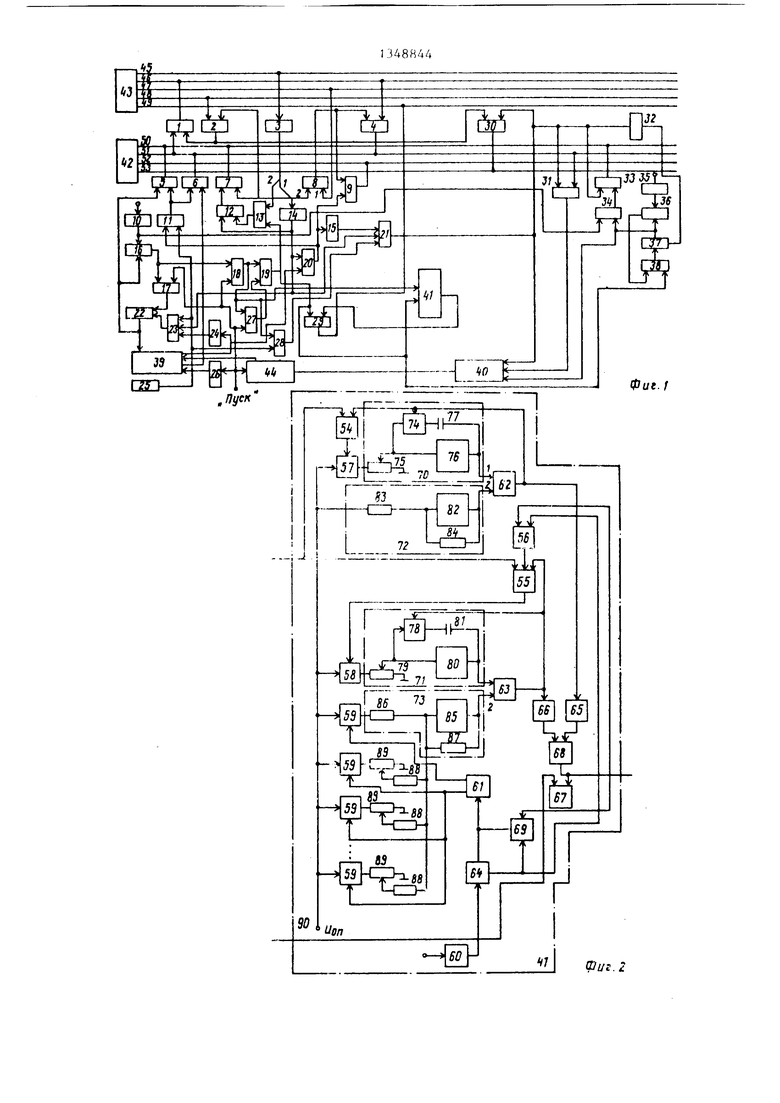

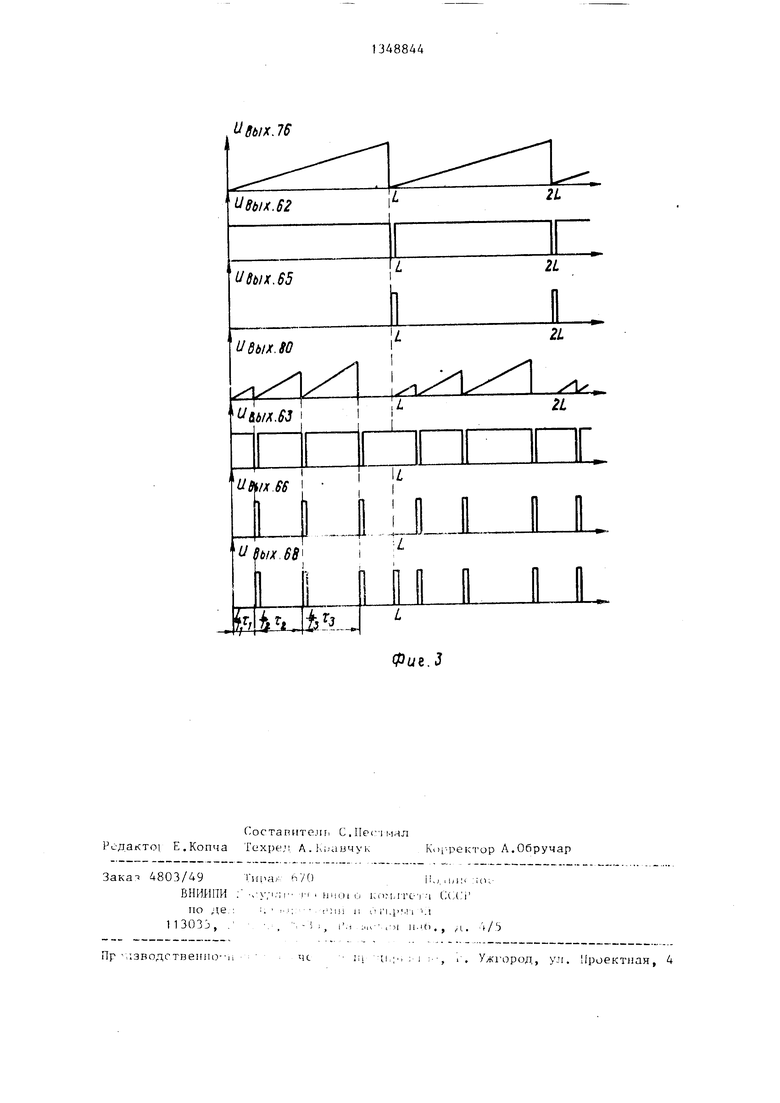

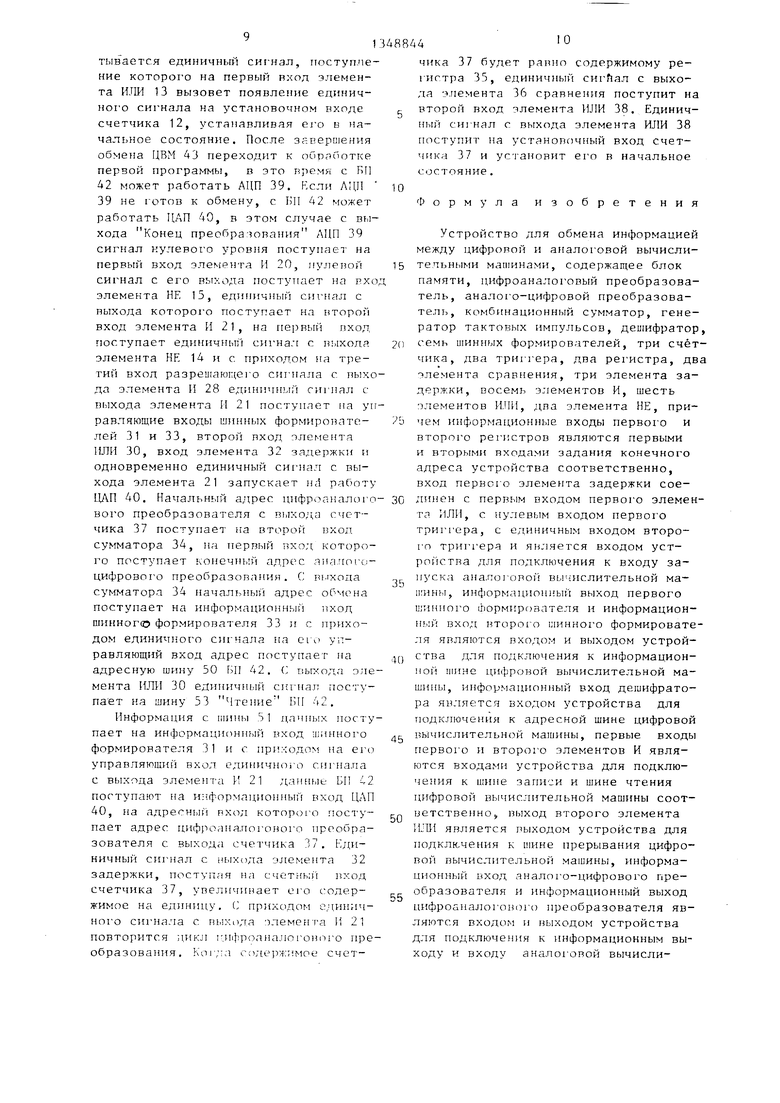

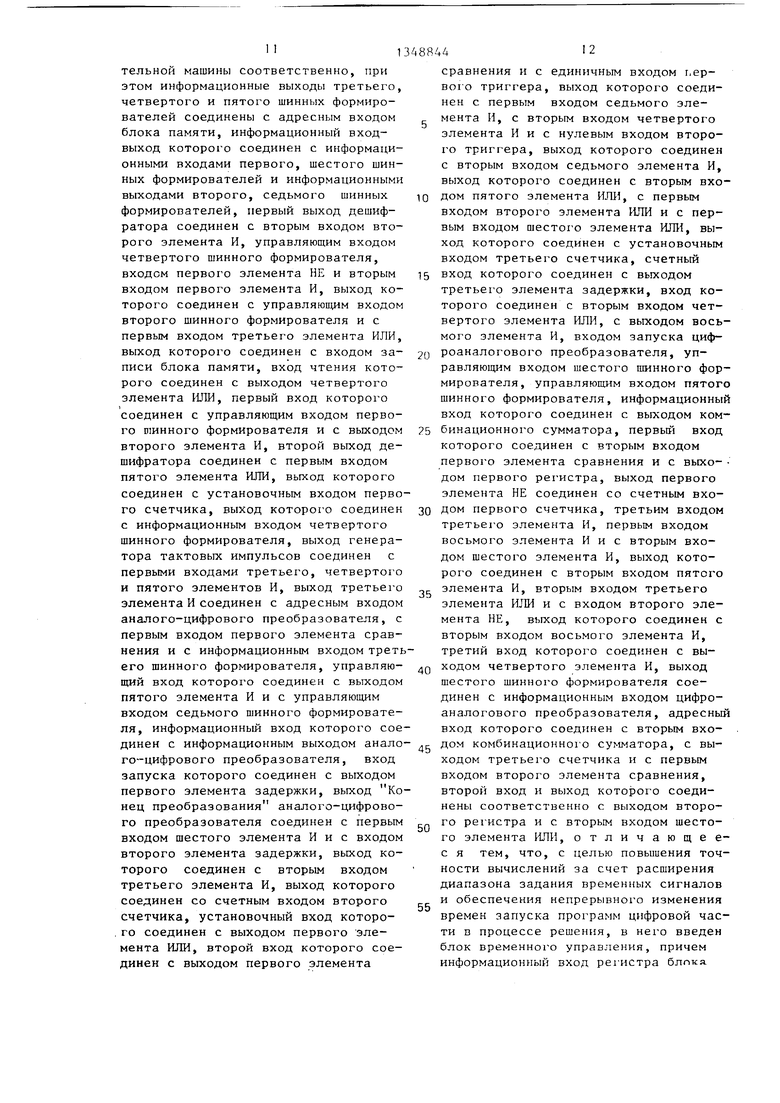

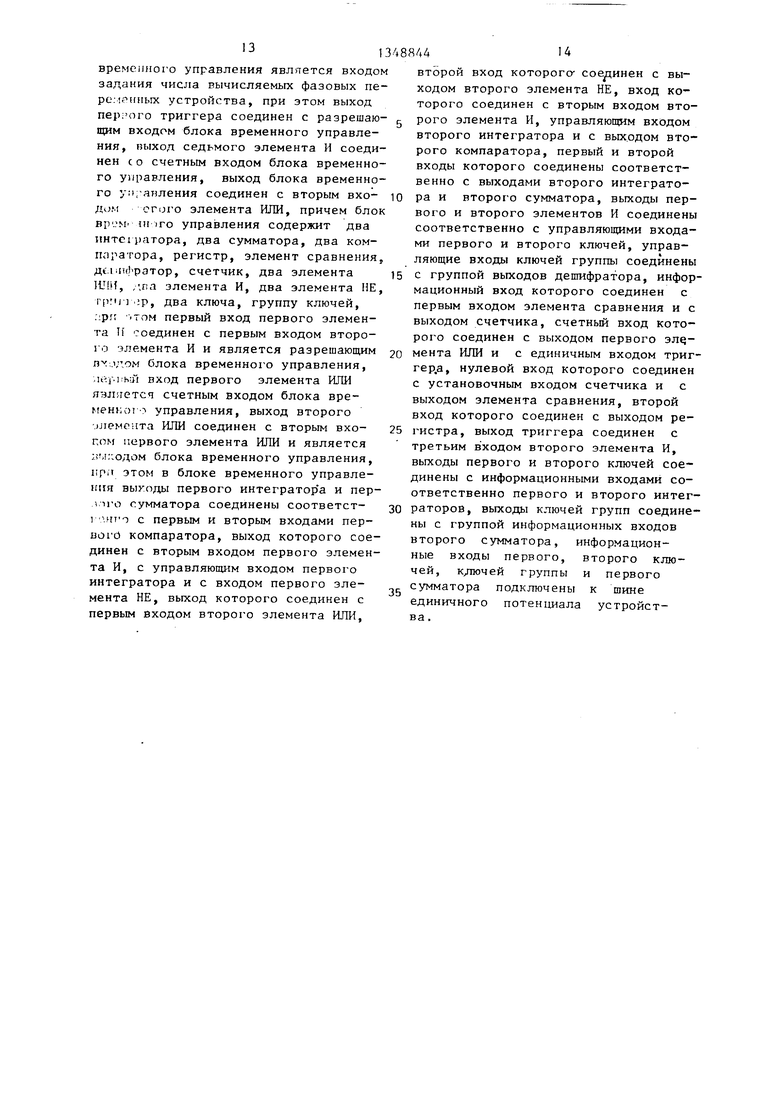

Ня фиг. 1 б,ч о к -.:.-.; о ,ч иредла1 аемо1-о устройства; на фиг,2 - схема блока време пи;1 |;ч управленггя; на . 3 - преме П(,|е ,|,иа1-р.:гчг ы работы блока врег-icHHc/j-o упраг .псни ,

УСТРОЙСТ1Ш со; ержит ((tx.u . 1) ni-p вый 1ПИННЫЙ 1)орм11ронатель 1, I Topoii элемент И 2, )атор i, второй 4, третий 5, сед(,мой 6, четвертый 7 шинные формирователи, первый элемент И 8, третий элемент H lll 9, первый регистр 10, пятый элемент 11 11, первый счетчик 12, пятый элемент ИЛИ ГЗ, первый 14 и второй 15 элементы 1И первый элемент 16 сравнения, первь-п элемент Ш1И 17, первый триггер 18, седьмой 19, iiiPCToJi 20, 21 элементы И, пторо л счетчик 22, тре- тиГ) элемент И 2, второй элемент 2ч задержки, г енератор 25 тактовых импульсов, пгрвьц элемент 26 задержки, BTopoi i триггер 27, четвертый элемент И 28, второй 29 и четвертый )0 элементы ИЛИ, 1П1П-1НЫЙ формирователь 31, трети элемент 32 плдсржгл, пятый шинный формирователь 33, ком- бинационш. сумматор 34, BTopijti ре- 1-истр J5, второй элемент 36 сравнения, третиГ счетчик 37, шестой элемент PL UI 8, аналого-цифровой преобразователь (AlUi) 39, цифроапало овый преобразователь 40, блок 41 В15емен- ного управле ия, блок 42 памяти (ЬН) цифровую вычиспительную маи;ину (ЦВМ) 43, аналс.1гоную вычислительную машинл (ЛВМ) 44, и:ину о адреса (ЦВМ), шину 46 данных ЦВМ, шину 47 записи ЦВМ iiiiiiiy 48 чтения ЦВМ, miniy 49 npepi, ния ЦВМ, шину Г.О адреса БЦ, шину 51 данных , |пину 52 записи ьИ, шину 53 чтения 1)11.

Блок 41 upe-.ieHHOi o управления содержит первы 14 и второй 55 элементы И, три1 |-ер 5h, первый j7 и BTopoji ЗН Ь ЛИ ЧИ, I jivniiy ключей 59, ре1 истр

Ь

60, дешифратор 61, первый 62 и второй 63 компараторы, элемент 6А сравнения, первый 65 и второй 66 элементы НЕ, первьш 67 и второй 68 элементы ПНИ, счетчик 69, первый 70 и второй 71 интеграторы, первый 72 и второй 73 сумматоры.

Цервый интегратор 70 содержит ключ 74, потенциометр 75, операционный усилит едь 76, конденсатор 77.

Второй интегратор 71 содержит ключ 78, потенциоме- р 79, операционный усилитель 80, конденсатор 81.

Первый сумматор 72 содержит оке-- рационный усилитель 82, регистр - Я и 84.

,H сумматор 73 ;ОДйрЖИ ) О112pa;j,iro;)iibiM усилитель 85, резисторы 8h и 87, гругиту резисторов 88 и группу иотенциол етр(1|| 89.

(лк)чи 57 и 58, группа ключей 59, первг:|й сумматор 72, по,к:ппчены информационными к шииг 90 единичного цотенциача устройства (опорному напря .м пч)

Ца этапе подгс Тоики 1.-хэдная за дача разделяется из из з-с г;:;,; способов па две частч, одна i. )- рых предн :311.( для решении ;;;

вычмс :ительиол

ЬМ)

другая - на цифровой вь ммпи

-e;i )( Г (ЦВМ) 43.

В (

ходнс й грамм, соотве

О; ; :огдг,, цифрован часть ис- за; ачи разбивается на К про- .чу1.гая iiaM.Md работает в |.:виц с ал1 о:-птмогч; ввод i зкзчен - переменных / (J - 1-М, М К) , расчет текуьгих значений фазовых переменных, вьщача через цифроанало- говый преобразователь расчитанных значений. Связь между переменными в решаемой задаче осуществляется по каналам аналого-цифрового преобра- зователя (АЦП) 39 и цифроаналогового преобразователя (ЦАЦ) 40, Пусть в

0

АВМ 44 передаются переменные у

.,У„ из ЦВМ 43, а из ПВМ 43 переменные Z , Z ..., z. В ЦВМ 43 вводится К программ задачи моделирования и программа обработки прерываний,под управлением которой происходит обмен информацией между ЦВМ 43 и БП 42, а также прерывание выполняюп .ейся и вы- g зов очередной программы вычисления фазовых переменных у (j-1-М).Ячейки БП 2 с 1 по К-ю отводятся для хранения результатов цреобразования с 1 по К-й канал АЦП 39, следующих, начиная с (К+1)-й по (К+М)-ю отводятся для хранения данных, предназначенных для выдачи с 1-го по М-й канал ЦАП 40, Таким образом, в регистр 10 необходимо занести конечный адрес К каналов АЦП 39, который одновременно является конечным адресом обмена между АЦП 39 и БП 42, а в регистр 35 заносится конечный адрес М каналов ЦАП 40. В регистр 60 заносится в двоичном коде число вычисляемых фазовых переменных, на К потенциометрах 89 блока 41 временного управления выставляются коэффициенты передачи, обеспечивающие время интегриL „ , где L - время.

I. а

рования - j равное наибольшему общему делителю

периодов изменения фазовых переменных. На потенциометре 75 выставляется коэффициент передачи, обеспечивающий время интегрирования L.

Величины 7р- L

определяют длительность времени, отведенного каждой из К программ для рещения в ЦВМ 43.Коэффициенты передачи можно выставлять по абсолютной величине от О до со ,

ограничивались

в то время как в известном устройстве зо мости обмена информации между БП 42

L величины L и - J

разрядностью регистров. Каждой из К программ вычисления Фазовой переменной для решения в ЦВМ 43 отводится

„ L время, определяемое величиной тгг-- Исключением является первая задача, часть времени обработки которой занимает время обмена переменными у.,

35

и Z

Z между ЦВМ

40

43 и БП 42.

Триггер 56 обнулен, обнулен также счетчик 69, в связи с чем на нулевом выходе дешифратора 61 находится сигнал 1, и соответствующий ключ 59 открыт. Опорное напряжение с шины 90 опорного напряжения поступает на выходы операционных усилителей 82 и 85, ла выходе компараторов 62 и 63 сигнал 1, ключи 74 и 78 открыты.

По единичному сигналу, поступающему с входа Пуск устройства, запускается на работу АВМ 44 и через элемент 26 задержки АЦП 39. Единичный сигнал с входа Пуск, поступая на единичный вход триггера 27 и нулевой вход триггера 18, устанавливает эти триггеры в состояния 1 и О соот45

50

55

и ЦВМ 43, нупевой сигнал с первого выхода дешифратора 3, поступая на вход элемента НЕ 14, вызовет поступление единичного сигнала с его выхода на третий вход элемента И 23 и второй вход элемента И 20, единичньй сигнал с выхода которого поступает на второй вход элемента И 11 и второй вход элемента ИЛИ 9, единичный сигнал с выхода которого поступает на шину 52 Запись БП 42. С приходом разрешающего сигнала с выхода ге нератора 25 на первьш вход элемента И 11 единичный сигнал с его выхода поступает на управляющие входы шинны формирователей 5 и 6. Таким образом, организуется запись информации, поступающей с выхода шинного формирователя 6 на шину 51 данных по адресу, поступающему с выхода шинного формирователя 5 на адресную шину 50 БП42 Единичный сигнал с выхода элемента 2 задержки поступает на второй вход элемента И 23 и с приходом на первый вход разрешающего сигнала с выхода генератора 25 единичный сигнал с выхода элемента И 23 поступает на счетный вход счетчика 22, увеличивая его содержимое на единицу. После при

ветственно. Единичный сигнал с входа Пуск устройства поступает на первый вход элемента ИЛИ 17, вызывая поступление единичного сигнала с его выхода на установочный вход счетчика 22, на выходе которого устанавливается адрес аналого-цифрового преобразования. В АЦП 39 происходит опрос и преобразование непрерывных сигналов, соответствующих переменным z

а

5

0

5

.,., z, поступающих с выхода АВМ 44 на информационный вход АЦП 39, начиная с начального адреса (находится в счетчике 22) и по конечный адрес (находится в регистре 10). АЦП 39 преобразует аналоговый сигнал в дискретную форму (двоичный код) и с информационного выхода подает его на информационный вход шинного формирователя 6, вырабатывая при этом единичный сигнал на выходе Конец преобразования, который поступает на вход элемента 24 задержки и первый вход элемента И 20, текущий адрес аналогово-цифрового преобразования с выхода счетчика 22 поступает на информационный вход шинного формирователя 5. Если при этом нет необходи5

0

5

0

5

и ЦВМ 43, нупевой сигнал с первого выхода дешифратора 3, поступая на вход элемента НЕ 14, вызовет поступление единичного сигнала с его выхода на третий вход элемента И 23 и второй вход элемента И 20, единичньй сигнал с выхода которого поступает на второй вход элемента И 11 и второй вход элемента ИЛИ 9, единичный сигнал с выхода которого поступает на шину 52 Запись БП 42. С приходом разрешающего сигнала с выхода генератора 25 на первьш вход элемента И 11 единичный сигнал с его выхода поступает на управляющие входы шинных формирователей 5 и 6. Таким образом, организуется запись информации, поступающей с выхода шинного формирователя 6 на шину 51 данных по адресу, поступающему с выхода шинного формирователя 5 на адресную шину 50 БП42. Единичный сигнал с выхода элемента 24 задержки поступает на второй вход элемента И 23 и с приходом на первый вход разрешающего сигнала с выхода генератора 25 единичный сигнал с выхода элемента И 23 поступает на счетный вход счетчика 22, увеличивая его содержимое на единицу. После приема нового адреса АЦП 39 переходит к преобразованию сигналов, поступающих из АВМ 44. При этом на информационном выходе и выходе Конец пре- образов-ания вырабатываются сигналы нулевого уровня. Таким образом, обеспечивается цикличность работы ЛЦП 39 Наращивание счетчика 22 будет происходить до тех пор, пока его содержи- мое станет равным содержимому регистра 10. В этом случае элемент 16 сравнения вырабатывает сигнал, который поступает на единичный вход тригтера 18 и второй вход элемента РИИ 17, с выхода которого единичны сигнал поступает на установочный вход счетчика 22, устанавливая его в начальное состояние. Единичный сигнал на единичном входе триггера 18 взводит ег о в состояние 1, и единичный сигнал с его выхода поступает на первый вход элемента И 19, на второй вход которого поступает единичный сигнал с выхода триггера 27. Единичный сигнал с выхода элемента И 19 поступает на второй вход элемента ИЛИ 13, первый вход элемента ИПИ 38 и первые входы элементов ИЛИ 29 и 67. С выходов элементов ИЛИ 13 и 38 единичный сигнал поступает на установочные входы счетчиков 12 и 37, устанавливая их в начальное состояние. Единичный сигнал с выхода элемента ИЛИ 29 подается на шину 49 Прерывание ЦВМ 43, при этом ЦВМ 43 передает управление программе прерываний обработки, которая запускает на выполнение программу вычисления первой фазовой переменной. Единичный сигнал с выхода триггера 18 поступает на н левой вход триггера 27, сбрасывая его в состо

яние О . Кроме того, сигнал с выхода триггера 18 поступает на первые входы элементов И 54 и 55. Нулевой сигнал с выхода триггера 27, поступая на второй вход элемента И 19, устанавливает на его выходе с 11 иал нулевого уровня. Единичный сигнал, поступая на первый вход э:1емента ИЛИ 67, проходит на счетный пход счетчика 69 и вход установки в единицу триггера 56. Код единицы поступает со счетчика 69 на первый вход элемента 64 сравнения и на вход дешифратора 61. На первом выходе из гругпты выходов дешифратора появляется сигнал 1 , а на нулевом выходе из группы выходов - сигнал О. (Соответствующий

ключ 59 закрывается, -а первый из остальных К ключей 59 открывается, и опорное напряжение через цепь: первый из К-х ключей 59, потенциометров 89 и резисторов 88, поступает на вход операционного усилителя 85, работающего в режиме суммирования. По единичному сигналу с выхода триггера 18 поступающему на первые входы элементов И 54 и 55, сигнал 1 поступает на управляющие входы ключей 54 и 58 и открывает их. Опорное напряжение через потенциометры 75 и 79 поступает на вход операционных усилителей 76 и 80, работающих в режиме интегрирования. Напряжение на выходах интеграторов 70 и 71 начинает увеличиваться, и когда напряжение на интеграторе 71 станет равным напряжению на сумматоре 87,сработает компаратор 63. При этом на его выходе появится сигнал О. Ключ 78 разомкнется и разрядит конденсатор 81, что приведет к появлению на выходе интегратора 71 сигнала О. На выходе компаратора 63 появится сигнал 1. Сигнал О через элемент НЕ 66 поступит на второй вход элемента ИЛИ 68, с выхода которого сигнал 1 посту

пит на второй вход элемента ИЛИ 67 и второй вход элемента ИЛИ 29, с выхода которого единичный сигнал поступит на шину 49 Прерывание ЦВМ 43.При этом ЦВМ 43 передает управление программе прерывания, которая запустит на выполнение программу вычисления второй фазовой переменной. Единичный сигнал с выхода элемента ИЛИ 67 поступит на

счетный вход счетчика 69 и на его выходе по лзится код, увеличенный на единицу. На вход сумматора 87 теперь подается опорное напряжение, на которое поступает через цепь: второй

из К-х ключей 59, потенциометров 89 и езисторов 88. Процесс выработки сигналов прерывания, длительность Mfжду которыми определяется коэффи- L

ииентами передачи ь

выставленными на потенциометрах 89, и L, вые-, тавленными на потенциометре 75, повторится, однако интегратор 71 будет интегрировать каждый раз до такого по величине напряжения, которое подается в данный момент на вход сумматора 87 через следуюиа1й из К-х ключей 59, потенциометров 89 и резисторов 88. Когда будет выбран ключ, номер

1

которого совпадает с номером, набранным на входе регистра 68, и двоичный код которого поступает на второй вход элемента 64 сравнения, на выходе его появится единичный сигнал, который установит в О счетчик 69 и триггер 56. Дешифратор 61 по своему нулевом выходу опять включит соответствующий ключ 59, а триггер 56, закроет эле- мент И 55. Интегратор 71 переведется в исходное положение. Одновременно с этим напряжение на выходе интегратора 70 будет продолжать увеличиваться, пока не сравняется с на- пряжением на выходе сумматора 84. В этот момент сработает компаратор 62, на его выходе появится сигнал О, который разомкнет ключ 74 и через элемент И 54 ключ 57. Конденсатор 77 разрядится, что приведет к появлению на выходе интегратора 70 сигнала О, На выходе компаратора 62 появится сигнал 1. Импульс логического О поступает на вход элемента НЕ 65 с выхода которого сигнал 1 через элементы ИЛИ 68 и 67 поступит на счетный вход счетчика 69. Процесс повторится сначала.

Диаграммы напряжений, поясняющие работу блока временного управления, представлены на фиг. 3.

С выхода элемента ИЛИ 68 единичные сигналы поступают на второй вход элемента ИЛИ 29, вызывая тем самым программы вычисления фазовых переменных. После выполнения программы вычисления К-й фазовой переменной программа обработки прерываний запустит на выполнение фоновые задачи, выполнение которых будет продолжаться до завершения времени цикла L. После завершения цикла программа обработки прерываний снова запустит на выполнение первую программу. Каждый раз при запуске первой программы производится обмен информацией между ЦВМ 43 и БП 42. При этом на адресной шине 45 ЦВМ 43 появляется первый адрес €П 42, по которому на первом выходе депшфратора 3 вырабатывается единичный сигнал, поступающий на управляющий вход шинного формирователя 7, разрешая поступление начального адреса обмена с выхода счетчика 12 на шину 50 адреса БП 42. Единичный сигнал с первого выхода дешифратора 3 поступает на второй вход элемента И 2, на первый вход которого

0 5

о

5

5

«

поступает си1-нал с шины 48 Чтение ЦВМ 43. Единичный сигнал с выхода элемента И 2 поступает на первый вход элемента ИЛИ 30, с выхода которого на шину 53 Чтение БП 42 поступает единичный сигнал. Считанная из БП 42 информация с шины 51 данных поступает на первый информационный вход шинного формирователя 1 (на управляющий вход которого поступает единичный сигнал с выхода элемента И 2) и с выхода шинного формирователя 1 поступает на шину 46 данных ЦВМ 43. При обработке поступившей информации ЦВМ 43 снимает с адресной шины 45 адрес БП 42 и на первом выходе дешифратора 3 появляется сигнал нулевого уровня, поступающий на вход элемента НЕ 14, с выхода которого единичный сигнал поступает на счетный вход счетчика 12, наращивая его содержимое на единицу. При появлении на адресной шине 45 ЦВМ 43 первого адреса БП 42 цикл чтения повторяется. После чтения К-й ячейки БП 42 на шине 47 Запись ЦВМ 43 появляется единичный сигнал и ЦВМ 43 переходит к записи результатов решения задачи, причем на каждом цикле записи в БП 42 вводятся все переменные до последней прочитанной. Это означает, что если к L-му циклу записи просчитаны у , у , - , у , то в БП

42будут записаны, начиная с адреса К+1, переменные у, , у, у , у , У Vg , У , из них у , у , у имеют старые значения (в первом цикле записи все переменные равны начальным условиям). Единичный сигнал с шины 47 Запись ЦВМ 43 поступает на первый вход элемента И 8, на второй вход которого поступает единичный сигнал

с первого выхода дешифратора 3. Еди- ничньш сигнал с выхода элемента И 8 поступает на управляющий вход шинного формирователя 4, разрешая прохождение информации с шины 46 данных ЦВМ 43 на шину 51 данных БП 42 и на второй вход элемента ИЛИ 9, с выхода которого единичный сигнал поступает на шину 52 Запись БП 42. Информация на шине 51 данных записывается в БП 42 по адресу, выставленному на адресной шине 50. После записи по- сдедней просчитанной переменной ЦВМ

43выставляет на адресную шину 45 второй адрес БП 42, по которому на втором вьгходе дешифратора 3 выраба,

тывается единичный сиг-нал, поступление которого на первый вход элемента ИЛИ 13 вызовет появление единич- ног о сигнечла на установочном входе счетчика 12, устанавливая его в начальное состояние. После завершения обмена ЦВМ 43 переходит к оирпботке первой программы, в это время с КП 42 может работать АЦП 39. Ь .сли ЛЦП 39 не готов к обмену, с БП 42 может работать ЦАП 40, в этом случае с хода Конец преобра: ования АЦП 39 сигнал нулевого уровня поступает на первый вход Н 20, нулевой сигнал с его выхода поступает на вхо, элемента НЕ 15, единичный сигнал с выхода которого поступает на второй вход элемента И 21, на Г1е1эвый вход, поступает единичный сигна. г с выхода элемента НЕ 14 и с приходом на третий вход разрешающего сигнала с выхо да элемента И 28 единичный сигнал с выхода элемента П 21 поступает на уи равляющие входы шинных формирователей 31 и 33, второй вход элемента 1ШП 30, вход элемента 32 задержки и одновременно единичный сигнал с выхода элемента 21 запускает иА работу ЦАП 40. Начальный адрес цифроа}1алогО вого преобразователя с В1)1хода счетчика 37 поступает на второй вход сумматора 34, на первый вход которого поступает конечный адрес аналого- цифрово1 о преобразования. С выхода сумматора 34 начальнр и адрес обмена поступает на информационный вход шинного формирователя 33 и с приходом единичного сигнала tia его управляющий вход адрес поступает на адресную шину 50 ВП 42. С иькода элемента ИЛИ 30 единичный сиг-нал поступает на шину 53 Чтение 1И1 42.

Информация с шины 51 дачных поступает на информаци(-1нный вход шинного формирователя 31 и с приходом на его управляющий вход единичного сигнала с выхода элемента И 21 данные БП 42 поступают на информационный вход ПАП 40, на адресный вход KOTopoi o noci-y- пает адрес цифроаналогового преобразователя с выхода счетчика 37. Единичный сигнал с ныхода элемента 32 задержки, поступая на счстньл 1 вход счетчика 37, увеличивает его содержимое на единицу. С приходом С Д1-п1ич- ного сигнала с Bi.ixo/ra элемергга И 21 повторится 1Ц1КЛ 1 И|}- роаналогоного пре- образова})ия. Koi ;;a с-пдержимое счет 348844 О

чика 37 будет равно содержимому ре- -истра 35, единичный сигнал с выхода элемента 36 сравнения поступит на с- второй вход элемента ИЛИ 38. Единичный с выхода элемента ИЛИ 38 поступит на установочный вход счетчика 37 и установит его в начальное состояние.

10

0

5

5

0

5

Формула изобретения

Устройство для обмена информацией между цифровой и аналоговой вычисли- тельн(1ми машинами, содержащее блок памяти, цифроаналоговый преобразователь, аналого-цифровой преобразова- телт), комбинационный сумматор, генератор тактовых импульсов, дешифратор, семь шинных формирователей, три счётчика, два триггера, два регистра, два элемента сравнения, три элемента задержки, восемь элементов И, шесть элементов ИЛИ, два элемента НЕ, причем информационные входы первого и второго регистров являются первыми и вторыми входами задания конечного адреса устройства соответственно, вход первого элемента задержки сое- лчинен с первым входом первого элемента ИЛИ, с нулевым входом первого триггера, с единичным входом второго триггера и является входом устройства для подключения к входу запуска аналоговой вычислительной машины, информацион)ый выход первого шинного Формирователя и информационный вход второго шинного формирователя являются входом и выходом устройства для подключения к информационной шине цифровой вычислительной машины, информационный вход дешифратора яв. шется входом устройства для подключения к адресной шине цифровой вычислительной машины, первые входы первого и второго элементов И являются входами устройства для подключения к шине записи и шине чтения цифровой вычислительной машины соответственно у выход второго элемента ИЛИ является выходом устройства для подключения к шине прерывания цифровой вычислительной машины, информационный вход аналого-цифрового преобразователя и информационный выход Ц1 фроаналогового преобразователя являются входом и выходом устройства для подключения к информационным выходу и входу анало1-овой вычислительной машины соответственно, при этом информационные выходы третьего, четвертого и пятого шинных формирователей соединены с адресным входом блока памяти, информационный вход- выход которого соединен с информационными входами первого, шестого шинных формирователей и информационными выходами второго, седьмого шинных формирователей, первый выход дешифратора соединен с вторым входом второго элемента И, управляющим входом четвертого шинного формирователя, входом первого элемента НЕ и вторым входом первого элемента И, выход которого соединен с управляющим входом второго шинного формирователя и с первым входом третьего элемента ИЛИ, выход которого соединен с входом за- писи блока памяти, вход чтения которого соединен с выходом четвертого элемента ИЛИ, первый вход которого соединен с управляющим входом первого пшнного формирователя и с выходом второго элемента И, второй выход дешифратора соединен с первым входом пятого элемента ИЛИ, выход которого соединен с установочным входом первого счетчика, выход которого соединен с информационным входом четвертого шинного формирователя, выход генератора тактовых импульсов соединен с первыми входами третьего, четвертого и пятого элементов И, выход третьего элемента И соединен с адресным входом аналого-цифрового преобразователя, с первым входом первого элемента сравнения и с информационным входом третьего шинного формирователя, управляю- щий вход которого соединен с выходом пятого элемента И и с управляющим входом седьмого шинного формирователя, информационный вход которого соединен с информационным выходом анало го-цифрового преобразователя, вход запуска которого соединен с выходом первого элемента задержки, выход Конец преобразования аналого-цифрового преобразователя соединен с первым входом шестого элемента И и с входом второго элемента задержки, выход которого соединен с вторым входом третьего элемента И, выход которого соединен со счетным входом второго счетчика, установочный вход которо- ,го соединен с выходом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента

0 5 о Q

5

сравнения и с единичным входом г,ер- вого триггера, выход которого соединен с первым входом седьмого элемента И, с вторым входом четвертого элемента И и с нулевым входом второго триггера, выход которого соединен с вторым входом седьмого элемента И, выход которого соединен с вторым входом пятого элемента ИЛИ, с первым входом второго элемента ИЛИ и с первым входом шестого элемента ИЛИ, выход которого соединен с установочным входом третьего счетчика, счетный вход которого соединен с выходом третьего элемента задержки, вход которого соединен с вторым входом четвертого элемента ИЛИ, с выходом восьмого элемента И, входом запуска циф- роаналогового преобразователя, управляющим входом шестого шинного формирователя, управляющим входом пятого шинного формирователя, информационный вход которого соединен с выходом комбинационного сумматора, первый вход которого соединен с вторым входом первого элемента сравнения и с выхо- дом первого регистра, выход первого элемента НЕ соединен со счетным входом первого счетчика, третьим входом третье1 о элемента И, первым входом восьмого элемента И и с вторым входом шестого элемента И, выход которого соединен с вторым входом пятого элемента И, вторым входом третьего элемента ИЛИ и с входом второго элемента НЕ, выход которого соединен с вторым входом восьмого элемента И, третий вход которого соединен с выходом четвертого элемента И, выход шестого шинного формирователя соединен с информационным входом цифро- аналогового преобразователя, адресный вход которого соединен с вторым входом комбинационного сумматора, с выходом третьего счетчика и с первым входом второго элемента сравнения, второй вход и выход KOToisoro соединены соответственно с выходом второго рех истра и с вторым входом шестого элемента ИЛИ, отличающее- с я тем, что, с целью повьшения точности вычислений за счет расширения диапазона задания временных сигналов и обеспечения непрерывного изменения времен запуска программ цифровой части в процессе решения, в него введен блок временно1 о управления, причем информационный вход регистра блпка

временного управления является входом задания числа вычисляемых фазовых переменных устройства, при этом выход пер; ого триггера соединен с разрешающим входом блока временного управления, выход седьмого элемента И соединен с о счетным входом блока временного управления, выход блока временного у;|;-атшения соединен с вторым входом сгиго элемента ИЛИ, причем блок вр .М U1 1ГО управления содержит два интегратора, два сумматора, два компаратора, регистр, элемент сравнения, At.iiitibpaTop, счетчик, два элемента Ii4H, ,г,л элемента И, два элемента НЕ, ;р, два ключа, группу ключей, ;Ф1 .тлм первый вход первого элемента И соединен с первым входом второго элемента И и является разрешающим пуJ;TOM блока временнох о управления, ,ir-jMbJi вход первого элемента ИЛИ является счетным входом блока временного управления, выход второго млемоита ИЛИ соединен с вторым вхо- пом первого элемента ИЛИ и является ;;м;1одом блока временного управления, lipii этом в блоке временного управления выходы первого интегратор а и пер- ( ii o сумматора соединены соответст- Г лчт о с первым и вторым входами пер- Богй компаратора, выход которого соединен с вторым входом первого элемента И, с управляющим входом первого интегратора и с входом первого элемента НЕ, выход которого соединен с первым входом второго элемента ИЛИ,

второй вход которого- с выходом второго элемента НЕ, вход которого соединен с вторым входом вто- рого элемента И, управляющим входом второго интегратора и с вых.одом второго компаратора, первый и второй входы которого соединены соответственно с выходами второго интегратора и второго сумматора, выходы первого и второго элементов И соединены соответственно с управляющими входами первого и второго ключей, управляющие входы ключей группы соединены

с группой выходов дешифратора, информационный вход которого соединен с первым входом элемента сравнения и с выходом счетчика, счетный вход которого соединен с выходом первого элчмента ИЛИ и с единичным входом триг- гер.а, нулевой вход которого соединен с установочным входом счетчика и с выходом элемента сравнения, второй вход которого соединен с выходом ре1 истра, выход триггера соединен с третьим входом второго элемента И, выходы первого и второго ключей соединены с информационными входами соответственно первого и второго интеграторов, выходы ключей групп соединены с группой информационных входов второго сумматора, информационные входы первого, второго ключей, к/почей группы и первого

сумматора подключены к шине единичного потенциала устройства ,

Г7П

,UycK

nf

.ie

Sbix.SZ

USbix.$5

и вых. 80

Состапитель С . Ilec i мил Редакто Е.Копча Техре,ч А.К1;авчукКч ректор А.Обручар

Закат 4803/49Titna; ь7()i.j,, ык :ui;ВНИЛПИ ; -ч }. )( НПО о коплтет-ч CCX i по де. ; i. :; с ми 11 i i l.l M i м

1 13033, . , . :- : , .. :.,ч-- с М 11.10. , д. t/ )

Up ,;зводствеи11о--11

ч с

2L

2L

2L

Фиг.2

iii и,; . ; I ;, i . Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1221666A1 |

| Устройство для передачи телеметрической информации | 1986 |

|

SU1336077A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сопряжения цифровой вычислительной машины | 1987 |

|

SU1444793A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании аналого-цифровых устройств и систем для моделирования динамических объектов и систем управления в реальном масштабе времени. Целью изобретения является повышение точности вычислений за счет расширения диапазона задания временных сигналов и обеспечения непрерывного изменения времен запуска программ цифровой части в процессе решения. Устройство содерлсит блок временного управления, цифроаналоговый преобразователь, аналого-цифровой преобразователь, комбинационный сумматор, генератор тактовых импульсов, дешифратор, два триггера, два регистра, два элемента сравнения, два элемента НЕ, три счетчика, три элемента задержки, шесть элементов ИЛИ, семь элементов И, семь шинных формирователей. 3 ил. (Л со 00 00 4 4

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1982 |

|

SU1053119A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1221666A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1986-06-30—Подача