Изобретение относится к вычислительной технике и может быть использовано при создании аналого-цифровых устройств и систем для моделирования диттамических объектов и систем управления в реальном масштабе времени Цель изобретения - повышение производительности.

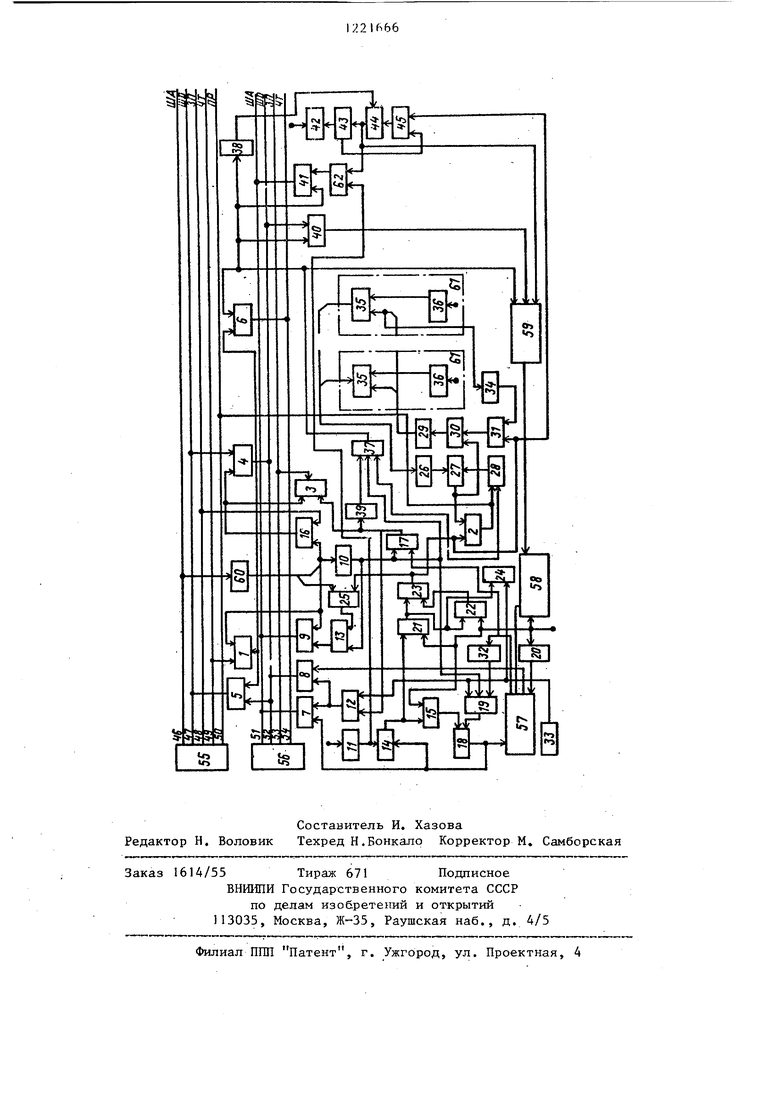

На чертеже представлена блок-схем устройства.

Устройство содержит восьмой элемент И 1, третий элемент ИЛИ 2, четвертьм элемент ИЛИ 3, пятый шинный формирователь 4, шестой шинный формирователь 5, шестой элемент . ИЛИ 6, второй шинный формирователь 7, первый шинный формирователь 8, седьмой шинный формирователь 9, первый элемент НЕ 10, первый регистр II, второй элемент И 12, пятый счетчик 13, первую схему 14 сравнения, первый элемент ИЛИ 15, седьмой элемент И 16, шестой элемент И 17, первый счетчик 18, первый элемент И 19, второй элемент 20 задержки, первый триггер 21, второй триггер 22, пятый элемент И 23, четвертьш элемент И 24, пятьм элемент ИЛИ 25, третий регистр 26, третью схему 27 сравнения, третий счетчик 28, второй дешифратор 29, четвертый счетчик 30, седьмой элемент ИЛИ 31, третий элемент 32 задержки, генератор 33 тактовых импульсов, четвертый элемент 3 задержки, шинные формирователи 35, регистры 36, третий элемент И 37, первый элемент 38 задержки, второй элемент НЕ 39, третий шинный формирователь 40, четвертый шинный формирователь 41, второй регистр 42, вторую схему 43 сравнения, второй счетчик 44, второй элемент ИЛИ 45, шины адреса 46, данных 47, Запись 48, Чтение 49, Прерьшание 50 цифровой вычислительной машины, шины адреса 51, данных 52, Запись 53, Чтение 54 блока памяти, цифровая вычислительная.машина (ЦВМ) 55, блок 56 памяти, аналого-цифровой преобразователь (АЦП) 57, аналоговая вычислительная машина (АВМ) 58, циф- роаналоговый преобразователь (ЦАП) 59, первый дешифратор 60, группу узлов 61 задания времени, комбинационный сумматор 62.

На этапе подготовки исходная задача разделяется одним из известных способов на две, одна из которых

5

0

5

предназначена для решения на аналоговой (АВМ 58), а другая - на цифровой части устройства (ЦВМ 55). В свою очередь, цифровая часть исходной задачи разбивается на К программ.

Связь между переменными осуществляется по каналам АЦП 57 и ЦАП 59. В ЦВМ 55 вводится К программ задачи моделлрования и программа обработки прерываний, под управлением которой происходит обмен информацией между ЦВМ 55 и блоком 56 памяти, а также прерывание выполняющейся и вызов очередной программы вычисления фазовых переменных. Ячейки блока 56 с 1 по К -ю отводятся для хранения результатов преобразования с 1 по К-и канала АЦП 57, следующие, начиная с К + 1 по к +М -ю, отводятся для хранения данных, предназначенных для выдачи с 1 по М-ый канал ЦАП 59. Таким образом, в регистр 11 необходимо занести конечный адрес К каналов АЦП 57, который одновременно является конечным адресом обмена между АЦП 57 и блоком 56, а в регистр 42 заносится конечный адрес М кана- лов ЦАП 59. В блоки 61 на каждый из К регистров 36 заносится двоичный код числа разрешающих сигналов генератора 33 импульсов, длительность которых равна промежутку времени, отведенному каждой из К программ для решения в ЦВМ 55. Исключением является первая задача, часть времени обработки которой занимает время обмена переменными между ЦВМ 55 и блоком 56. По единичному сигналу, поступающему с входа Пуск устройства, запускается в работу АВМ 58 через элемент 20 задержки АЦП 57. Единичный сигнал с входа Пуск, поступая на единичный вход триггера 22 и нулевой вход триггера 21, устанавливает эти триггеры в состояние логической 1 и логического О соответственно. Единичньй сигнал с входа. Пуск устройства поступает на второй вход элемента ИЛИ 15, вы- зьшая поступление единичного сигнала с его выхода на установочный вход счетчика 18, на выходе которого устанавливается начальньй адрес аналого-цифрового преобразования. В АЦП 5 57 происходит опрос и преобразование непрерывных сигналов, соответствующих переменным, поступающим с выхода АВМ 58 на информационный вход АЦП 57,

0

5

0

5

0

начиная с начального адреса(находится в счетчике 18) и по конечный адрес (находится в регистре П), АЦП 57 преобразует аналоговый сигнал в дискретную форму (двоичный код) и с информационного выхода подает его на информационный вход формирователя 8, вырабатывая при этом единичный сигнал на.выходе Конец преобразования, который поступает на вход элемента 32 задержки и первый вход элемента И 17, текущий адрес аналого-цифрового преобразователя с выхода счетчика 18 поступает на информационный вход шин

ного формирователя 7, Если при этом нет необходимости обмена информацией между блоком 56 и ЦВМ 55, нулевой сигнал с первого выхода дешифратора 60, поступая на вход элемента НЕ 10, вызьшает поступление единичного сигнала с его выхода на второй вход элемента И 19 и второй вход элемента И 17, единичный сигнал с выхода которого поступает на второй вход элемента И 12 и первый вход элемента ИЛИ 3, единичный сигнал с выхода которого поступает на шину 53 Запис блока 56. С приходом разрешающего сигнала с выхода генератора 33 на первый вход элемента И 12 единичный сигнал с его выхода поступает на управляющие входы шинных формирователей 7 и 8. Таким образом, организуется запись информации, поступающе с выхода шинного формирователя 8 на шину 52 данных по адресу, поступающему с выхода шинного формирователя 7 на адресную шину 51 блока 56. Единичный сигнал: с выхода элемента 32 задержки поступает на третий вход элемента И 19, и с приходом на первый вход разрешающего сигнала с выхода генератора 33 единичный сигнал с выхода элемента И 19 поступает на счетный вход счетчика 18, увеличивая его содержимое на единицу. После . . приема нового адреса АЦП 57 перехо- дит к преобразователю сигналов, поступающих из АВМ 58, при этом на информационном выходе и выходе Конец преобразования вырабатываются сигналы нулевого уровня. Таким образом, обеспечивается цикличность работы АЦП 57. Наращивание счетчика 18 происходит до тех пор, пока его содержи мое не станет равным содержимому регистра П. В этом случае схема 14 сравнения вырабатывает единичный

, 10

t5

20

25

30

35 40 4550 55

2216664

сигнал, который поступает на единичный вход триггера 21 и первый вход элемента ИЛИ 15, с выхода которого единичный сигнал поступает на установочный вход счетчика 18, устанавливая его в начальное состояние. Единичный сигнал на единичном входе триггера 21 взводит его в состояние логической 1 и единичный сигнал с его выхода поступает на первый вход элемента И 23, на второй вход которого поступает единичный сигнал с выхода триггера 22. Единичный сигнал с выхода элемента И 23 поступает на вторые входы элементов ИЛИ 25 и 45 и первые входы элементов ИЛИ 2 и 31, с выходов которых единичный сигнал поступает на установочные входы счетчиков 13, 28, 44 и 30, устанавливая их в начальное состояние. Кроме того, единичный сигнал с выхода элем1ента ИЛИ 2 подается на шину 50 Прерывание ЦВМ 55, при этом ЦВМ 55 передает управление программе обработки прерываний, которая запускает на выполнение первую программу вычисления фазовой переменной. Единичный сигнал с выхода триггера 21 поступает на нулевой вход триггера 22, сбрасывая его в состояние логического О. Нулевой сигнал с выхода триггера 22, поступая на второй вход элемента И 23, устанавливает на его выходе сигнал нулевого уровня. Двоичный код номера программы (в данном случае первой), находящийся в счетчике 30, поступает на вход дешифратора 29, с выхода которого единичный сигнал поступает на управляющий вход шинного формирователя 35, разрешая запись содержимого первого регистра 36 в регистр 26. Единичный сигнал с выхода триггера 21, поступающий на второй вход элемента И 24, разрешает прохождение тактовых импульсов, поступающих с выхода генератора 33 на первый вход элемента И 24, с выхода последнего на счетный вход счетчика 28. Наращивание счетчика 28 происходит до тех пор, пока его содержимое не станет равным содержимому регистра 26, в этом случае схема 27 сравнения вырабатывает единичный сигнал, поступление которого на второй вход элемента ИЛИ 2 вызывает поступление единичного сигнала с его выхода на вход 50 Прерывание ЦВМ 55. При

этом ЦВМ 55 передает управление программе прерывания, которая запускает на выполнение вторую программу вычисления фазовой переменной. В это же время единичный сигнал с выхода схемы 27 сравнения поступает на счетный вход счетчика 30, увеличивая его содержимое на единицу. Дешифратор 29 вырабатывает единичный сигнал, поступление которого на управляющий вход шинного формирователя 35 вызывает запись содержимого следующего регистра 36 в регистр 26. Таким образом устройство работает до тех пор, пока не будут выполнены все К программ вычисления фазовых переменных. При переходе к К -и программе единичный сигнал с выхода дешифратора 29 поступает на управляющий входк ого шинного формирователя и на вход элемента 34 задержки. Единичный сигнал с выхода элемента 34 задержки поступает на второй вход элемента 31 ИЛИ, с выхода которого единичный сигнал поступает на установочный вход счетчика 30, устанавливая его в начальное состояние. После выполнения К-и программы программа обработки прерываний снова запус- кает на вьшолнение первую программу. Каждый раз,, при запуске первой программы производится обмен информацией между ЦВМ 55 и блоком 56. При этом на адресной шине 46 появляется первый адрес блока 56, по которому на первом выходе дешифратора 60 вырабатывается единичный сигнал, поступающий на управляющий вход шинного формирователя 9, разрешая поступление начального адреса обмена с выхода счетчика 13 на шину 51 адреса. Единичньй сигнал с первого выхода дешифратора 60 поступает на первый вход элемента И 1, на второй вход которого поступает сигнал с шины Чте- ние ЦВМ 55. Единичный сигнал с выхода элемента И 1 поступает на первый вход элемента ЩШ 6, с выхода которого на шину 54 Чтение блока 56 поступает единичный сигнал. Считанная из блока 56 информация с шины 52 данных поступает на информационный вход шинного формирователя 5 (на управляющий вход которого поступает единичньй сигнал с выхода элемента И 1) и с его выхода поступает на шину 47 данных. При обработке поступившей информации ЦВМ 55

10

20

25

15 45

2216666

снимает с адресной шины 46 адрес ка 56 памяти, и на первом выходе дешифратора 60 появляется сигнал нулевого уровня, поступающий на вход элемента НЕ 10, с выхода которого единичный сигнал поступает на счетный вход счетчика 13, наращивая его содержимое на единицу. При появлении на адресной шине 46 первого адреса блока 56 цикл чтения повторяется. После чтения К -и ячейки блока 56 на шине 48 Запись появляется единичньй сигнал и ЦВМ 55 переходит к записи результатов решения задачио Причем на каждом цикле записи в блок 56 вводятся все переменные до последней просчитанной. Единичньй сигнал с шины Запись ЦВМ 55 поступает на первый вход элемента И 16, на второй выход которого по- ступает единичный сигнал с первого выхода дешифратора 60. Единичный сигнал с выхода элемента И 16 поступает на управляющий вход шинного .формирователя 4, разрешая прохождение информации с шины 47 данных на шину 52 данных и на второй вход элемента ИПИ 3, с выхода которого единичный сигнал поступает на шину, 53 Запись Информация на шине 52 данных записывается в блок 56 по адресу, выставленному на адресной шине 51, После записи последней просчитанной переменной ЦВМ 55 выставляет на адресную шину 46 второй адрес блока 56, по которому на втором выходе дешифратора 60 вырабатывается единичный сигнал, поступление которого на первый вход элемента ИЛИ 25 вызывае.т появление единичного сигнала на установочном входе счетчика 13, устанавливая его в начальное состояние. После завершения обмена ЦВМ 55 переходит к обработке первой программы и в это время с блоком 56 может работать АЦП 57. Если АЦП 57 не готово к обмену, с блоком 56 может работать ЦАП 59, в этом случае с выхода Конец преобразования АЦП 57 сигнал нулевого : уровня поступает на первьй вход элемента И 17, нулевой сигнал с его выхода поступает на вход элемента НЕ 39, единичньй сигнал с выхода которого поступает на первый вход элемента И 37, на второй вход поступает еди-. ничный сигнал с выхода элемента НЕ 10 и с приходом на третий вход раз30

35

40

50

55

решающего сигнала с выхода элемента И 24 единичный сигнал с выхода элемета И 37 поступает на второй вход элемента ИЛИ 6, управляющие входы шинных формирователей 40 и 41, на вход элемента 38 задержки и одновременно единичный сигнал с выхода элемента И 37 запускает в работу ЦАП 59 Начальньй адрес цифроаналогового преобразователя с выхода счетчика 44 поступает на второй вход сумматора 62, на первый вход которого поступает конечньй адрес аналого-цифрового преобразования. С выхода матора 62 начальный адрес обмена постзшает на информационный вход шинного формирователя 41, и с приходом единичного сигнала на его управляющий вход адрес поступает на адресную шину блока 56. С выхода элемента ИЛИ 6 единичный сигнал поступает на шину 54 Чтение. Информация с шины 52 данных поступает на информационный вход шинного формирователя 40, и с приходом на его управляющий вход единичного сигнала с выхода элемента И 37 данные блока 56 поступают на информационный вход ЦАП 59, на адресный вход которого поступает адрес цифроаналогового преобразования с выхода счетчика 44. Единичньй сигнал с выхода элемента 38 задержки, поступая на счетный вход счетчика 44, увеличивает его содержимое на единицу. С приходом единичного сигнала с выхода элемента И 37 повторяется цикл цифроаналогового преобразования. Когда содержимое счетчика 44 равно содержимому регистра 42, единичный сигнал с выхода схемы 43 сравнения поступает на первый вход элемента ИЛИ 45. Единичный сигнал с выхода элемента ИЛИ 45 поступает на установочный вход счетчика 44 и устанавливает его в начальное состояние.

Формула изобретения

Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами, содержащее блок памяти, аналого-цифровой и циф- роаналоговый преобразователи, три счетчика, два регистра, пять элемен- тов И, пять элементов ИЛИ, два элемента НЕ, два элемента задержки, два триггера, генератор тактовых им-

20

н. 35

216668

пульсов, первый дешифратор, две схемы сравнения, семь шинных формирователей, причем информационньш вход и выход аналого-цифрового преобразова5 теля соединены соответственно с информационным выходом аналоговой вычислительной машины и через первый шинный формирователь - с данных блока памяти, выход первого

10 счетчика соединен с адресным входом аналого-цифрового преобразователя, первьм входом первой схемы сравнения и через второй шинный формирователь - с адресной шиной блока памяти, вто-

15 рой вход первой схемы сравнения

соединен с. выходом первого регистра, вход которого является первым входом задания конечного адреса устройства, выход первой схемы сравнения соединен с первым входом первого элемента ИЛИ, выход которого соединен с установочным входом первого счетчика, счетный вход которого соединен с выходом первого элемента И, управляющие входы первого и второго шинных формирователей соединены с выходом второго элемента И, информационный выход цифроаналогового преобразователя соединен с информационным входом

30 аналоговой вычислительной машины, а информационный вход через третий шинный формирователь соединен с ши25

ной данных блока-памяти, адресный вход цифроаналогового преобразователя соединен с выходом второго счетчика, соединенным с первым входом второй схемы сравнения, второй вход которой соединен с выходом второго регистра, вход которого является вторым входом задания конечного адреса устройства, выход второй схемы сравнения соединен с первым входом второго элемента ИЛИ, выход которого соединен с установочным входом второго счетчика, счетный вход которого через первый элемент задержки соединен с выходом третьего элемента И, соединенньм также с управляющими входами третьего и четвертого шинных формирователей, первый и второй входы третьего элемента И . соединены соответственно с выходами первого и второго элементов НЕ, а третий вход соединен с выходом четвертого элемента И, первый вход которого соединен с выходом генератора тактовых импульсов, выход третьего элемента ИЛИ соединен с шиной прерывания цифровой вычислительной маши- ны, а первый вход - с выходом пятого элемента И, выходная и входная шины данных цифровой вычислительной машины соответственно через пятый и тестой шинные формирователи соединены с входной и выходной шинами данных блока памяти, первый вход первого элемента И соединен с выходом первого элемента НЕ, вход первого дешифратора соединен с адресной шиной цифровой вычислительной машинь, отличающееся тем, что, с целью повьппения производительности, оно содержит группу узлов за- Дания времени, комбинационный сумматор, шестой, седьмой и восьмой элементы И, шестой и седьмой элементы ИЛИ, третий и четвертый эле- менты задержки, четвертый и пятый счетчики, третью схему сравнения, второй дешифратор, третий регистр, причем выходы УЗЛОВ задания времени группы соединены с входами тре- тьего регистра, выход которого сое- динен с первым входом третьей схемы сравнения, второй вход которой соединен с выходом третьего счетчика, выход равно третьей схемы сравнения соединен с вторым входом тре- тьего элемента ИЛИ и счетным В ходом четвертого счетчика, выход которого через второй дешифратор соединен с разрешающими входами узлов задания времени группы,установочный и счетный вхр ды третьего счетчика соединены соответственно с выходом третьего элемента ИЛИ и выходом четвертого элемента И, второй вход которого соединен с выходом первого триггера, соединен ным с первыми входами второго триггера и пятого элемента И, второй вход которого соединен с выходом второго триггера, второй вход которого соединен с входом пуска устройства, вторым входом первого элемента ИЛИ, первым входом триггера, входом Пуск аналоговой вычислительной машины и через второй элемент задержки с входом Пуск аналого-цифрового преоб- разователя, выход Конец преобразователя которого через третий элемент задержки соединен с вторым входом первого элемента И, третий вХод которого и первый вход второго элемента И соединены с выходом генератора

тактовых импульсов, второй вход первого триггера соединен с выходом первой схемы сравнения, выход первого элемента НЕ соединен со счетным входом пятого счетчика, и первым входом шестого элемента И, второй вход которого Соединен с выходом Конец преобразования аналого-цифрового преобразователя, а выход соединен с входом второго элемента НЕ, вторым входом элемента И и первым входом четвертого элемента ИЛИ, выход которого соединен с шиной записи блока памяти, а второй вход - с выходом седьмого элемента И и управляющим входом пятого шинного формирователя, первый вход седьмого элемента И соединен с шиной записи цифровой вычислительной машины, второй вход седьмого элемента И, вход первого элемента НЕ, вторые входы пятого элемента ИЛИ и восьмого элемента И и управляющий вход седьмого шинного формирователя соединены с выходами первого дешифратора, второй вход восьмого элемента И соединен с шиной чтения цифровой вычислительной машины, а выход соединен с управляющим входом шестого шинного формирователя и первым входом шестого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом третьего элемента И, соединенным с входом Пуск цифроаналогового преобразователя и с шиной чтения блока памяти, вторые входы пятого и второго элементов ИЛИ и первый вход седьмого элемента ИЛИ соединены с выходо пятого элемента И, выход пятого элемента ИЛИ соединен с установочным входом пятого счетчика, выход которого через седьмой шинный формировател соединен с адресной шиной блока памяти, второй вход седьмого элемента ИЛИ через четвертый элемент задержки соединен с соответствующ1П4 выходом второго дешифратора, выход седьмого элемента ИЛИ соединен с установочным входом четвертого счетчика, первый и второй входы комбинационного сумматора соединены соответственно,с выходом первого регистра и выходом второго счетчика, а выход соединен через четвертый шинный формирователь с адресной шиной блока памяти.

if

Э

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1986 |

|

SU1348844A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1982 |

|

SU1053119A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для связи аналоговой и цифровых вычислительных машин | 1983 |

|

SU1140135A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Устройство для сопряжения абонентов с цифровой вычислительной машиной | 1985 |

|

SU1305700A1 |

Изобретение относится к области вычислительной техники и может быть использовано при создании аналого- цифровых устройств, и систем для моделирования динамических объектов и систем управления в реальном масштабе времениi Целью изобретения является повышение производительности. Устройство содержит блок памяти, регистры, счетчики, схемы сравнения, аналого-цифровой и цифроаналоговый преобразователи, триггеры, генератор тактовых импульсов, шинные формиро- . ватели. Цель достигается 3ji счет .оптимизации распределения временных интервалов, выполнения различных операций в устройстве. 1 ип. IND 1C о а о

Составитель И. Хазова Редактор Н. Воловик Техред Н.Бонкало Корректор М. Самборская

Заказ 1614/55 Тираж 671 Подписное ВНШШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

| Устройство для сопряжения аналоговой и цифровой вычислительных машин | 1979 |

|

SU858022A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1982 |

|

SU1053119A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-03-30—Публикация

1983-07-11—Подача