1

Изобретение относится к технике связи и может быть использовано в аппаратуре передачи данных при разработк-е устройств, обеспечивающих помехоустойчивый прием многократно повторяемой информации.

Известно устройство приема многократно передаваемых комбинаций, содержащее последовательно соединенные блок преобразования и блок мажоритарной вцборки, два элемента И, два регистра сдвига, первый блок памяти, элемент ИЛИ и сумматор l}.

Однако в известном устройстве недост.аточная помехозащищенность.

Цепь изобретения - повышение помехозжцищенности.

Для этого в устройство приема многократно передаваемых комбинаций, содержащее последовательно соединенные блок преобразования и блок мажоритарной выборки, два элемента И,два регистра сдвига, первый, блок памяти, элемент ИЛИ и сумматор, введены декодирующий блок, блок определения достоверности символов, последовательно соединенные делитель, второй блок памяти и блок сравнения, а также блок управления и запоминакндий

блок, причем вход блока преобразования соединен с входом декодирующего блока, первый выход которого соедие нен с одним входом элемента ИЛИ,другой вход которого сюединен через первый элемент И с вторым выходом декодирукздего блока, выходы блока преобразования соединены с входами блока

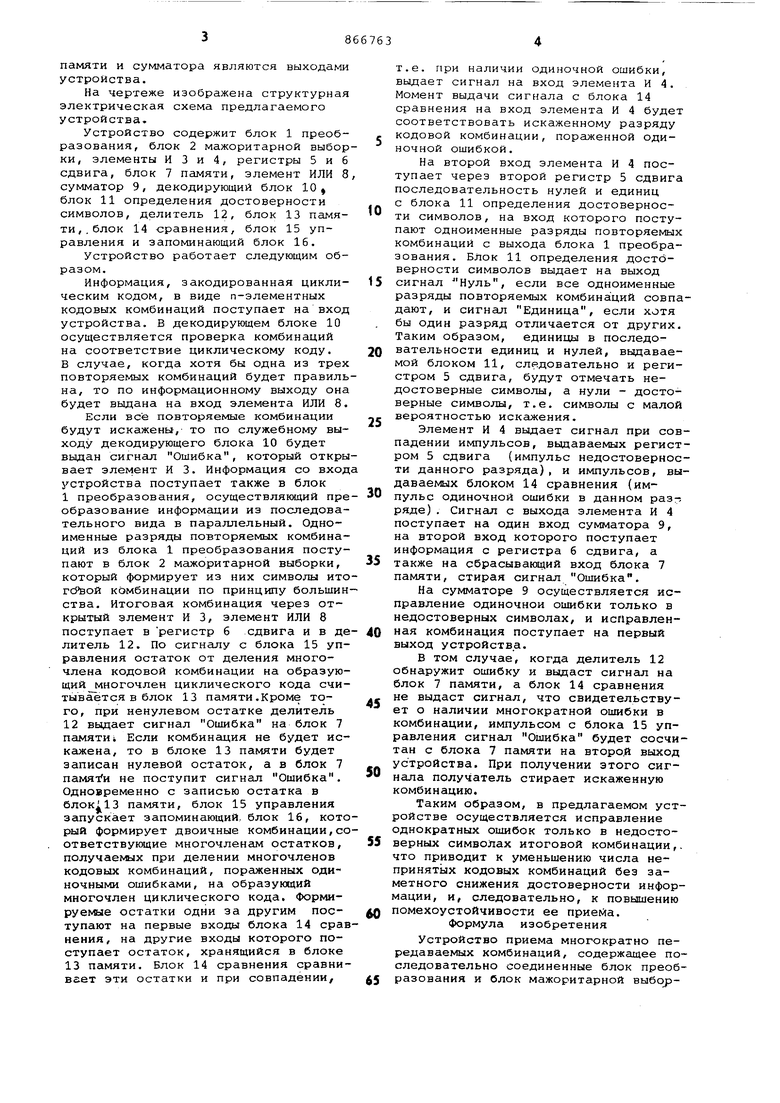

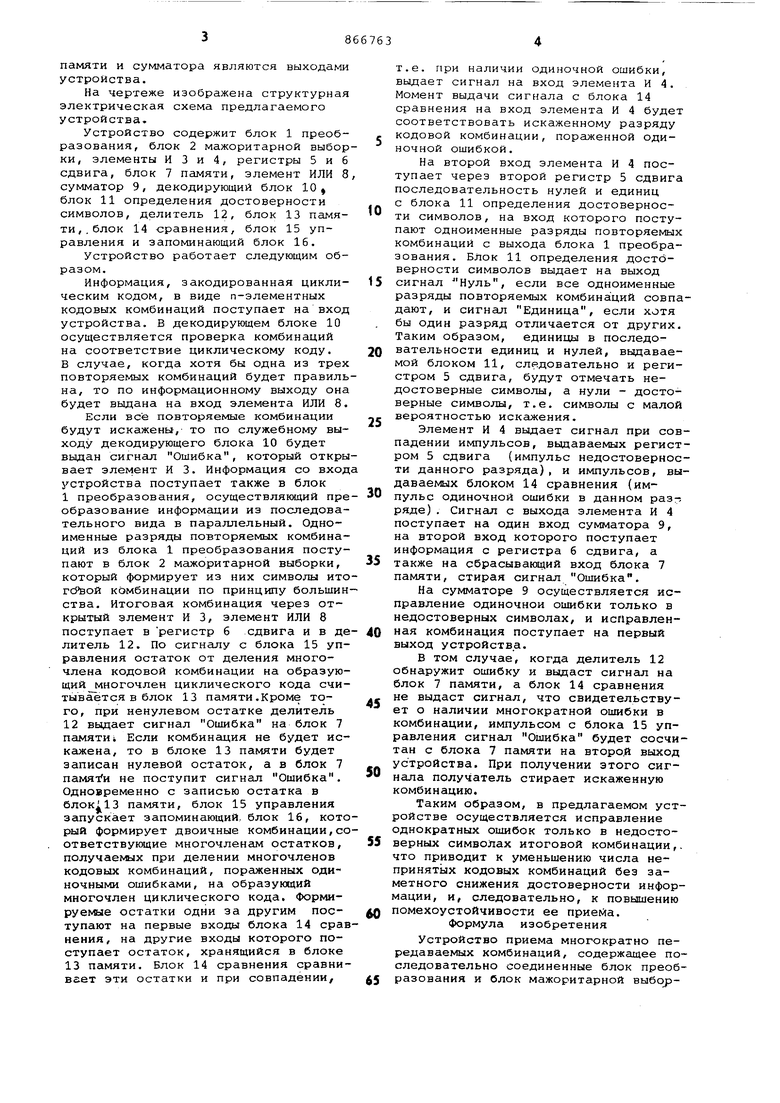

IQ определения достоверности символов, выход которого через последовательно соединенные первый регистр сдвига и второй элемент И соединен с одним входом сумматора, другой вход которого через второй регистр сдвига соединен с выходом элемента ИЛИ, соеди1 ненным с первым входом делителя,второй вход которого соединен с. одним выходом блока управления, соединенным с входом запоминающего блока, вы20ходы которого соединены с входами блока сравнения, выход которого соединен с другим входом второго элемента И, выход которого соединен с первым входом первого блока памяти, вто25рой и третий входы которого соединены соответственно с выходом делителя и другим выходом блока управления, выход блока мажоритарной выборки соединен с другим входом первого элемен30та И, при этом выходы первого блока памяти и сумматора являются выходами устройства. На чертеже изображена структурная электрическая схема предлагаемого устройства. Устройство содержит блок 1 преобразования, блок 2 мажоритарной выбор ки, элементы И 3 и 4, регистры 5 и 6 сдвига, блок 7 памяти, элемент ИЛИ 8 сумматор 9, декодирующий блок 10 блок 11 определения достоверности символов, делитель 12, блок 13 памяти,.блок 14 сравнения, блок 15 управления и запоминающий блок 16. Устройство работает следующим образом. Информация, закодированная циклическим кодом, в виде п-элементных кодовых комбинаций поступает на вход устройства. В декодирующем блоке 10 осуществляется проверка комбинаций на соответствие циклическому коду. В случае, когда хотя бы одна из трех повторяемых комбинаций будет правиль на, то по информационному выходу она будет выдана на вход элемента ИЛИ 8. Если все повторяемые комбинации будут искажены, то по служебному выходу декодирующего блока 10 будет выдан сигнал Ощибка, который откры вает элемент И 3. Информация со вход устройства поступает также в блок 1 преобразования, осуществляющий пре образование информации из последовательного вида в параллельный. Одноименные разряды повторяемых комбинаций из блока 1 преобразования поступают в блок 2 мажоритарной выборки, который формирует из них символы ито гсЯвой комбинации по принципу большин ства. Итоговая комбинация через открытый элемент И 3, элемент ИЛИ 8 поступает в регистр 6 сдвига и в де литель 12. По сигналу с блока 15 управления остаток от деления многочлена кодовой комбинации на образующий многочлен циклического кода считывается в блок 13 памяти.Кроме того, при ненулевом остатке делитель 12выдает сигнал Ошибка на блок 7 памяти; Если комбинация не будет искажена, то в блоке 13 памяти будет записан нулевой остаток, а в блок 7 памяти не поступит сигнал Ошибка. Одновременно с записью остатка в блок113 памяти, блок 15 управления запускает запоминающий, блок 16, кото рый формирует двоичные комбинации,со ответствующие многочленам остатков, получаемых при делении многочленов кодовых комбинаций, пораженных одиночными ошибками, на образующий многочлен циклического кода. ФормиpyeNMe остатки одни за другим поступают на первые входы блока 14 срав нения, на другие входы которого поступает остаток, хранящийся в блоке 13памяти. Блок 14 сравнения сравнивает эти остатки и при совпадении, т.е. при наличии одиночной ошибки, выдает сигнал на вход элемента И 4. Момент выдачи сигнала с блока 14 сравнения на вход элемента И 4 будет соответствовать искаженному разряду кодовой комбинации, пораженной одиночной ошибкой. На второй вход элемента и 4 поступает через второй регистр 5 сдвига последовательность нулей и единиц с блока 11 определения достоверности символов, на вход которого поступают одноименные разряды повторяемых комбинаций с выхода блока 1 преобразования. Блок 11 определения достоверности символов выдает на выход сигнал , если все одноименные разряды повторяемых комбинаций совпадают, и сигнал Единица, если хотя бы один разряд отличается от других. Таким образом, единицы в последовательности единиц и нулей, выдаваемой блоком 11, следовательно и регистром 5 сдвига, будут отмечать недостоверные символы, а нули - достоверные символы, т.е. символы с малой вероятностью искажения. Элемент И 4 выдает сигнал при совпадении импульсов, выдаваемых регистром 5 сдвига (импульс недостоверности данного разряда), и импульсов, выдаваемых блоком 14 сравнения (импульс одиночной ошибки в данном раз-; ряде). Сигнал с выхода элемента И 4 поступает на один вход сумматора 9, на второй вход которого поступает информация с регистра 6 сдвига, а также на сбрасывающий вход блока 7 памяти, стирая сигнал Ошибка. На сумматоре 9 осуществляется исправление одиночной ошибки только в недостоверных символах, и исправленная комбинация поступает на первый выход устройства. В том случае, когда делитель 12 обнаружит ошибку и выдаст сигнал на блок 7 памяти, а блок 14 сравнения не выдаст сигнал, что свидетельствует о наличии многократной ошибки в комбинации, импульсом с блока 15 управления сигнал Ошибка будет сосчитан с блока 7 памяти на второ.й выход устройства. При получении этого сигнала получатель стирает искаженную комбинацию. Таким образом, в предлагаемом устройстве осуществляется исправление однократных ошибок только в недостоверных символах итоговой комбинации,, что приводит к уменьшению числа непринятых кодовых комбинаций без заметного снижения достоверности информации, и, следовательно, к повышению помехоустойчивости ее приема. Формула изобретения Устройство приема многократно передаваемых комбинаций, содержащее последовательно соединенные блок преобразования и блок мажоритарной выборки, два элемента И, два регистра сдвига, первый блок памяти, элемент ИЛИ и сумматор, отличающеес я тем, что, с целью повышения помехоустойчивости, введены декодирующий блок, блок определения достоверности символов, последовательно соединенные делитель, второй блок памяти и блок сравнения, а также блок управления и запоминающий блок, причем вход блока преобразования соединен с входом декодирующего блока, первый выход которого соединен с одним входом элемента ИЛИ, вход которого соединен через первый элемент И с вторым выходом декодирующего блока, вьлходы блока преобразования соединены с входами блока опреде ления достоверности символов, выход которого через последовательно соединенные первый регистр сдвига и вто рой элемент И соединен с одним входо сумматора, вход которого чере второй регистр сдвига соединен с вы устройства регистрации ходом элемента ИЛИ, соединенным с первым входом делителя, второй вход которого соединен с одним выходом блока, управления, соединенным с входом запоминающего блока, выходы которого соединены с входами блока сравнения, выход которого соединен с другим входом второго элемента И, выход которого соединен с первым входом первого блока памяти, вторюй и третий входы которого соединены соответственно с выходом делителя и другим выходом блока управления, выход блока мажоритарной выборки соединен с другим входом первого элемента И,при этом выходы первого блока памяти и сумматора являются выходами устройства. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 330561, кл. Н 04 L 1/10, 1970 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1985 |

|

SU1349009A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| ДЕКОДЕР С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК | 2008 |

|

RU2370887C1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Устройство для обнаружения и исправления ошибок | 1984 |

|

SU1243100A1 |

| Многоканальная кодоимпульсная система телесигнализации | 1986 |

|

SU1325544A1 |

| Устройство для передачи и приема дискретных сигналов | 1977 |

|

SU720465A2 |

| Мажоритарное декодирующее устройство | 1981 |

|

SU1005059A1 |

| Система передачи информации с решающей обратной связью | 1984 |

|

SU1167746A1 |

II

,HHq)opMa

ния

fZ

jk

, Ошибка

Авторы

Даты

1981-09-23—Публикация

1979-12-14—Подача