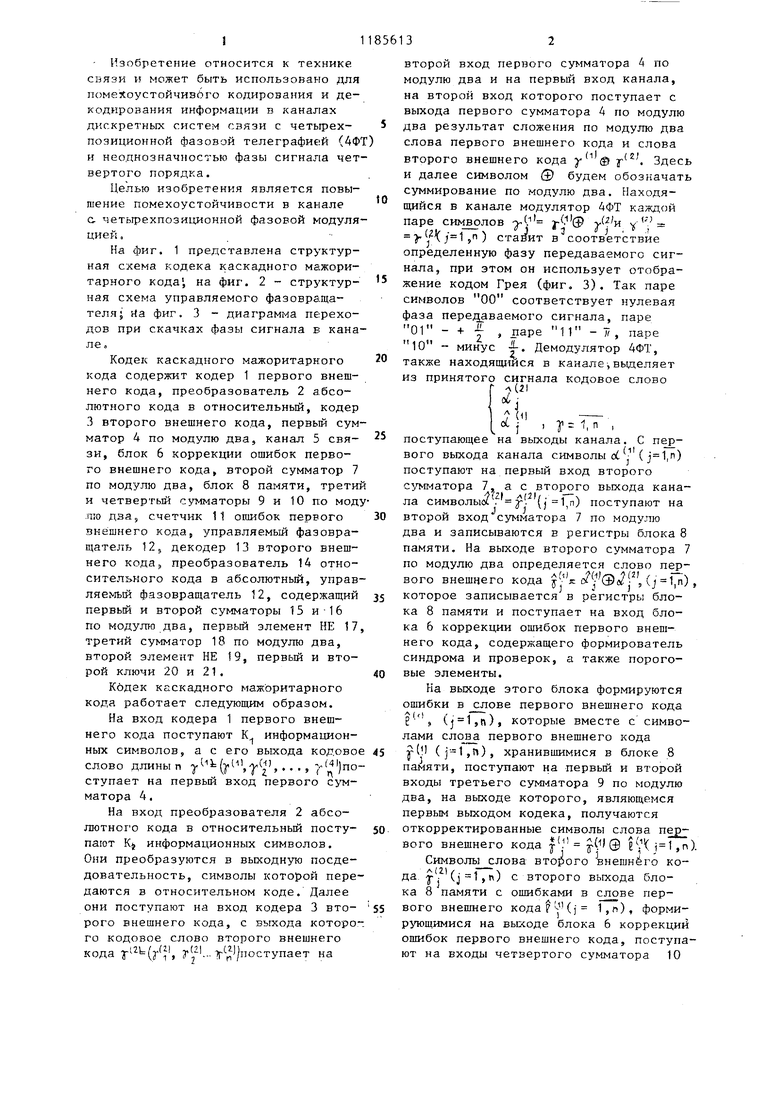

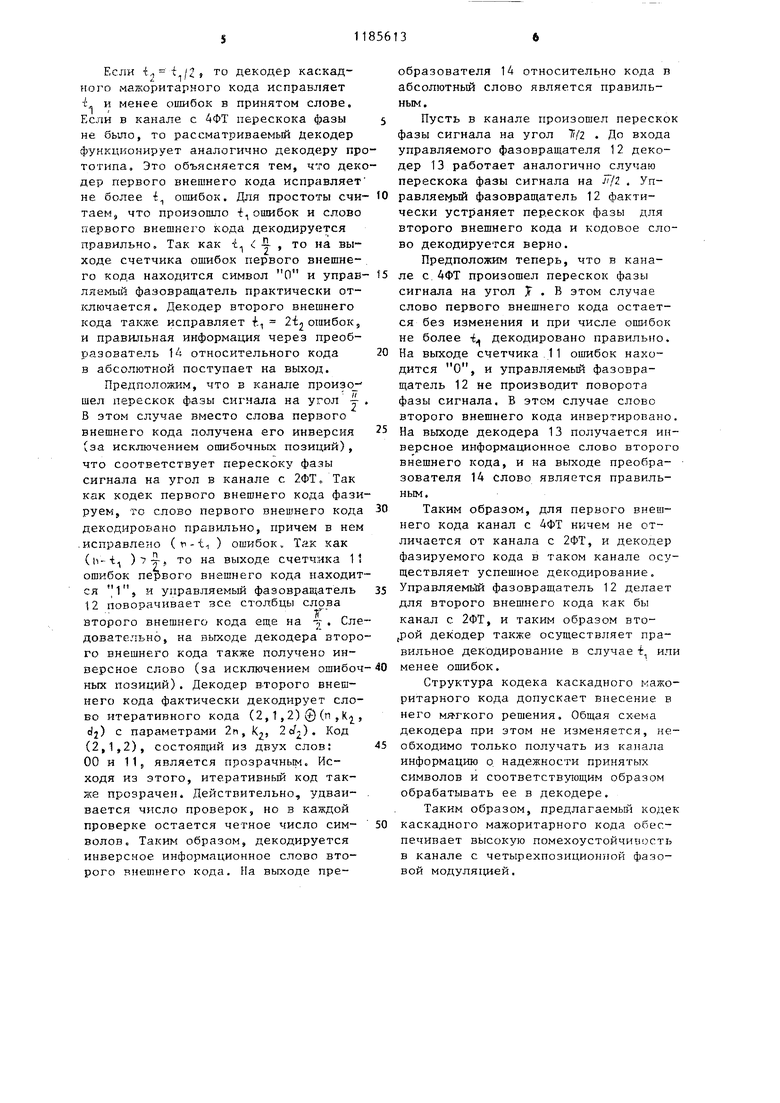

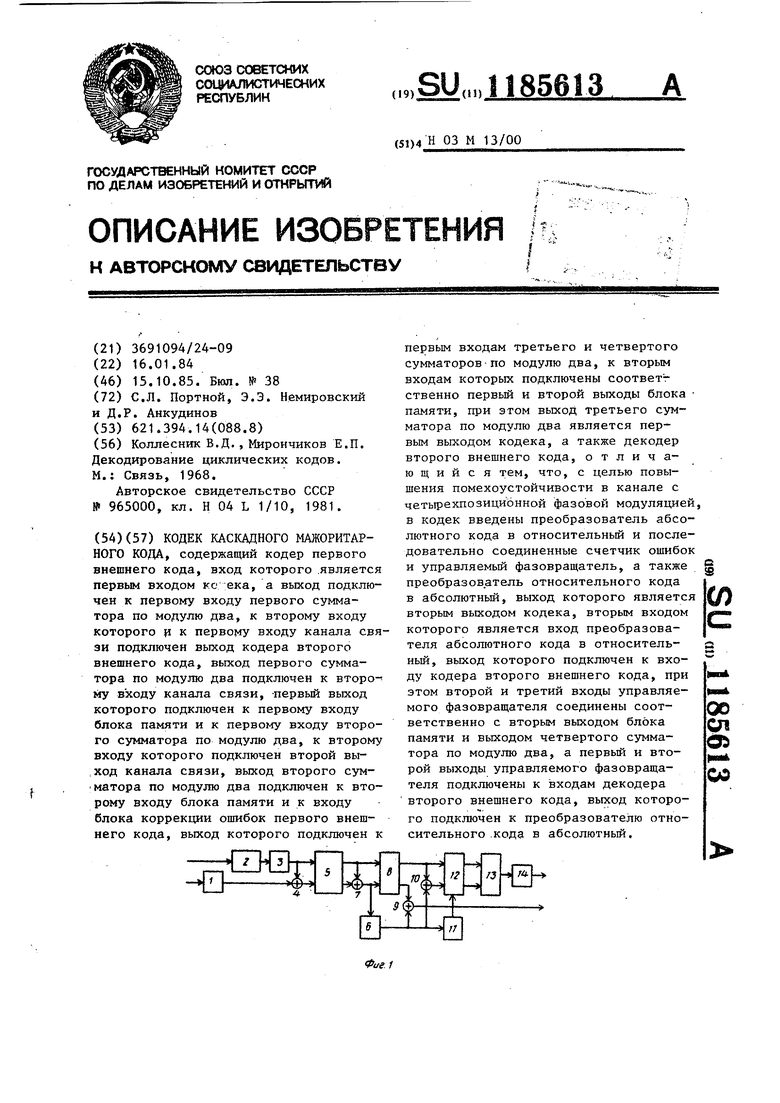

Изобретение относится к технике связи и может быть использовано для помеХоустойчивбго кодирования и декодирования информации в каналах дискретных систем связи с четырехпозиционной фазовой телеграфией (4Ф и неоднозначностью фазы сигнала чет вертого порядка. Целью изобретения является повышение помехоустойчивости в канале а четырехпозиционной фазовой модуля цией . На фиг. 1 представлена структурная схема кодека каскадного мажоритарного кода , на фиг. 2 - структурная схема управляемого фазовра11цателя; Иа фиг. 3 - диаграмма переходов при скачках фазы сигнала в кана ле. Кодек каскадного мажоритарного кода содержит кодер 1 первого внешнего кода, преобразователь 2 абсолютного кода в относительный, кодер 3 второго внешнего кода, первый сум матор 4 по модулю два, канал 5 связи, блок 6 коррекции ошибок первого внешнего кода, второй сумматор 7 по модулю два, блок 8 памяти, трети и четвертый сумматоры 9 и 10 по мод .а;о два, счетчик 11 ошибок первого внешнего кода, управляемый фазовращатель 12 декодер 13 второго внешнего кода преобразователь 14 относителького кода в абсолютный, управ ляемый фазовращатель 12, содержащий первьй и второй сумматоры 15 н-16 по модулю два, первый элемент НЕ 17 третий сумматор 18 по модулю два, второй элемент НЕ 19, первый и второй ключи 20 и 21, Кодек каскадного мажоритарного кода работает следующим образом. На вход кодера 1 первого внешнего кода поступают К информационных символов, а с его выхода кодово слово длины п ( п) ступает на первый вход первого сумматора 4. На вход преобразователя 2 абсолютного кода в относительный поступают Kj( информационных символов. Они преобразуются в выходную посдедовательность, символы которой пере даются в относительном коде. Далее они поступают на вход кодера 3 второго внешнего кода, с выхода которо го кодовое слово второго внешнего кода yj.-lrnl ° y второй вход первого сумматора 4 по модулю два и на первый вход канала, на второй вход которого поступает с выхода первого сумматора 4 по модулю два результат сложения по модулю два слова первого внешнего кода и слова второго внешнего кода у Здесь и далее символом Ql будем обозначать суммирование по модулю два. Находящийся Б канале модулятор 4ФТ каждой паре символов -j-. / ) ставит в соответствие определенную фазу передаваемого сигнала, при этом он использует отображение кодом Грея (фиг, 3). Так паре символов 00 соответствует нулевая фаза перед}аваемого сигнала, паре 01 - -)- I , паре 11 - 17, паре 10 - минус |-. Демодулятор 4ФТ, также находящийся в канале выделяет из принятого сигнала кодовое слово л(г1 7 (1 , 1 1, п , поступающее на выходы канала. С первого выхода канала символы оС . (,i) поступают на первый вход второго с тиг- атора 7, а с второго выхода канала символы . . {),п) поступают на второй вход сумматора 7 по модулю два и записываются в регистры блока 8 памяти. На выходе второго сумматора 7 по модулю два определяется слово первого внешнего кода j , (j 1,п) , которое записывается в регистры блока В памяти и поступает на вход блока 6 коррекции ошибок первого внешнего кода, содержащего формирователь синдрома и проверок, а также пороговые элементы, Ка выходе этого блока формируются ошибки в слове первого внешнего кода нЧ () которые вместе с символами первого внешнего кода г( (j-1,f) хранившимися в блоке 8 памяти, поступают на первый и второй входы третьего сум1-1атора 9 по модулю два, на выходе которого, являющемся первым выходом кодека, получаются откорректированные символы слова первого внешнего кода |Я j-( )@ ,n). Символы слова второго внешнего кода, j3 (j 1 , п) с второго выхода блока 8 памяти с ошибками в слове первого внешнего ( 1,) формирующимися на выходе блока 6 коррекций ошибок первого внешнего кода, поступают на входы четвертого сумматора 10

Если /2 то декодер каскадного мажоритарного кода исправляет L и менее оишбок в принятом слове, Если в канале с АФТ перескока фазы не было, то рассматриваемый декодер функционирует аналогично декодеру прототипа. Это объясняется тем, что декодер первого внешнего кода исправляет не более i ошибок. Для простоты считаем, что произошло -t, ошибок и слово первого внешнего кода декодируется правильно. Так как i ; -Л- , то на выходе счетчика ошибок первого внешнего кода находится символ О и управЛЛ8МЫЙ фазовращатель практически отключается. Декодер второго внешнего кода также исправляет i, ошибок, и правильная информация через преобразователь относительного кода в абсолютной поступает на выход.

Предположим, что в канапе произо шел перескок фазы сигнала на угол у . В этом случае вместо слова первого внешнего кода получена его инверсия (за исключением ошибочных позиций), что соответствует перескоку фазы сигнала на угол в канале с 2ФТ, Так как кодек первого внешнего кода фазируем, то слово первого внешнего кода декодировано правильно, причем в нем .исправлено (n-t ) ошибок. Так как (h-i )7-, то на выходе счетчика 1 ошибок первого внешнего кода находится , и управляемьш фазовращатель 12 поворачивает все столбцы слова

второго внешнего кода еще на -,- . Следовательно, на выходе декодера второго внешнего кода также получено инверсное слово (за исключением ошибочных позиций), Декодер второго внешнего кода фактически декодирует слово итеративного кода (2,1,2) (Э (п ,К , dj) с параметрами 2п, К, , Код (2,1,2), состоящий из двух слов; 00 и 11, является прозрачным. Исходя из этого, итеративный код также прозрачен. Действительно, удваивается число проверок, но в каждой проверке остается четное число символов. Таким образом, декодируется инверсное информационное слово второго внешнего кода. Па выходе преобразователя 14 относительно кода в абсолютный слово является правильным.

Пусть в канале произошел переско фазы сигнала на угол Tiji . До входа управляемого фазовращателя 12 декодер 13 работает аналогично случаю перескока фазы сигнала на . Управляемый фазовращатель 12 фактически устраняет перескок фазы для второго внешнего кода и кодовое слово декодируется верно.

Предположим теперь, что в канале с 4ФТ произошел перескок фазы сигнала на угол 7 . В этом случае слово первого внешнего кода остается без изменения и при числе ошибок не более -t декодировано правильно. На выходе счетчика 11 ошибок находится О, и управляемый фазовращатель 12 не производит поворота фазы сигнала. В этом случае слово второго внешнего кода инвертировано На выходе декодера 13 получается инверсное информационное слово второг внешнего кода, и на выходе преобразователя 14 слово является правильным .

Таким образом, для первого внешнего кода канал с 4ФТ ничем не отличается от канала с 2ФТ, и декодер фазируемого кода в таком канале осуществляет успешное декодирование, Управляемйй фазовращатель 12 делает для второго внешнего кода как бы канал с 2ФТ, и таким образом второй декодер также осуществляет правильное декодирование в случае f, ил менее ошибок.

Структура кодека каскадного мажоритарного кода допускает внесение в него мЯГкого решения. Общая схема декодера при этом не изменяется, необходимо только получать из канала информацию о, надежности принятых символов и соответствующим образом обрабатывать ее в декодере.

Таким образом, предлагаемый коде каскадного мажоритарного кода обеспечивает высокую помехоустойчивость в канале с четырехпозиционпой фазовой модулягщей.

ВхоВ

л on l

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек блочных кодов | 1984 |

|

SU1270899A1 |

| Кодек блочного кода | 1985 |

|

SU1358098A1 |

| Кодек блочных кодов | 1988 |

|

SU1640829A1 |

| Кодек мажоритарного блочного кода | 1981 |

|

SU965000A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Кодек каскадного блочного кода | 1985 |

|

SU1338075A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Кодек блочных кодов | 1987 |

|

SU1473088A1 |

| Кодек двоичных блочных кодов | 1986 |

|

SU1408532A1 |

КОДЕК КАСКАДНОГО МАЖОРИТАРНОГО КОДА, содержащий кодер первого внешнего кода, вход которого .является первым входом кс ека, а выход подключен к первому входу первого сумматора по модулю два, к второму входу которого и к первому входу канала связи подключен выход кодера второго внешнего кода, выход первого сумматора по модулю два подключен к второму входу канала связи, -первый выход которого подключен к первому входу блока памяти и к первому входу второго сумматора по модулю два, к второму входу которого подключен второй вы:Ход канала связи, выход второго сумматора по модулю два подключен к второму входу блока памяти и к входу блока коррекции ошибок первого внешнего кода, выход которого подключен к первым входам третьего и четвертого сумматоров по модулю два, к вторым входам которых подключены соответг ственно первый и второй выходы блока памяти, при этом выход третьего сумматора по модулю два является первым выходом кодека, а также декодер второго внешнего кода, отличающийся тем, что, с целью повышения помехоустойчивости в канале с четырехпозиционной фазовой модуляцией, в кодек введены преобразователь абсолютного кода в относительный и последовательно соединенные счетчик ошибок и управляемый фазовращатель, а также преобразователь относительного кода (Л в абсолютный, выход которого является вторым выходом кодека, вторым входом которого является вход преобразователя абсолютного кода в относительный, выход которого подключен к входу кодера второго внешнего кода, при этом второй и третий входы управляемого фазовращателя соединены соот00 ветственно с вторым выходом блока ел dd памяти и выходом четвертого сумматора по модулю два, а первый и второй выходы управляемого фазовраща00 теля подключены к входам декодера второго внешнего кода, выход которого подключен к преобразователю относительного .кода в абсолютный.

Фиг. Z

| Коллесник В.Д | |||

| , Мирончиков Е.П | |||

| Декодирование циклических кодов | |||

| М.; Связь, 1968 | |||

| Кодек мажоритарного блочного кода | 1981 |

|

SU965000A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-10-15—Публикация

1984-01-16—Подача