со х

О5

ю

00

ю

фиг. /

Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки информации, организованной в пакеты. Эта информация обрабатывается с учетом вероятностных характеристик каналов передачи информации, в частности каналов, свойства которых меняются во времени. В первом приближе-ю и генератор логического О, выходы

НИИ такой канал может быть охарактеризован двумя состояниями - хорошее (х) и плохое (п) и называется соответственно X-каналом и п-каналом, - Цель изобретения - повышение достоверности декодирования при приеме дискретных сигналов из канала связи с переменными параметрами.

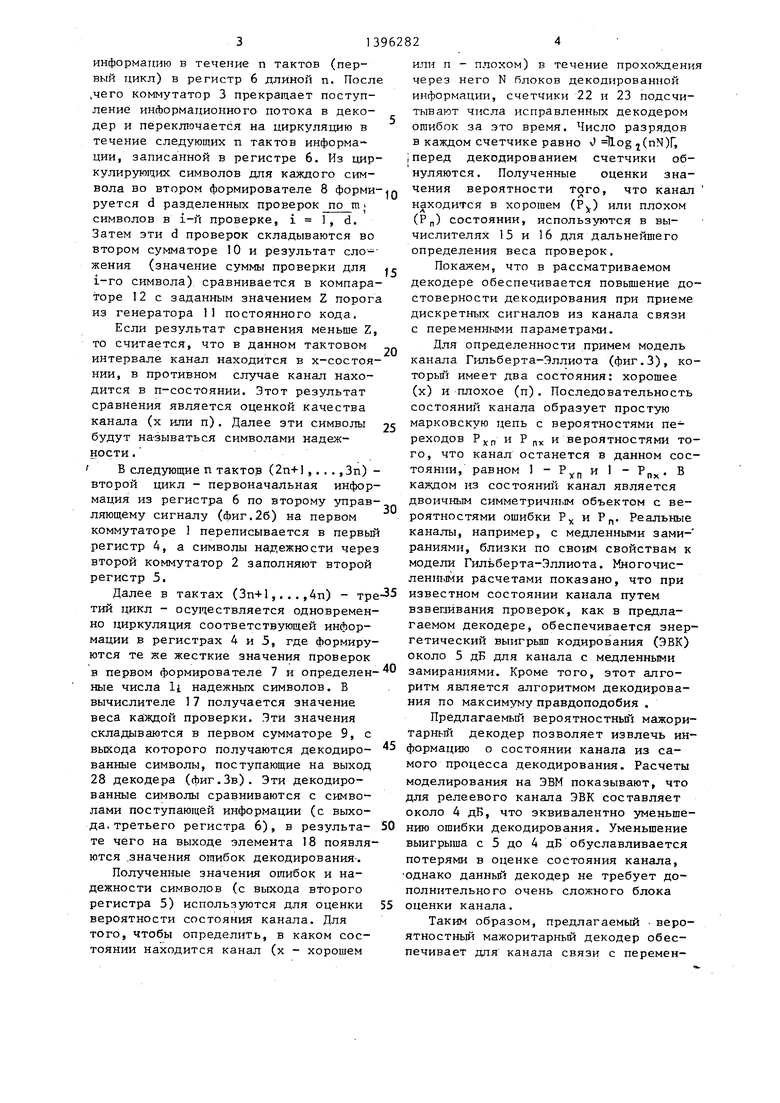

На фиг. 1 изображена функциональная схема вероятностного мажоритарного декодера; на фиг. 2 - временные диаграммы, поясняющие его работу; на фиг. 3 - модель канала передачи с переменными параметрами.

15

20

которых соединены с соответствующими выходами генератора II, число которы сГ .

Блок I3 сумматоров служит для определения числа надежных символов во всех d проверках и выполнен на d (т(-)-входовых полных сумматорах. Чис ло выходов i-ro сумматора т. общее число выходов блока 13 W

d

г W..

Каждьй из вычислителей 15-17 выполнен на d программируемых постоянных запоминаквдих устройствах (ГШЗУ).

Каждьй из вычислителей 15-17 выполнен на d программируемых постоянных запоминаквдих устройствах (ГШЗУ).

Вероятностный мажоритарный декодер 25 В каждом i-м ГШЗУ первого вычислите- содержит первый 1, второй 2 и третий ля 15 по сигналу j е fO,2 -I} с блои

35

3 коммутаторы, первый 4, второй 5 третий 6 регистры, первый 7 и второй 8 формирователи проверок, первый 9 и второй 10 сумматоры, генератор П зо постоянного кода, компаратор 12, блок 13 сумматоров, блок 14 элементов НЕ, первый 15 и второй 16 вычислители оценки вероятности, вычислитель 17 веса проверок, элемент 18 неравнозначности, элемент НЕ 19, первый 20 и второй 21 элементы И, первый 22 и второй 23 счетчики. На фиг. 1 обозначены информационный 24 и тактовый 25 входы, первый 26 и вто- рой 27 управляющие входы и выход 28. . Вероятностный мажоритарный декодер предназначен для обработки информации, закодированной циклическим кодом (п, k, d) с параметрами: п - длина кода; k - количество информационных символов; d - число разделенных проверок (расстояние Хемминга).

Формирователь 7(8) проверок служит для формирования жестких значений проверок и выполнен на d (т)-входо- вых сумматорах по модулю два, причем

XI m М, га - число символов, вхо- bi

дящих в i-ю разделенную проверку (на фиг. 1 указаны размерности входов и 55 выходов сооветствующих блоков).

Первьй сумматор 9 является сумматором по модулю два. Второй сумматор

ка 13 и сигналу Р со счетчика 22 вычисляется оценка

е,.

х (1 - 2Р,)

45

50

В каждом i-M ЛПЯУ второго вычислителя 16 по сигналу 1; с блока 14 и сигналу РП со счетчика 23 вычисляется оценка

(,,. о - 2Р,f- -,

где га / - число символов в i-й проверке;

1 с - число символов в i-й проверке, соответствующей Х-кана- лу. .

По .этим оценкам в каждом i-м ППЗУ вычислителя 17 вычисляется .вес Q i-й проверки

л л

Q wfi-e4 -.

где W +1 -или -I - сигнал на первом

(знаковом) входе i-ro ППЗУ вычислителя 17 (с .; формирователя 7). Вероятностный мажоритарный деко- дер работает следуюидим образом.

На вход 24 декодера поступает блок информации из п бит, где п - длина указанного кода (п, k, d). Коммутатор 3 по команде первого управляющего сигнала (фиг.2а) переписывает эту

10 является двоичным сумматором, число выходов которого tT Tinged Г, где Х1 - наименьшее больгаее пелое, т.е. целовая часть числа X плюс I.

Генератор 11 постоянного кода - это генератор сО-разрядного числа Z (значение порога в двоичной форме), содержащий генератор логической 1

которых соединены с соответствующими выходами генератора II, число которых сГ .

Блок I3 сумматоров служит для определения числа надежных символов во всех d проверках и выполнен на d (т(-)-входовых полных сумматорах. Число выходов i-ro сумматора т.Г, общее число выходов блока 13 W

d

г W..

Каждьй из вычислителей 15-17 выполнен на d программируемых постоянных запоминаквдих устройствах (ГШЗУ).

В каждом i-м ГШЗУ первого вычислите- ля 15 по сигналу j е fO,2 -I} с блоВ каждом i-м ГШЗУ первого вычислите- ля 15 по сигналу j е fO,2 -I} с блока 13 и сигналу Р со счетчика 22 вычисляется оценка

е,.

х (1 - 2Р,)

В каждом i-M ЛПЯУ второго вычислителя 16 по сигналу 1; с блока 14 и сигналу РП со счетчика 23 вычисляется оценка

(,,. о - 2Р,f- -,

где га / - число символов в i-й проверке;

1 с - число символов в i-й проверке, соответствующей Х-кана- лу. .

По .этим оценкам в каждом i-м ППЗУ вычислителя 17 вычисляется .вес Q i-й проверки

л л

Q wfi-e4 -.

где W +1 -или -I - сигнал на первом

(знаковом) входе i-ro ППЗУ вычислителя 17 (с .; формирователя 7). Вероятностный мажоритарный деко- дер работает следуюидим образом.

На вход 24 декодера поступает блок информации из п бит, где п - длина указанного кода (п, k, d). Коммутатор 3 по команде первого управляющего сигнала (фиг.2а) переписывает эту

15

информацию в течение п тактов (первый цикл) в регистр 6 длино п. После

.чего коммутатор 3 прекращает поступление информационного потока в декодер и переключается на циркуляцию в течение следующих п тактов информа ции, записанной в регистре 6. Из циркулирующих символов для каждого символа во втором формирователе 8 форми- п руется d разделенных проверок по т; символов в 1-й проверке, i 1, d. Затем эти d проверок складываются во втором сумматоре 10 и результат ело- жения (значение суммы проверки для i-ro символа) сравнивается в компараторе 12 с заданным значением Z порога из генератора 11 постоянного кода.

Если результат сравнения меньше Z, то считается, что в данном тактовом интервале канал находится в х-состоя- нии, в противном случае канал находится в п-состоянии. Этот результат сравнения является оценкой качества канала (х или п). Далее эти символы будут называться символами надежности .

В следующие п тактов (2п+1,...,3п) - второй цикл - первоначальная информация из регистра 6 по второму управляющему сигналу (фиг.26) на первом коммутаторе 1 переписывается в первый регистр 4, а символы надежности через второй коммутатор 2 заполняют второй регистр 5.

или п - плохом) в течение прохо5кдения через него N блоков декодированной информации, счетчики 22 и 23 подсчитывают числа исправленных декодером ошибок за это время. Число разрядов в каждом счетчике равно О Tlog ,(пН)Г, перед декодированием счетчики обнуляются. Полученные оценки значения вероятности того, что канал находится в хорошем (Ру) или плохом (РП) состоянии, используются в вычислителях 15 и 16 для дальнейшего определения веса проверок.

Покажем, что в рассматриваемом декодере обеспечивается повышение достоверности декодирования при приеме дискретных сигналов из канала связи с переменными параметрами.

Для определенности примем модель канала Гильберта-Эллиота (фиг.З), кото рьй имеет два состояния: хорошее (х) и плохое (п). Последовательность состояний канала образует простую марковскую цепь с вероятностями переходов РХП и Р пх и вероятностями того, что канал останется в данном сос20

25

тоянии, равном

РХП и

в

30

каждом из состоянии канал является двоичным симметричн1,1М объектом с вероятностями ошибки Р и Pp. Реальные каналы, например, с медленными зами- раниями, близки по своим свойствам к модели Гильберта-Эллиота. Многочисленными расчетами показано, что при

Далее в тактах (Зп+1,...,4п) - тре-35 известном состоянии канала путем тий цикл - осуществляется одновремен- взвепйвания проверок, как в предла- но циркуляция соответствующей инфор- гаемом декодере, обеспечивается энер- мации в регистрах 4 и 5, где формиру- гетический выигрыш кодирования (ЭВК)

ются те же жесткие значения проверок в первом формирователе 7 и определен ные числа li надежных символов. В вычислителе 17 получается значение веса ка:ждой проверки. Эти значения складываются в первом сумматоре 9, с выхода которого получаются декодированные символы, поступающие на выход 28 декодера (фиг.Зв). Эти декодированные символы сравниваются с символами поступающей информации (с выхода, третьего регистра 6), в результате чего на выходе элемента 18 появляются .значения ошибок декодирования-. Полученные значения ошибок и надежности символов (с выхода второго регистра 5) используются для оценки вероятности состояния канала. Для того, чтобы определить, в каком состоянии находится канал (х - хорошем

15

п

62824

или п - плохом) в течение прохо5кдения через него N блоков декодированной информации, счетчики 22 и 23 подсчитывают числа исправленных декодером ошибок за это время. Число разрядов в каждом счетчике равно О Tlog ,(пН)Г, перед декодированием счетчики обнуляются. Полученные оценки значения вероятности того, что канал находится в хорошем (Ру) или плохом (РП) состоянии, используются в вычислителях 15 и 16 для дальнейшего определения веса проверок.

Покажем, что в рассматриваемом декодере обеспечивается повышение достоверности декодирования при приеме дискретных сигналов из канала связи с переменными параметрами.

Для определенности примем модель канала Гильберта-Эллиота (фиг.З), кото рьй имеет два состояния: хорошее (х) и плохое (п). Последовательность состояний канала образует простую марковскую цепь с вероятностями переходов РХП и Р пх и вероятностями того, что канал останется в данном сос20

25

тоянии, равном

РХП и

в

около 5 дБ для канала с медленными 40 замираниями. Кроме того, этот алгоритм является алгоритмом декодирования по максимуму правдоподобия ,

Предлагаемьш вероятностньп мажори- тарньш декодер позволяет извлечь ин45 формацию о состоянии канала из самого процесса декодирования. Расчеты моделирования на ЭВМ показывают, что для релеевого канала ЭВК составляет около 4 дБ, что эквивалентно уменьше50 нию ошибки декодирования. Уменьшение выигрыша с 5 до 4 дБ обуславливается потерями в оценке состояния канала, однако данньй декодер не требует дополнительного очень сложного блока

55 оценки канала.

Таким образом, предлагаемьй -веро- ятностньй мажоритарный декодер обеспечивает для канала связи с переменными параметрами увеличение энергетического выигрыша кодирования.

Формула изобретения

Вероятностный мажоритарный декодер, содержащий первый сумматор, первый и второй коммутаторы, выход каждого из которых соединен с информа- )Q ционным входом одноименного регистра, параллельные выходы первого регистра |подключены к соответствующим входам |первого формирователя проверок, о т- |л и ч а ю щ .и и с я тем, что, с це- .с лью повышения достоверности декодирования при приеме дискретных сигналов из канала связи с переменными па13962826

объединены и являются тактовым входом декодера, параллельные выходы третьего регистра подключены к входам второго формирователя проверок, выходы которого соединены с входами второго сумматора, выходы которого и )зыходы генератора постояннстго кода подключены соответственно к первым и вторым входам компаратора, выход которо го соединен с первым информационным входом второго коммутатора, последовательный выход первого регистра соединен с вторым информационным входом первого коммутатора, последовательный выход второго регистра подключен к второму информационному входу второго коммутатора, первому входу первого элемента И и через элемент НЕ 1раметрами, в декодер введены второй

|сумматор, второй формирователь-прове-20к первому входу второго элемента И,

jpoK, генератор постоянного кода, ком-параллельные выходы второго регистра

аратор, блок сумматоров, блок эле-соединены с соответствующими входами

Центов НЕ, первый и второй вычисли-блока сумматоров, выходы которого

гели оценки вероятности, вычислительподключены к первым входам первого

Ьеса проверок, первый и второй счет- 25вычислителя оценки вероятности и вхоНики, элемент неравнозначности, эле- НЕ, первый и второй элементы И, 1гре|гий регистр и третий коммутатор, tiepBbtfi информационный и управляющий которого являются соответственно информационным и первым зшрав- фяющим входами декодера, выход тре- tbero коммутатора соединен с информа- |щонным входом третьего регистра, по- фледовательньй выход которого подключен к первому входу элемента неравно- начности, второму информационному третьего коммутатора и первому 1 нформационному входу первого комму- т атора, управляющий вход которого Объединен с управляющим входом вто- ого коммутатора и является.вторым управляющим входом декодера, тактовые Входы первого - третьего регистров

дам блока элементов НЕ, выходы которого соединены с первыми входами второго вычислителя оценки вероятности, выходы первого формирователя прове- Q рок, первого и второго вычислителей оценки вероятности подключены соответственно к первым - третьим входам вычислителя веса проверок, выходы которого соединены с входами первого сумматора, выход которого соединен с вторым входом элемента неравнозначности и является выходом декодера, выход элемента неравнозначности подключен к вторым входам первого ,и второго элементов И, выходы которых соединены с входами одноименных счетчиков, выходы которых подключены к вторым входам одноименных вычислителей оценки вероятности.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностный мажоритарный декодер | 1989 |

|

SU1647915A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| СПОСОБ ОБРАБОТКИ И ПРИЕМНИК СООБЩЕНИЙ ЦИРКУЛЯРНЫХ ОДНОСТОРОННИХ СЕТЕЙ ПЕРЕДАЧИ ДАННЫХ С ПОВТОРЕНИЯМИ | 2016 |

|

RU2643441C2 |

| Кодек блочного кода | 1985 |

|

SU1358098A1 |

| Декодер мажоритарных блоковых кодов | 1986 |

|

SU1349011A1 |

| СПОСОБ РАБОТЫ СИМВОЛЬНОГО ПОРОГОВОГО ЭЛЕМЕНТА В СИМВОЛЬНОМ МАЖОРИТАРНОМ ДЕКОДЕРЕ | 2014 |

|

RU2573741C2 |

| Устройство для исправления ошибок в информации, закодированной циклическим кодом | 1974 |

|

SU512589A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

Изобретение относится к вычислительной технике. Его использование в системах передачи и обработки информации, организованной в пакеты, позволяет повысить достоверность декодирования при приеме дискретных сигналов из канала связи с переменными параметрами. Вероятностный мажоритарный декодер содержит коммутаторы 1, 2, регистры 4, 5, Лормирователь 7 проверок и сумматор 9. Введение коммутатора 3, регистра 6, формирователя 8 проверок, сумматора 10, генератора 11 постоянного кода, компаратора 12, блока 13 сумматоров, блока 14 элементов НЕ, вычислителей 15, 16 оценки вероятности,вычислителя 17 веса проверок, элемента 18 неравнозначности, элемента НЕ 19, элементов И 20,. 21 и счетчиков 22, 23 обеспечивает декодирование с учетом вычисляемых надежностей символов, а также определение состояния канала связи и использование этой оценки для взвешенного декодирования. 3 ип. S сл

Фиг.г

/ /гх

/-

ЗЮ

/ /гх

/- Рпус.

1-Рп

Фиг.

| Зарубежная радиоэлектроника, 1986, № 7, с | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Зарубежная радиоэлектроника, 1985, № 7, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-15—Публикация

1986-11-17—Подача