I13

Изобретение относится к автоматике и может быть использовано в системах дискретной передачи, например звуковых сигналов.

Цель изобретения - повышение точности кодирования.

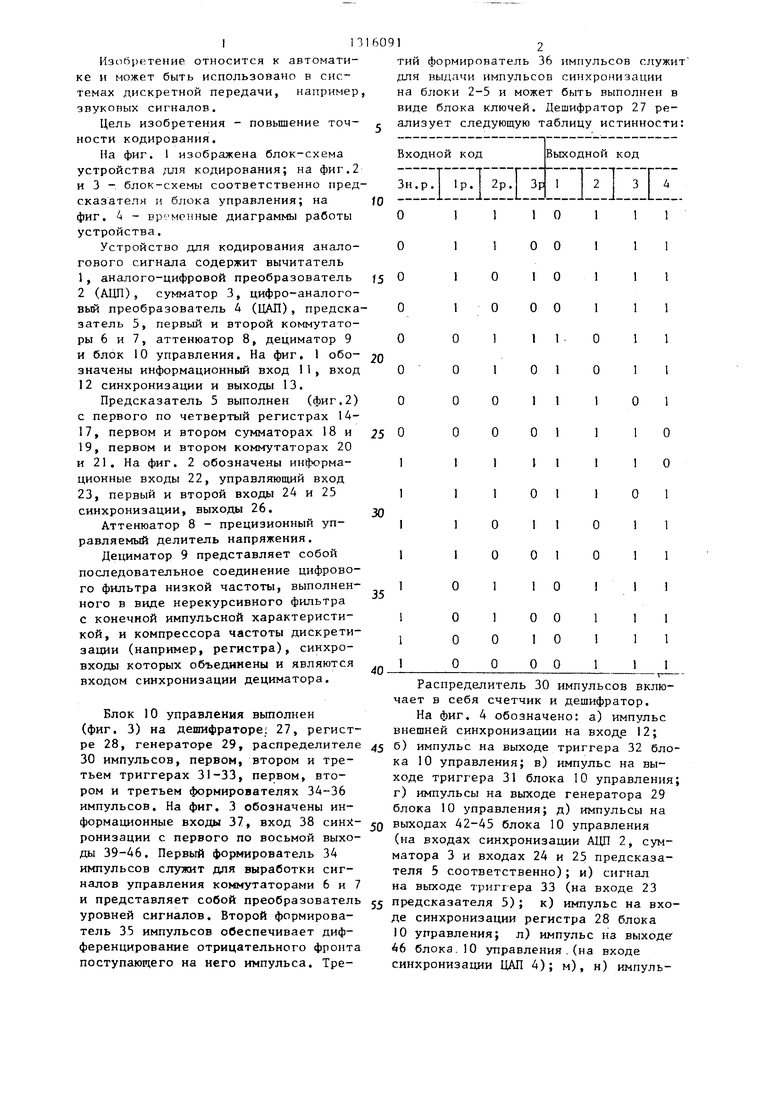

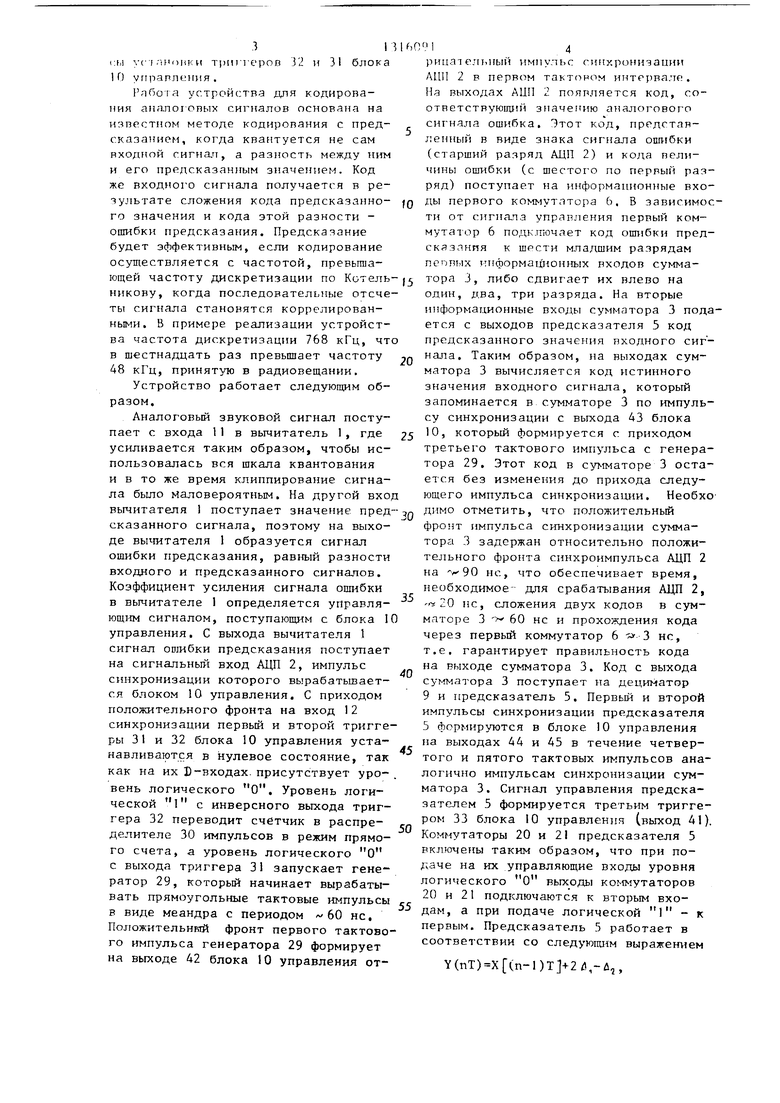

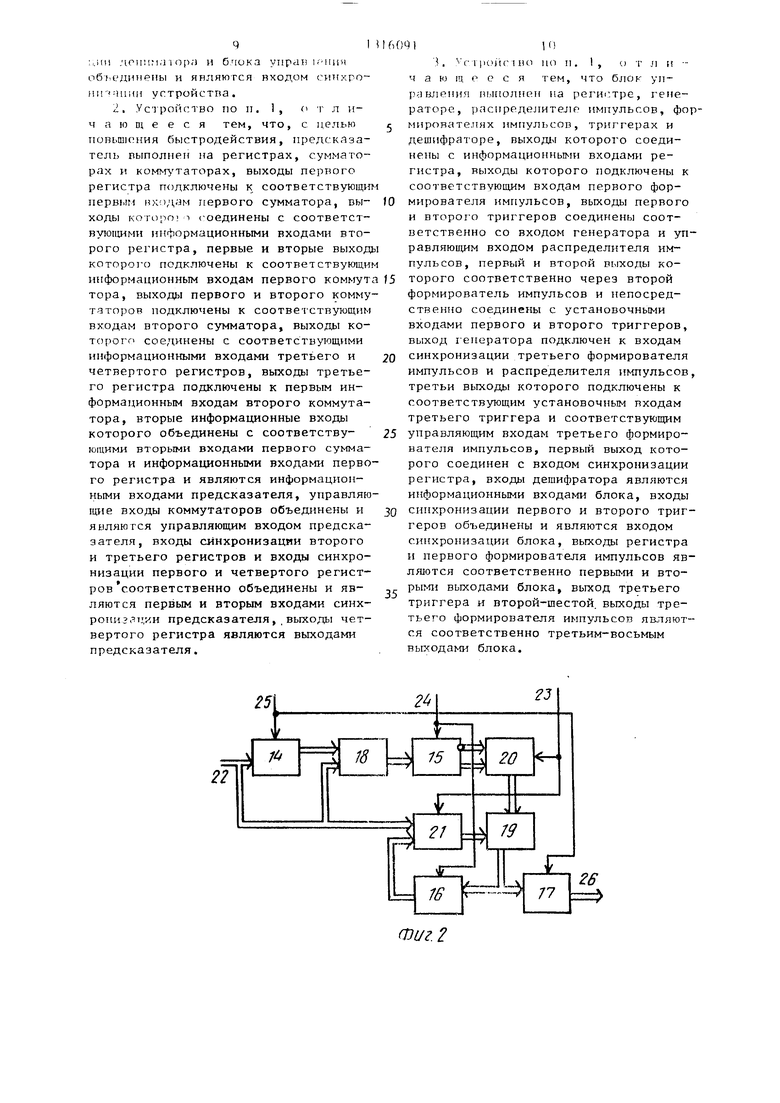

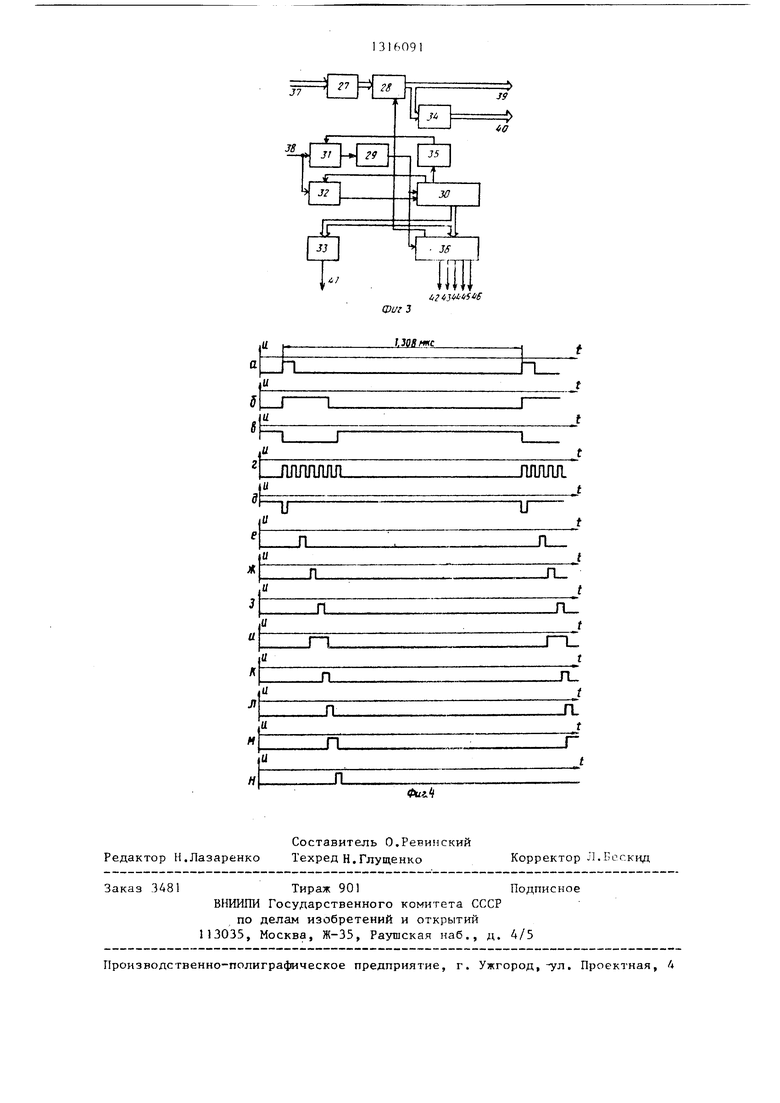

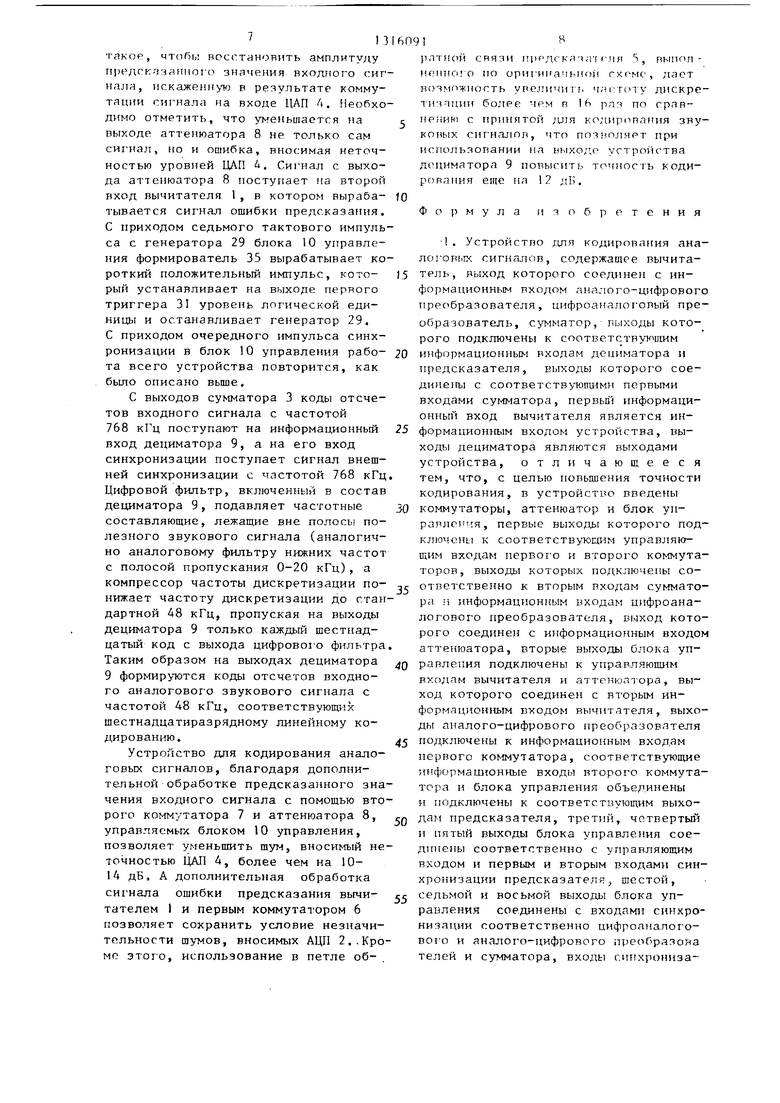

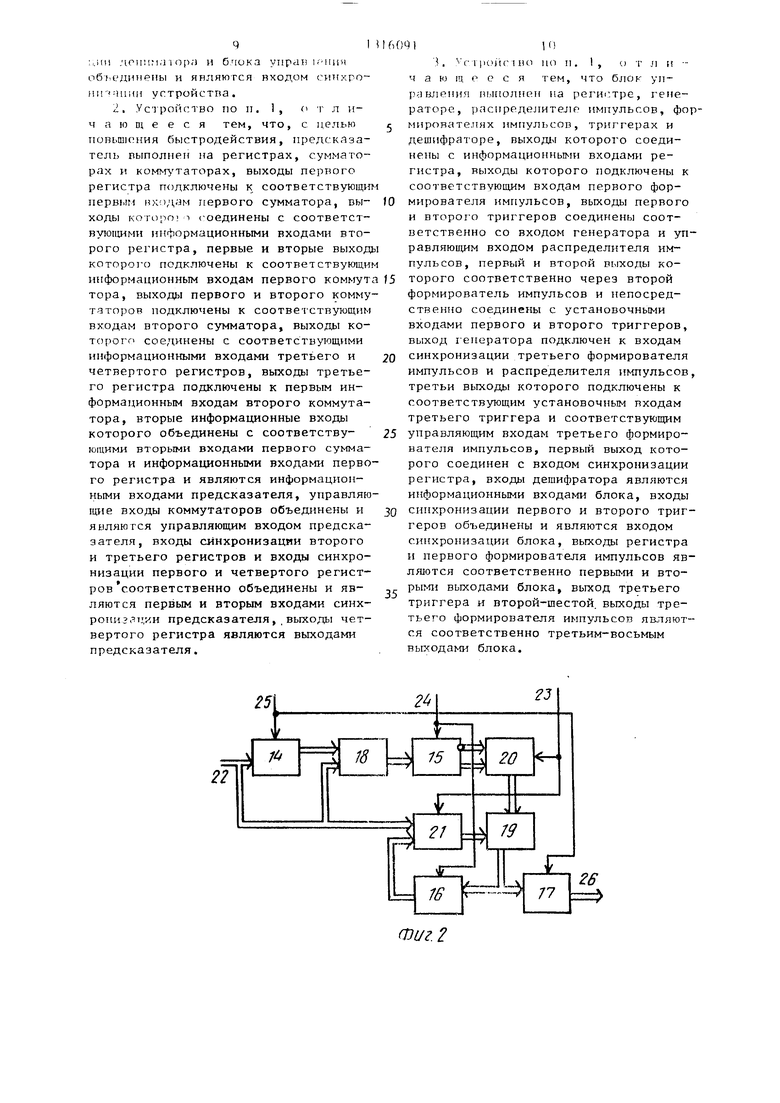

На фиг. I изображена блок-схема устройства для кодирования; на фиг.2 и 3 - блок-схемы соответственно предсказателя н блока управления; на фиг. 4 - вр ; менные диаграммы работы устройства.

Устройство для кодирования аналогового сигнала содержит вычитатель 1, аналого-цифровой преобразователь 2 (АДП), сумматор 3, цифро-аналоговый преобразователь Д (ЦАП), предсказатель 5, первый и второй коммутаторы 6 и 7, аттенюатор 8, дециматор 9 и блок 10 управления. На фиг, 1 обозначены информационный вход 11, вход 12 синхронизации и выходы 13.

Предсказатель 5 выполнен (фиг.2) с первого по четвертый регистрах 14- 17, первом и втором сумматорах 18 и 19, первом и втором коммутаторах 20 и 21. На фиг. 2 обозначены информационные входы 22, управляющий вход 23, первый и второй входы 24 и 25 синхронизации, выходы 26.

Аттенюатор 8 - прецизионный управляемый делитель напряжения.

Дециматор 9 представляет собой последовательное соединение цифрового фильтра низкой частоты, выполненного в виде нерекурсивного фильтра с конечной импульсной характеристикой, и компрессора частоты дискретизации (например, регистра), синхро- входы которых объединены и являются входом синхронизации дециматора.

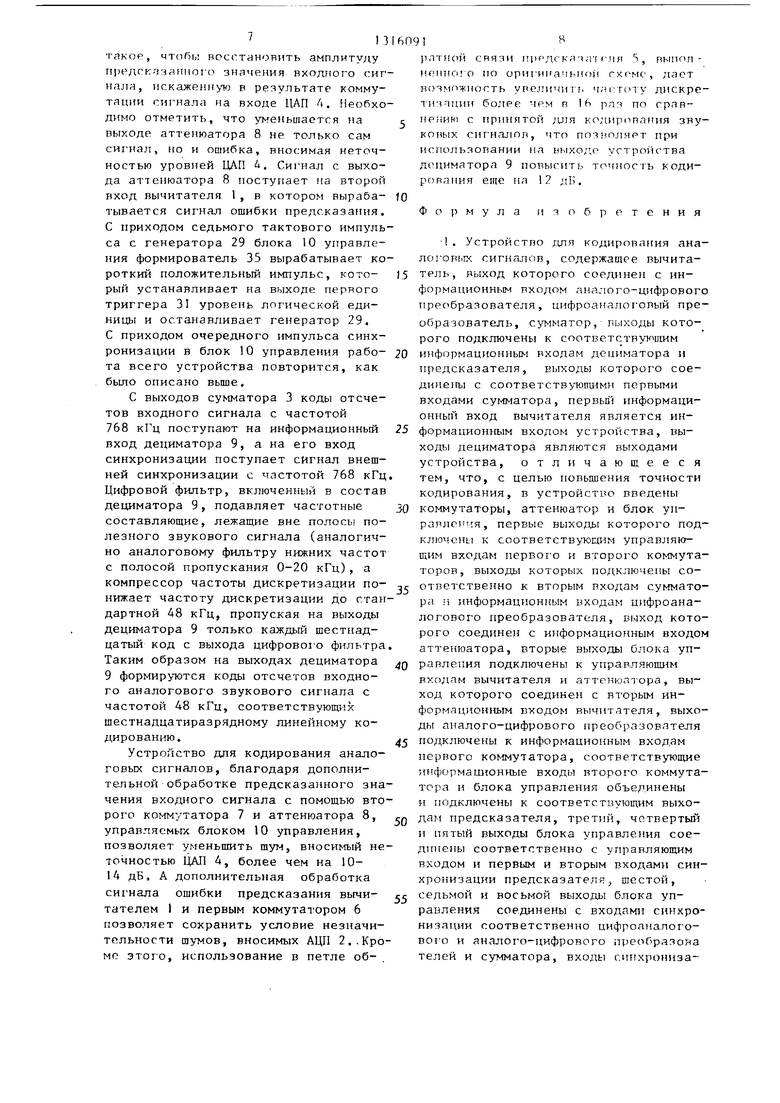

Блок 10 управления вьтолнен (фиг. 3) на дешифраторе; 27, регистре 28, генераторе 29, распределителе 30 импульсов, первом, втором и третьем триггерах 31-33, первом, втором и третьем формирователях 34-36 импульсов. На фиг. 3 обозначены информационные входы 37, вход 38 синхронизации с первого по восьмой выходы 39-46. Первый формирователь 34 импульсов служит для выработки сигналов управления коммутаторами б и 7 и представляет собой преобразователь уровней сигналов. Второй формирователь 35 импульсов обеспечивает дифференцирование отрицательного фронта поступающего на него импульса. Тре6091

тий формирователь 36 импульсов служит для выдачи импульсов синхронизации на блоки 2-5 и может быть выполнен в виде блока ключей. Дешифратор 27 реализует следующую таблицу истинности:

Распределитель 30 импульсов включает в себя счетчик и дешифратор.

На фиг. 4 обозначено: а) импульс внешней синхронизации на входе 12;

б) импульс на выходе триггера 32 блока 10 управления; в) импульс на выходе триггера 31 блока 10 управления; г) импульсы на выходе генератора 29 блока 10 управления; д) импульсы на

выходах 42-45 блока 10 управления (на входах синхронизации АДП 2, сумматора 3 и входах 24 и 25 предсказателя 5 соответственно); и) сигнал на выходе т тиггера 33 (на входе 23

предсказателя 5); к) импульс на вхое синхронизации регистра 28 блока 10 управления; л) импульс на выходе- 6 блока.10 управления.(на входе синхронизации ЦАП 4); м), н) импуль(;ы с I . U onKn трштеров 32 н 31 блока 1 Г) упраплеиия .

Рлбога устройства для кодирования аналох опых сиг}шлов основана на известном методе кодирования с пред- сказанием, когда квантуется не сам входной сигнал, а разность между ним и его предсказанным значением. Код же входного сигнала получается в результате сложения кода предсказанно- го значения и кода этой разности - ошибки предсказания. Предсказание будет эффективным, если кодирование осуществляется с частотой, превьпиа- ющей частоту дискретизации по Котель никову, когда последователыгые отсчеты сигнала становятся коррелированными. В примере реализации устройства частота дискретизации 768 кГц, чт в шестнадцать раз превышает частоту 48 кГц, принятую в радиовещании.

Устройство работает следуюгцим образом.

Аналоговый звуковой сигнал поступает с входа 11 в вычитатель 1, где усиливается таким образом, чтобы использовалась вся шкала квантования и в то же время клиппирование сигнала было маловероятным. На другой вхо вычигателя 1 поступает значение пред сказанного сигнала, поэтому на выходе вычитателя 1 образуется сигнал ошибки предсказания, равный разности входного и предсказанного сигналов. Коэффициент усиления сигнала ошибки в вычитателе 1 определяется управляющим сигналом, поступающим с блока 1 управления. С выхода вычитателя 1 сигнал оп1ибки предсказания поступает на сигнальньш вход АЦП 2, импульс синхронизации которого вырабатьшает- ся блоком 10 управления. С приходом положительного фронта на вход 12 синхронизации первый и второй триггеры 31 и 32 блока 10 управления устанавливаются в нулевое состояние, так как на их Б-входах, присутствует уро- вень логического О. Уровень логической 1 с инверсного выхода триггера 32 переводит счетчик в распре- делителе 30 импульсов в режим прямого счета, а уровень логического О с выхода триггера 31 запускает генератор 29, которьй начинает вырабатывать прямоугольные тактовые импульсы в виде меандра с периодом «60 не, Положительнряй фронт первого тактового импульса генератора 29 формирует на выходе 42 блока 10 управления от

5 о - г

5

0

5

ринат ejii.Hbii i импульс синхронизации ЛИИ 2 в первом тактоном интервале. На выходах АЦП 2 появляется код, соответствующий значению аналогового сигнала ошибка. Этот код, представленный в виде знака сигнала ошибки (старший разряд АЦП 2) и кода величины ошибки (с шестого по первый разряд) поступает на информационные входы первого коммутатора 6. В зависимости от сигнала управления первый коммутатор 6 подключает код ошибки предсказания к шрсти младшим разрядам пеппых информа1 1ионных входов сумматора 3, либо сдвигает их влево на один, два, три разряда. На вторые информационные входы сумматора 3 подается с выходов предсказателя 5 код предсказанного значения входного сигнала. Таким образом, на выходах сумматора 3 вычисляется код истинного значения входного сигнала, который запоминается в сумматоре 3 по импульсу синхронизации с выхода 43 блока 10, который формируется с приходом третьего тактового импульса с генератора 29. Этот код в сумматоре 3 остается без изменения до прихода следующего импульса синхронизации. Необходимо отметить, что положительный фронт импульса синхронизации сумматора 3 задержан относительно положительного фронта синхроимпульса АЦП 2 на НС, что обеспечивает время, необходимое для срабатывания АЦП 2, ГУ 20 НС, сложения двух кодов в сумматоре 3 60 НС и прохождения кода через первый коммутатор 6 3 не, т.е. гарантирует правильность кода на выходе сумматора 3. Код с выхода сумматора 3 поступает на дециматор 9 и предсказатель 5. Первый и второй импульсы синхронизации предсказателя 5 формируются в блоке 10 управления на выходах 44 и 45 в течение четвертого и пятого тактовых импульсов аналогично импульсам синхронизации сумматора 3. Сигнал управления предсказателем 5 формируется третьим триггером 33 блока 10 управления (выход 41). Коммутаторы 20 и 21 предсказателя 5 рклюг)ены таким образом, что при подаче на их управляющие входы уровня логического О выходы ко -1мутаторов 20 и 21 подключаются к вторым входам, а при подаче логической 1 - к первым. Предсказатель 5 работает в соответствии со следующим выражением

У(пТ)Х(п-1),-Л,,

V(nT) - ИГ.1ХОДКОЙ сиг яал (код) в

момент времени пТ; ,2, . . . ,

Т - период дискретизации; Х(пТ) - входной сигнал (код);

4,ХГ(п-))(п-2) j-X(n-2)(n-3)T,

Код с выходов сумматора 3 поступает на рег истр 1А и сумматор 18, где складывается с инверсным значением кода предьщущего отсчета сигнала, т.е. определяется значение /а, и на коммутатор 21. Так как выходы этого коммутатора 21 подключены к его вторым входам (на его управляющем входе уровень логического О), код с выходов сумматора 3 поступает на вторые входы сумматора 19, на пер вьсх входах которого в этот момент имеется значение, подаваемое с инверсных выходов регистра 15 через коммутатор 20, Поэтому с приходом первого импульса синхронизации предсказателя 5 в регистр 16 записывается значение суммы хС(п-1 ), а в регистр 15 - код с выходов сумматора 18, равный ,3,Xt(n-l)(n-2)T. Одновременно с приходом первого синхроимпульса на управляющие входы коммутаторов 20 и 21, с входа 23 подается уровень логической- 1 и они подключают на свои выходы первые входы. Причем первые входы коммутатора 20 подключены к прямым выходам регистра 15 таким образом, что код с выхода регистра 15 сдвигается на оди разряд влево, т.е. осуществляется уменьшение его на два. Таким образом на первые входы сумматора 19 поступает код 2д,, а на его вторые входы - код частичной суммы X(n-l)TJ- и,с регистра 16. С приходом второго импульса синхронизации предсказателя 5 код с выхода сумматора 19, равный предсказанному значению последующего отсчета входного сигнала Y(nT) Х (п-1 )Т + 2 4 -4j, записьгеается в регистр 17. Одновременно вторым импульсом синхронизации код с выходов сумматора 3 записывается в регистр 1А предсказателя 5, так как он необходим для работы предсказателя 5 в следующем периоде- дискретизации. Кроме зтого код разности 4,. записанный в регистре 15, будет также использован в следующем периоде дискретизации как и,, так как снимается с инверсных выходов регистра 15.

1Л

После записи кода и регистр I7 предсказателя 5 он поступает на второй коммутатор 7и блок 10 упрап- ления. В соответствии с таблицей

истинности дешифратор 27 блока 10 управления формирует позиционный код управления, который поступает на вход регистра 28. По положительному фронту импульса синхронизации, пырабатываемому формирователем 36, в течение второй половины пятого тактового интервала, т.е. по отрицательному фронту пятого тактового импульса (см. фиг. 4к) код управления записывается

в регистр 28. Далее этот код сразу поступает с выходов 39 блока 10 на управляющее входы первого коммутатора 6 и второго коммутатора 7. Второй коммутатор 7 подключает ко входам

ЦАП 4 одиннадцать последовательных разрядов выходного кода предсказателя 5 или с 15 по 5, или с 14 по 4, или с 13 по 3, или с 12 по 2, т.е. таким образом, чтобы максимально использовать динамический диапазон ЦАП 4. На первый (старший) разряд ЦАП 4 подается независимо от кода управле- ния старший разряд кода с выхода . предсказателя 5, так как он является

знаковым. Первый коммутатор 6 также переключает выходы АЦП 2 к соответствующим входам сумматора 3. Одновременно код управления с выходов регистра 28 поступает на формирователь 34, который вырабатывает сигналы управления, необходимые для работы аттенюатора 8 и вычитателя 1. По положительному фронту шестого тактового импульса генератора 29 (см. фиг. 4 ) формирователь 36 вырабатьгоает импульс синхронизации ЦАП 4, по которому в него записывается код с соответствующих выходов коммутатора 7, Одновременно со второго выхода распределителя 30 импульсов отрицательный импульс подается на установочный вход второго триггера 32. В результате на выходе этого триггера 32 устанавливается уровень логического нуля,

который переводит счетчик в распределителе 30 в режим параллельной записи. Код с выходов коммутатора 7 преобразуется в ЦАП 4 в соответствующее ему напряжениеJ инвертированное относительно входного кода ЦАП 4 а, следовательно, и входного сигнала устройства. Выходное напряжение ЦАП 4 . подается на аттенюатор 8. На выходе аттенюатора 8 снимается напряжение

3

такое, чт(1бы восстановить амплитуду 11редск- заяниог(1 значения входного сигналя, искаженн то в результате коммутации сигнала на входе ЦАП А. ieo6xo димо отметить, что уменьшается на выходе аттенюатора 8 не только сам сигнал, но и ошибка, вносимая неточностью уровней ЦЛП А. Сигнал с выхода аттенюатора 8 поступает на второй вход вычитателя 1, в котором вырабатывается сигнал ошибки предсказания. С приходом седьмого тактового импульса с генератора 29 блока 10 управления формирователь 35 вырабатывает короткий положительный импульс, который устанавливает на выходе первого триггера 31 уровень логической единицы и останавливает генератор 29. С приходом очередного импульса синхронизации в блок 0 управления работа всего устройства повторится, как было описано вьше.

С выходов сумматора 3 коды отсчетов входного сигнала с частотой 768 кГц поступают на информационный вход дециматора 9, а на его вход синхронизации поступает сигнал внешней синхронизации с частотой 768 кГц Цифровой фильтр, включенный в состав дециматора 9, подавляет частотные составляющие, лежащие вне полосы полезного звукового сигнала (аналогично аналоговому фильтру нижних частот с полосой пропускания 0-20 кГц), а компрессор частоты дискретизации понижает частоту дискретизации до стандартной 48 кГц, пропуская на выходы дециматора 9 только каждый шестнадцатый код с выхода цифрового фильтра Таким образом на выходах дециматора 9 формируются коды отсчетов входного аналогового звукового сигнала с частотой 48 кГц, соответствующих шестнадцатиразрядному линейному кодированию.

Устройство для кодирования аналоговых сигналов, благодаря дополнительной обработке предсказанного значения входного сигнала с помощью второго коммутатора 7 и аттенюатора 8, управляемых блоком 10 управления, позволяет уменьшить шум, вноси п,1й неточностью ЦАП 4, более чем на 10- 14 дБ, А дополнительная обработка сигнала ошибки предсказания вычи- тателем 1 и первым коммутатором 6 позволяет сохранить условие незначительности шумов, вносимых АЦП 2.,Кроме этого, использование в петле об6091

рлтиой связи пррдскя ча- гля 3, пыпол- HfMiHci о по оригиианьиой схеме, дает вотможпость упеличигг. ч.чстсчу дискре- тнз-тции более --IRM п 16 рп: по срав- с иеиин) с принятой ;и)я кодирппакия зву- коных сигналов, что познолярт при использовании на выходе устройства дем;иматора 9 повысить точность кодирования еще па 12 дБ.

o

Формула изобретения

-1. Устройство для кодирова гия ана- логов.к сигналов, содержащее вычита15 тель, выход которого соединен с информационным входом аналого-цифрового преобразователя, цифроаналог овый преобразователь, сумматор, выходы которого подключены к соответствуюишм

0 информационным входам дециматора и предсказателя, выходы которого соединены с соответствуюпц1ми первыми входами су1-1матора, первый информационный вход вычитателя является ин5 формационным входом устройства, выходы дециматора являются выходами устройства, отличающееся тем, что, с целью гювьщзения точности кодирования, в устройство введены

30 коммутаторы, аттенюатор и блок уп- равлс1 ;я, первые выходы которого под- ключснь к соответствующим управляющим входам первог о и второго коммутаторов, выходы которых подключены со2 ответственно к вторым входам сумматора и информационным входам цифроана- логового преобразователя, выход которого соединен с информационным входом аттенюатора, вторые выходы блока уп0 равлепия подключены к управляющим

входам вычитателя и аттенюатора, вы- ход которого соединен с вторым информационным входом вычитателя, выходы аналого-цифрового преобразователя

45 подключены к информационным входам первого коммутатора, соответствующие информационные входы второго коммутатора и блока управления объединены и подключены к соответствующим выхоQ дам предсказателя, третий, четвертьй и пятый выходы блока управления соединены соответственно с управляющим входом и первым и вторым входами синхронизации предсказателя, шестой,

седьмой и восьмой выходы блока управления соединены с входами синхронизации соответственно цифроаналого- вого и аналого-цифрового преобразояа телей и сумматора, входы счпхрониза;..ии лгиипа op;) н блока yiipajs ичшн обьедияены и янляюгся входом сиихро (пг чиии устройства.

2, Ус 1 ройство по п. 1, о т л н ч а ю Dj е е с я тем, что, с целью Т1овьш1с ния быстродействия, предсказатель выполнен на регистрах, сумматорах и KOMMif TflTOpax, выходы первого регистра подключены к соответствующим nepBi.iH вход;лм первого сумматора, выходы которо о соединены с соответст- ВУ101ЦИМИ информационными входами второго регистра, первые и вторые выходы которого подключены к соответствующим информационным входам первого коммута тора, выходы первого и второго коммутаторов подключены к соответствующим входам второго сумматора, выходы которого соединены с соответствующими информационными входами третьего и четвертого регистров, выходы третьего регистра подключены к первым информационным входам второго коммутатора, вторые информационные входы которого объединены с соответствующими вторыми входами первого сумматора и информационными входами первого регистра и являются информационными входами предсказателя, управляющие входы коммутаторов объединены и являются управляющим входом предсказателя, входы синхронизации второго и третьего регистров и входы синхронизации первого и четвертого регистров соответственно объединены и являются первым и вторым входами синх- роиизаи/г и предсказателя ,, выходы четвертого регистра являются выходами предсказателя.

Qt1(1

. 1 ройс мю но п. I , о т л и - ч а ю |ц о е с я тем, что блок управления на регистре, генераторе, распределителе импульсов, формиронатедях импульсов, триггерах и дешифраторе, выход1 1 которого соединены с информационными входами регистра, выходы которого подключены к соответствующем входам первого формирователя импульсов, выходы первого и второго триггеров соединены соответственно со входом генератора и уп- paвляюuц м входом распределителя импульсов, первый и второй выходы которого соответственно через второй формирователь импульсов и непосредственно соединены с установочными входами первого и второго триггеров, выход 1-енератора подключен к входам

синхронизации третьего формирователя импульсов и распределителя импульсов, третьи выходы которого подключены к соответствующим установочным входам третьего триггера и соответствующим

управляющим входам третьего формирователя импульсов, первый выход которого соединен с входом синхронизации регистра, входы дешифратора являются информационными входами блока, входы

синхронизации первого и второго триггеров объединены и являются входом синхронизации блока, выходы регистра и первого формирователя импульсов яв- ЛЯ10ТСЯ соответственно первыми и вторыми выходами блока, выход третьего триггера и второй-шестой, выходы третьего формирователя импульсов являются соответственно третьим-восьмым выходами блока.

Ф1/г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| УСТРОЙСТВО ДЛЯ СЖАТИЯ ДАННЫХ (ВАРИАНТЫ) | 1994 |

|

RU2093957C1 |

| УСТРОЙСТВО ДЛЯ СЖАТИЯ ДАННЫХ (ВАРИАНТЫ) | 1994 |

|

RU2093958C1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1999 |

|

RU2173030C2 |

| УСТРОЙСТВО ЦИФРОВОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ТЕЛЕВИЗИОННОГО СИГНАЛА | 1992 |

|

RU2042282C1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

Изобретение относится к автоматике. Р го использование в системах дискретной передачи, например, звуковых сигналов позволяет повысить точность кодирования. Устройство содержит вычитатель 1, аналого-цифровой преобразователь (АЩ) 2, сумматор 3, цифроаналоговый преобразователь (ЦАП) 4, предсказатель 5 и дециматор 9. Введение коммутаторов 6 и 7, аттенюатора 8 и блока 10 управления обес- счивает снижение шумов, вносимых .ЦП 2 и LLAn 4, а специфическое выполнение предсказателя 5 позволяет повысить частоту дискретизации более чег в шестнадцать раз, что также по- ; ь:шает точность кодирования. 2 з.п. ф-лы, 4 ил, 1 табл. сл со о: о со

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1984 |

|

SU1197085A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 4318086, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| ГКЕЕ Transactions on Circuits N,-rJ Systems, 1978, v | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-06-07—Публикация

1985-12-13—Подача