Изобретение относится к измерительной технике и может быть исполь- зойано в злектро- и радиотехнике, в частности при измерении коэффициентов модуляции сигналов с амплитудной модуляцией.

Целью изобретения является повышение точности измерений..

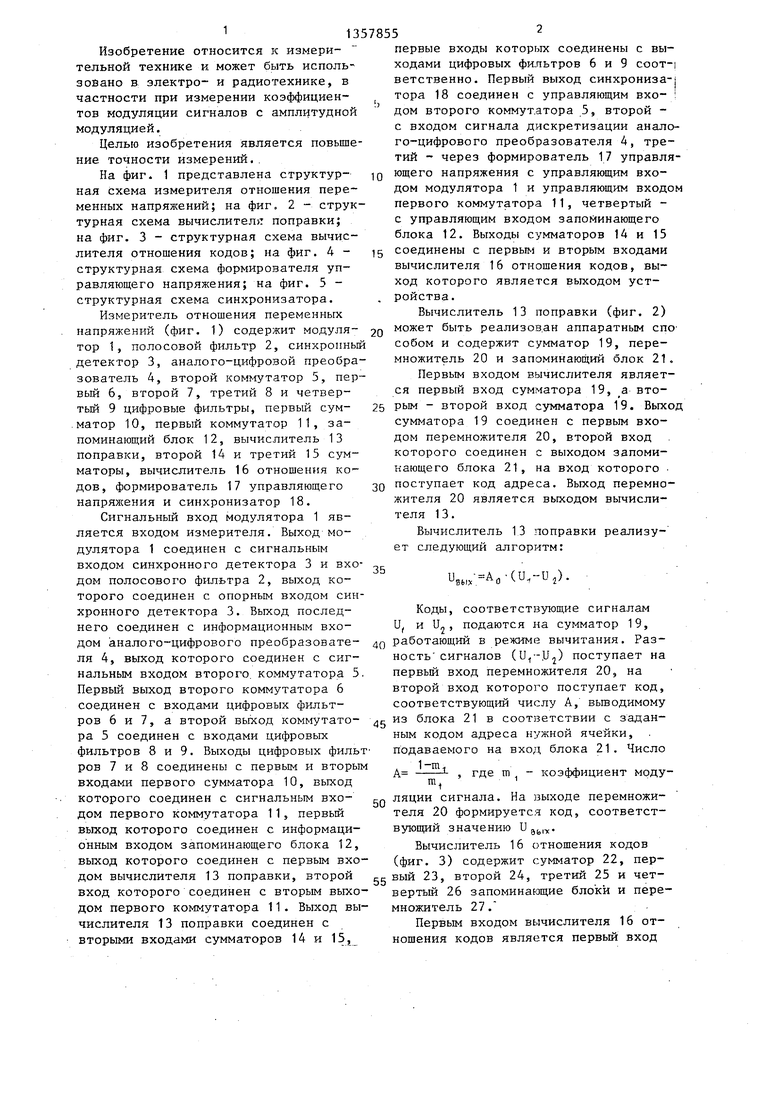

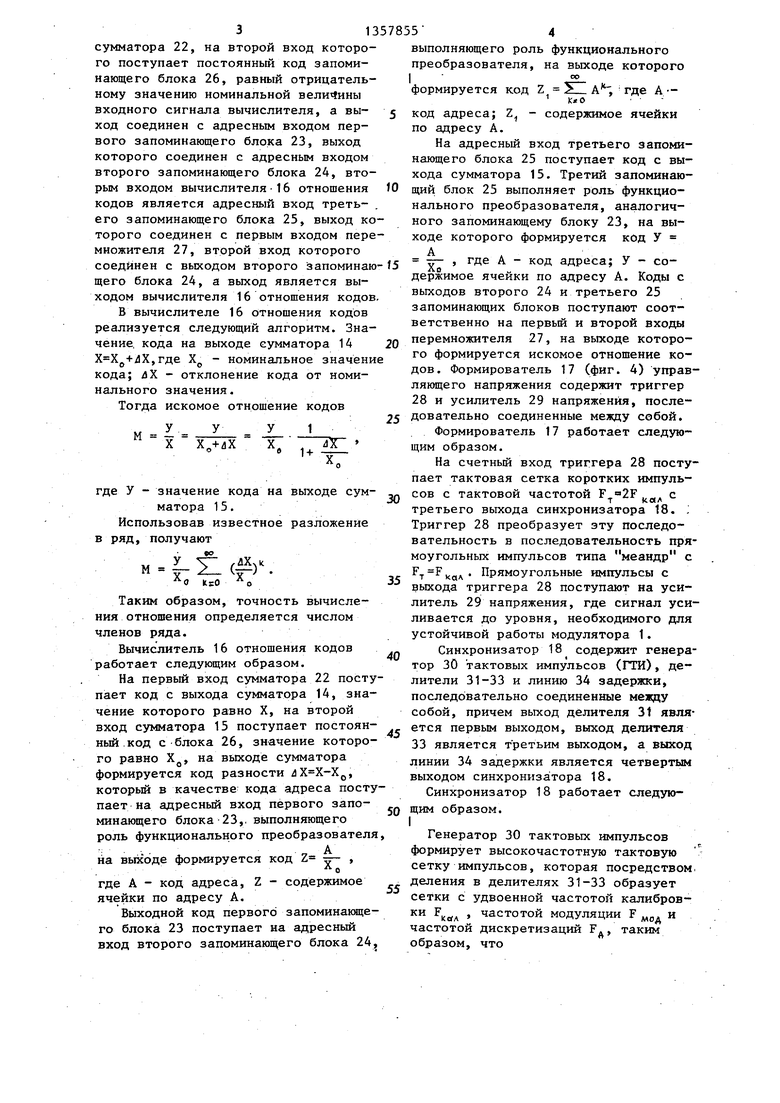

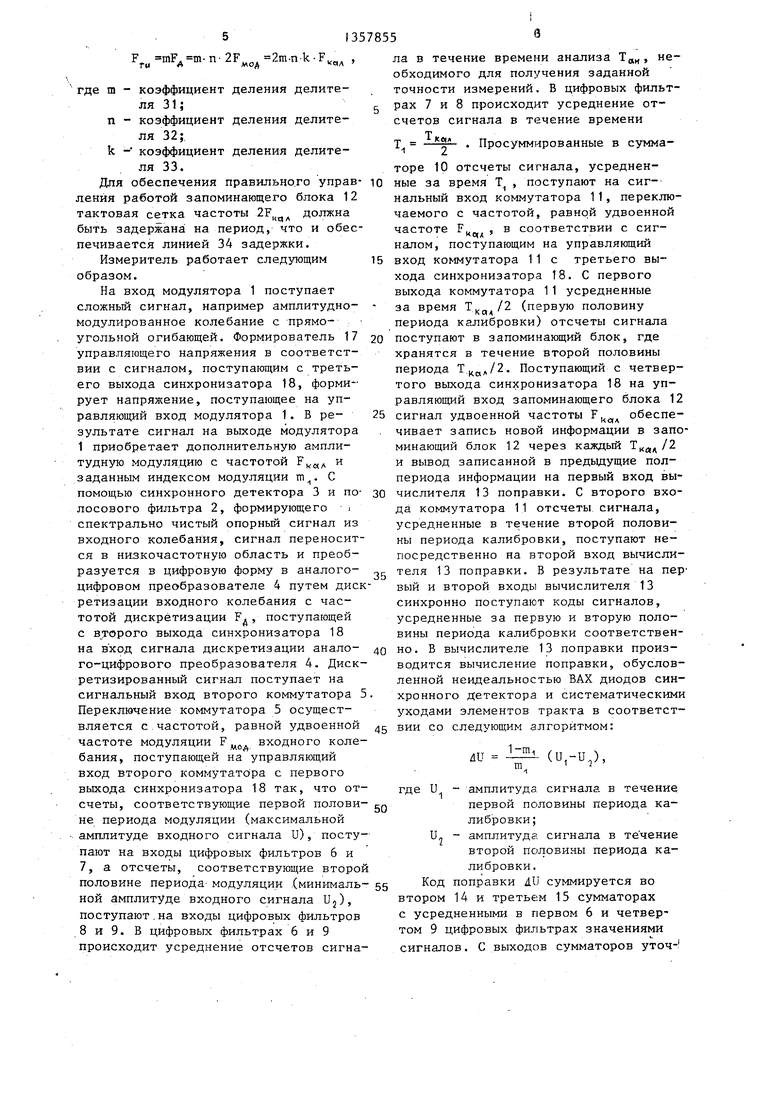

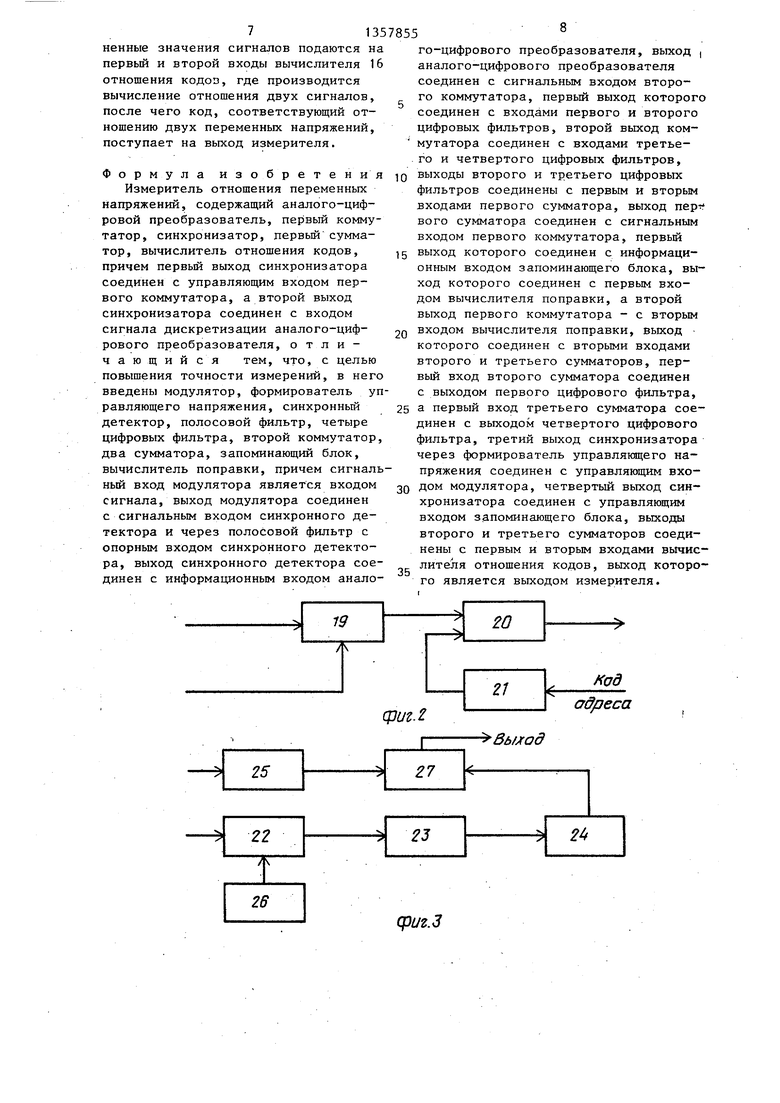

На фиг. 1 представлена структурная схема измерителя отношения переменных напряжений; на фиг, 2 - структурная схема вычислител : поправки; на фиг. 3 - структурная схема вычислителя отношения кодов; на фиг. 4 - структурная схема формирователя уп- равляюш:его напряжения; на фиг. 5 - структурная схема синхронизатора.

Измеритель отношения переменных напряжений (фиг. 1) содержит модулятор 1, полосовой фильтр 2, синхронный детектор 3, аналого-цифровой преобразователь 4, второй коммутатор 5, первый 6, второй 7, третий 8 и четвертый 9 цифровые фильтры, первый сум- матор 10, первый коммутатор 11, запоминающий блок 12, вычислитель 13 поправки, второй 14 и третий 15 сумматоры, вычислитель 16 отношения кодов, формирователь 17 управляющего напряжения и синхронизатор 18.

Сигнальный вход модулятора 1 является входом измерителя. Выход модулятора 1 соединен с сигнальным входом синхронного детектора 3 и входом полосового фильтра 2, выход которого соединен с опорным входом синхронного детектора 3. Выход последнего соединен с информационным входом аналого-цифрового преобразователя 4, выход которого соединен с сигнальным входом второго, коммутатора 5 Первый выход второго коммутатора 6 соединен с входами цифровых фильтров 6 и 7, а второй выход коммутатора 5 соединен с входами цифровых

фильтров В и 9. Выходы цифровых фИЛЬТ

ров 7 и 8 соединены с первым и вторьм входами первого сумматора 10, выход которого Соединен с сигнальным входом первого коммутатора 11, первый выход которого соединен с информационным входом запоминающего блока 12, выход которого соединен с первым входом вычислителя 13 поправки, второй вход которого соединен с вторым выходом первого коммутатора 11. Выход вычислителя 13 поправки соединен с вторыми входами сумматоров 14 и 15,

первые входы которых соединены с выходами цифровых фильтров 6 и 9 COOT-j

ветственно. Первый выход синхрониза-| тора 18 соединен с управляющим вхо- дом второго коммутатора 5, второй - с входом сигнала дискретизации аналого-цифрового преобразователя 4, третий - через формирователь 17 управляющего напряжения с управляющр1м входом модулятора 1 и управляющим входом первого коммутатора 11, четвертый - с управляющим входом запоминающего блока 12. Выходы сумматоров 14 и 15

соединены с первьм и вторым входами вычислителя 16 отношения кодов, выход которого является выходом устройства.

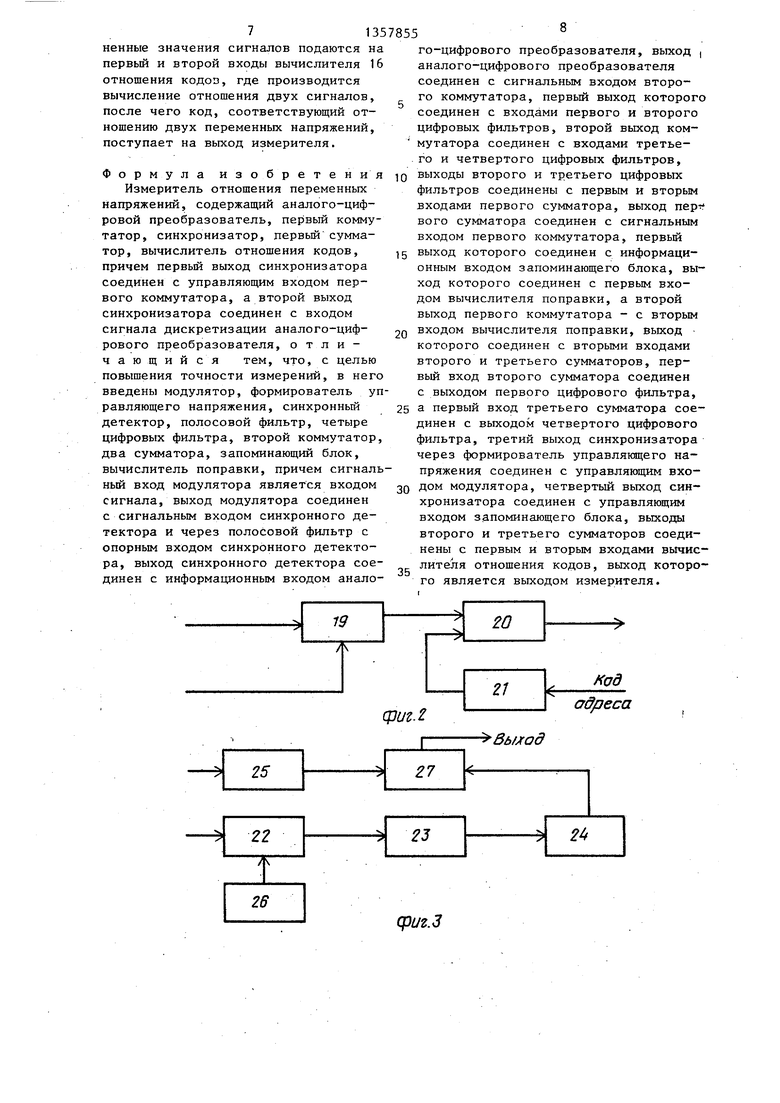

Вычислитель 13 поправки (фиг. 2) может быть реализов.ан аппаратным способом и содержит сумматор 19, перемножитель 20 и запоминающий блок 21. Первым входом вычислителя является первый вход сумматора 19, а вторым - второй вход сумматора 19. Выход сумматора 19 соединен с первым входом перемножителя 20, второй вход которого соединен с выходом запоминающего блока 21, на вход которого .

поступает код адреса. Выход перемножителя 20 является выходом вычислителя 1 3.

Вычислитель 13 поправки реализует следующий алгоритм:

5

0

5

ъш о

и,

(U,-Uj).

Коды, соответствующие сигналам и Uj, подаются на сумматор 19,

работающий в режиме вычитания. Разность сигналов () поступает на первый вход перемножителя 20, на второй вход которого поступает код, соответствующий числу А, вьшодимому из блока 21 в соответствии с заданным кодом адреса нужной ячейки, подаваемого на вход блока 21. Число

1-т,, ,

где m - коэффициент модуА

т.

ляции сигнала. На выходе перемножителя 20 формируется код, соответствующий значению и,.

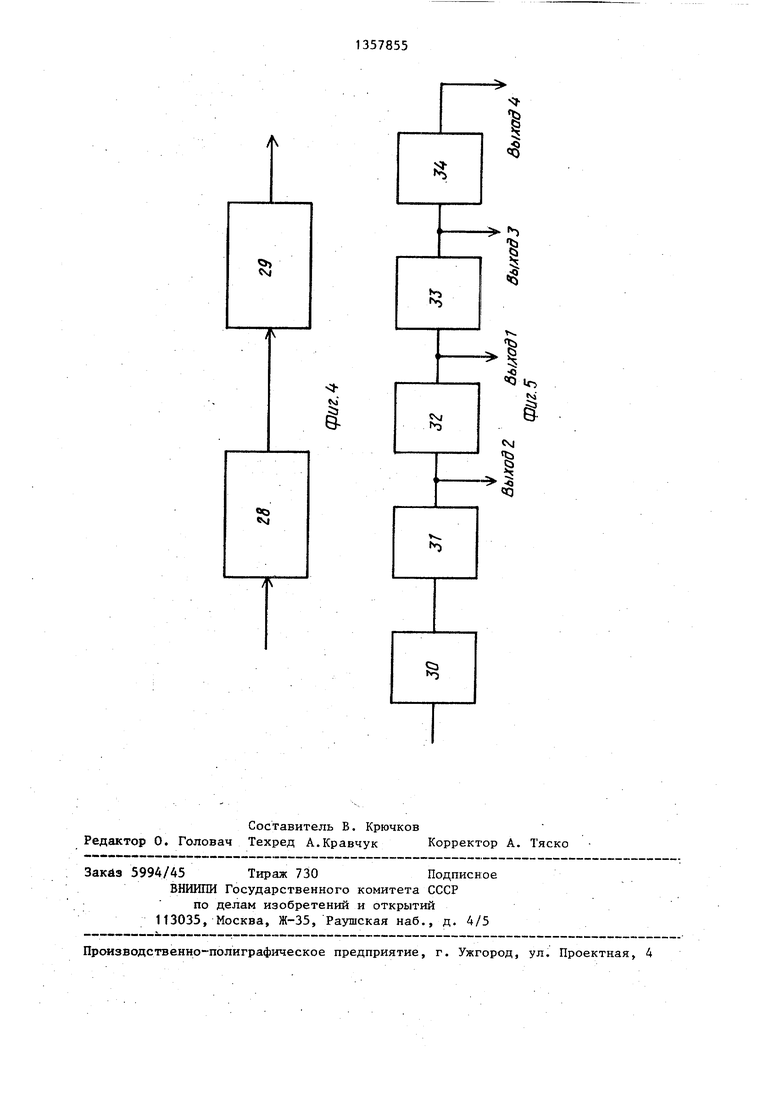

Вычислитель 16 отношения кодов (фиг. 3) содержит сумматор 22, первый 23, второй 24, третий 25 и чет- вертьш 26 запоминающие блоки и перемножитель 27.

Первьм входом вычислителя 16 отношения кодов является первый вход

сумматора 22, на второй вход которого поступает постоянный код запоминающего блока 26, равный отрицательному значению номинальной величины входного сигнала вычислителя, а вы- ход соединен с адресным входом первого запоминающего блока 23, выход которого соединен с адресным входом второго запоминающего блока 24, вторым входом вычислителя16 отношения кодов является адресный вход третьего запоминающего блока 25, выход которого соединен с первым входом перемножителя 27, второй вход которого соединен с выходом второго запоминающего блока 24, а выход является выходом вычислителя 16 отношения кодов.

В вычислителе 16 отношения кодов реализуется следующий алгоритм. Значение, кода на выходе сумматора 14 ,где Хр - номинальное значение кода; 4Х - отклонение кода от номинального значения.

Тогда искомое отношение кодов

- X

X +dX

у

X,

1

1 +

лх х„

е У - значение кода на выходе сумматора 15.

Использовав известное разложение ряд, получают

90

« г

Л-0

КсО

С-)

о

Таким образом, точность вычисления отношения определяется числом членов ряда.

Вычис литель 16 отношения кодов работает следующим образом.

На первый вход сумматора 22 поступает код с выхода сумматора 14, значение которого равно X, на второй вход сумматора 15 поступает постоянный код с блока 26, значение которого равно X , на вькоде сумматора формируется код разности , который в качестве кода адреса поступает на адресный вход первого запо- минакицего блока-23,. выполняющего роль функционального преобразователя

-А

на вых оде формируется код Z TJ- ,

° где А - код адреса, Z - содержимое

ячейки по адресу А.

Выходной код первого запоминакнце- го блока 23 поступает на адресный вход второго запоминающего блока 24,

O 5

0

5

0

выполняющего роль функционального преобразователя, на выходе которого I °о

формируется код Z А Ч где А

код адреса; Z - содержимое ячейки по адресу А.

На адресный вход третьего запоминающего блока 25 поступает код с выхода сумматора 15. Третий запоминающий блок 25 выполняет роль функционального преобразователя, аналогичного запоминающему блоку 23, на выходе которого формируется код У

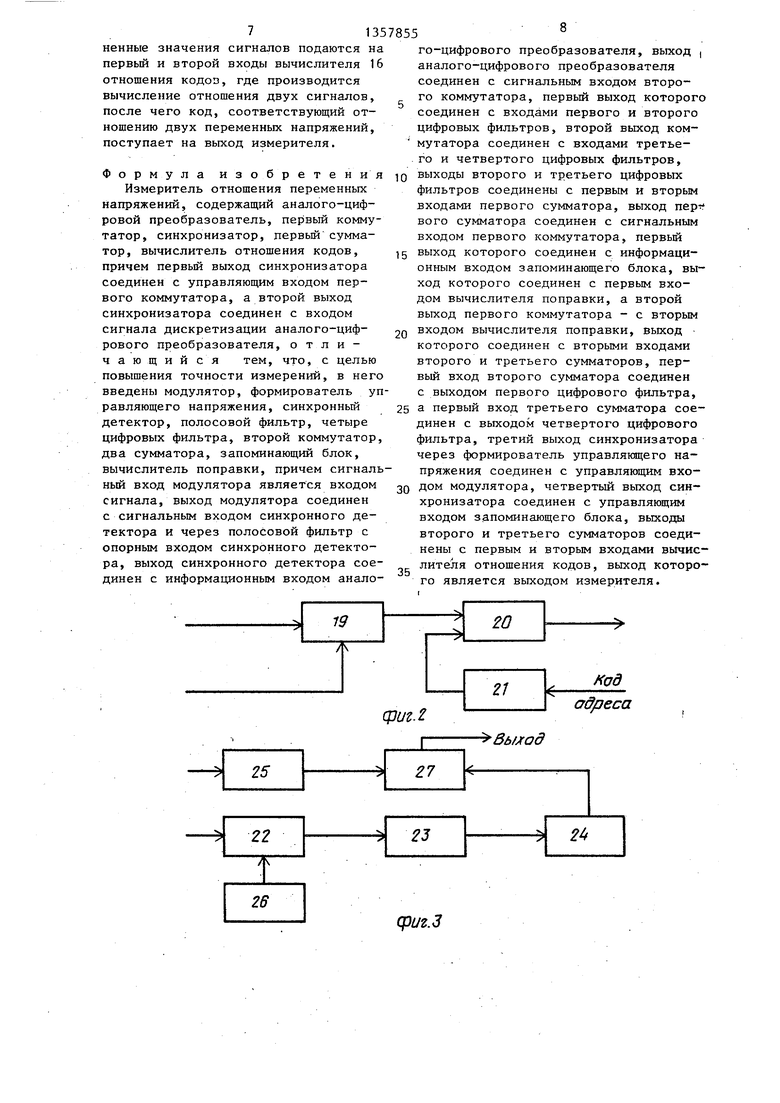

- , где А - код адреса; У - содержимое ячейки по адресу А. Коды с выходов второго 24 и третьего 25 запоминающих блоков поступают соответственно на первый и второй входы перемножителя 27, на выходе которого формируется искомое отношение кодов. Формирователь 17 (фиг. 4) управ- лякнцего напряжения содержит триггер 28 и усилитель 29 напряжения, последовательно соединенные между собой.

Формирователь 17 работает следующим образом.

На счетный вход триггера 28 поступает тактовая сетка коротких импульсов с тактовой частотой F,2F.,. с

т К« А

третьего выхода синхронизатора 18. . Триггер 28 преобразует эту последовательность в последовательность прямоугольных импульсов типа меандр с

F F т кал

Прямоугольные импульсы с выхода триггера 28 поступают на усилитель 29 напряжения, где сигнал усиливается до уровня, необходимого для устойчивой работы модулятора 1.

Синхронизатор 18 содержит генератор 30 тактовых импульсов (ГТИ), делители 31-33 и линию 34 задержки, последовательно соединенные мезвду собой, причем выход делителя 31 является первым выходом, выход делителя 33 является третьим выходом, а выход линии 34 задержки является четвертым выходом синхрониза тора 18.

Синхронизатор 18 работает следующим образом. I

Генератор 30 тактовых импульсов формирует высокочастотную тактовую сетку импульсов, которая посредством, деления в делителях 31-33 образует сетки с удвоенной частотой калибровки FIJ , частотой модуляции F д. и частотой дискретизаций F, таким образом, что

ru

тГд m. n- 2F 2m.n-k F

где m - коэффициент деления делителя 3 1 ; n - коэффициент деления делителя 32;

k - коэффициент деления делителя 33.

Для обеспечения правильного управ- ленйя работой запоминающего блока 12 тактовая сетка частоты 2F. должна

К ц л быть задержана на период, что и обеспечивается линией 34 задержки.

Измеритель работает следующим образом.

На вход модулятора 1 поступает сложный сигнал, например амплитудно- модулированное колебание с прямоугольной огибающей. Формирователь 17 управляющего напряжения в соответствии с сигналом, поступающим с третьего выхода синхронизатора 18, формирует напряжение, поступающее на управляющий вход модулятора 1. В ре- зультате сигнал на выходе модулятора 1 приобретает дополнительную амплитудную модуляцию с частотой F и заданным индексом модуляции го. С помощью синхронного детектора 3 и по- лосового фильтра 2, формирующего i спектрально чистый опорный сигнал из входного колебания, сигнал переносится в низкочастотную область и преобразуется в цифровую форму в аналого- цифровом преобразователе 4 путем дискретизации входного колебания с частотой дискретизации F, поступающей с второго выхода синхронизатора 18 на вход сигнала дискретизации анало- го-цифрового преобразователя 4. Диск- ретизированный сигнал поступает на сигнальный вход второго коммутатора 5 Переключение коммутатора 5 осуществляется с.частотой, равной удвоенной

частоте модуляции F входного колебания, поступающей на управляющий вход второго коммутатора с первого выхода синхронизатора 18 так, что от

не периода модуляции (максимальной амплитуде входного сигнала U), поступают на входы цифровых фильтров 6 и 7, а отсчеты, соответствующие второй половине периода- модуляции .(минималь- ной амплитуде входного сигнала Uj), поступают.на входы цифровых фильтров 8 и 9. В цифровых фильтрах 6 и 9 происходит усреднение отсчетов сигна357855Й

, ла в течение времени анализа T

не

5 о 0

5

5

обходимого для получения заданной точности измерений. В цифровых фильтрах 7 и 8 происходит усреднение отсчетов сигнала в течение времени

Т

Т - Просуммированные в сумматоре 10 отсчеты сигнала, усредненные за время Т , поступают на сигнальный вход коммутатора 11, переключаемого с частотой, равной удвоенной частоте F , в соответствии с сигналом, поступающим на управляющий вход коммутатора 11 с третьего выхода синхронизатора 18. С первого выхода коммутатора 11 усредненные за время (первую половину периода калибровки) отсчеты сигнала поступают в запоминающий блок, где хранятся в течение второй половины периода (/2. Поступающий с четвертого выхода синхронизатора 18 на управляющий вход запоминающего блока 12 сигнал удвоенной частоты F обеспечивает запись новой информации в запоминающий блок 12 через каждый и вывод записанной в предыдущие полпериода информации на первый вход вычислителя 13 поправки. С второго входа коммутатора 11 отсчеты сигнала, усредненные в течение второй половины периода калибровки, поступают непосредственно на второй вход вычислителя 13 поправки. В результате на первый и второй входы вычислителя 13 синхронно поступают коды сигналов, усредненные за первую и вторую половины периода калибровки соответственно. В вычислителе 13 поправки производится вычисление поправки, обусловленной неидеальностью ВАХ диодов синхронного детектора и систематическими уходами элементов тракта в соответствии со следующим алгоритмом:

ли

1 -т

тп

(uru,).

0

5

1

и, где и - амплитуда, сигнала в течение первой половины периода калибровки;

амплитуда сигнала в течение второй половилчы периода калибровки.

Код поправки J.U суммируется во втором 14 и третьем 15 сумматорах с усредненными в первом 6 и четвертом 9 цифровых фильтрах значениями сигналов. С выходов сумматоров уточненные значения сигналов подаются на первый и второй входы вычислителя 16 отношения кодов, где производится вычисление отношения двух сигналов, после чего код, соответствующий отношению двух переменных напряжений, поступает на выход измерителя.

Формула изобретения

Измеритель отношения переменных напряжений, содержащий аналого-цифровой преобразователь, первый коммутатор, синхронизатор, первый сумматор, вычислитель отношения кодов, причем первый выход синхронизатора соединен с управляющим входом первого коммутатора, а второй выход синхронизатора соединен с входом сигнала дискретизации аналого-цифрового преобразователя, отличающийся тем, что, с целью повышения точности измерений, в него введены модулятор, формирователь управляющего напряжения, синхронный детектор, полосовой фильтр, четыре цифровых фильтра, второй коммутатор, два сумматора, запоминающий блок, вычислитель поправки, причем сигнальный вход модулятора является входом сигнала, выход модулятора соединен с сигнальным входом синхронного детектора и через полосовой фильтр с опорным входом синхронного детектора, выход синхронного детектора соединен с информационным входом анало

го-цифрового преобразователя, выход | аналого-цифрового преобразователя соединен с сигнальным входом второго коммутатора, первый выход которого соединен с входами первого и второго цифровых фильтров, второй выход коммутатора соединен с входами третьего и четвертого цифровых фильтров, выходы второго и третьего цифровых фильтров соединены с первым и вторым входами первого сумматора, выход перч вого сумматора соединен с сигнальным входом первого коммутатора, первый выход которого соединен с информационным входом запоминающего блока, выход которого соединен с первым входом вычислителя поправки, а второй выход первого коммутатора - с вторым входом вычислителя поправки, выход которого соединен с вторыми входами второго и третьего сумматоров, первый вход второго сумматора соединен с выходом первого цифрового фильтра, а первый вход третьего сумматора соединен с выходом четвертого цифрового фильтра, третий выход синхронизатора через формирователь управляющего напряжения соединен с управляющим входом модулятора, четвертый выход синхронизатора соединен с управляющим входом запоминающего блока, выходы второго и третьего сумматоров соединены с первым и вторым входами вычислителя отношения кодов, выход которого является выходом измерителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель отношения переменных напряжений | 1985 |

|

SU1307359A1 |

| Измеритель сдвига фаз | 1986 |

|

SU1366966A1 |

| Система связи | 1989 |

|

SU1815802A1 |

| Широкополосная система связи | 1985 |

|

SU1401625A1 |

| Цифровой анализатор спектра | 1990 |

|

SU1777096A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СТАНЦИЯ СОПРОВОЖДЕНИЯ ЦЕЛИ | 1997 |

|

RU2114444C1 |

| Измеритель сдвига фаз (его варианты) | 1982 |

|

SU1040432A1 |

| Система связи с относительной фазовой и фазоимпульсной модуляцией | 1987 |

|

SU1559421A1 |

| Устройство для обнаружения сигналов и измерения их параметров | 1987 |

|

SU1478145A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

Изобретение может быть использовано при измерении коэффициентов модуляции сигналов с амплитудной модуляцией. Цель изобретения - повышение точности измерения. Измеритель содержит аналого-цифровой преобразователь 4, коммутатор 11, сумматор 15, вычислитель 16 отношения кодов и синхронизатор 18. Для достижения цели в измеритель введены модулятор 1, полосовой фильтр 2, синхронный детектор 3, коммутатор 5, цифровые фильтры 6-9, сумматоры 10, 14 и 15, запоминающий блок 12, вычислитель 13 поправки, формирователь 17 управляющего напряжения в измерителе образованы новые функциональные связи. 5 ил. со ел 00 ел ел f/e.f

Вь/лод

Сриг.З

«vj

Л

м

op

Nj

Составитель В. Крючков Редактор О. Головач Техред А.Кравчук Корректор А. Тяско

Закйз 5994/45 Тираж 730Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| ИЗМЕРИТЕЛЬ ОТНОШЕНИЙ ЭЛЕКТРИЧЕСКИХ ИМПУЛЬСОВ | 0 |

|

SU351169A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Автоматический измеритель напряжения | 1972 |

|

SU611155A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Измеритель отношения переменных напряжений | 1977 |

|

SU742810A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-12-07—Публикация

1986-02-05—Подача