1

Изобретение относится к технике спектрального анализа.

Целью изобретения является повышение достоверности обнаружения сигнала .

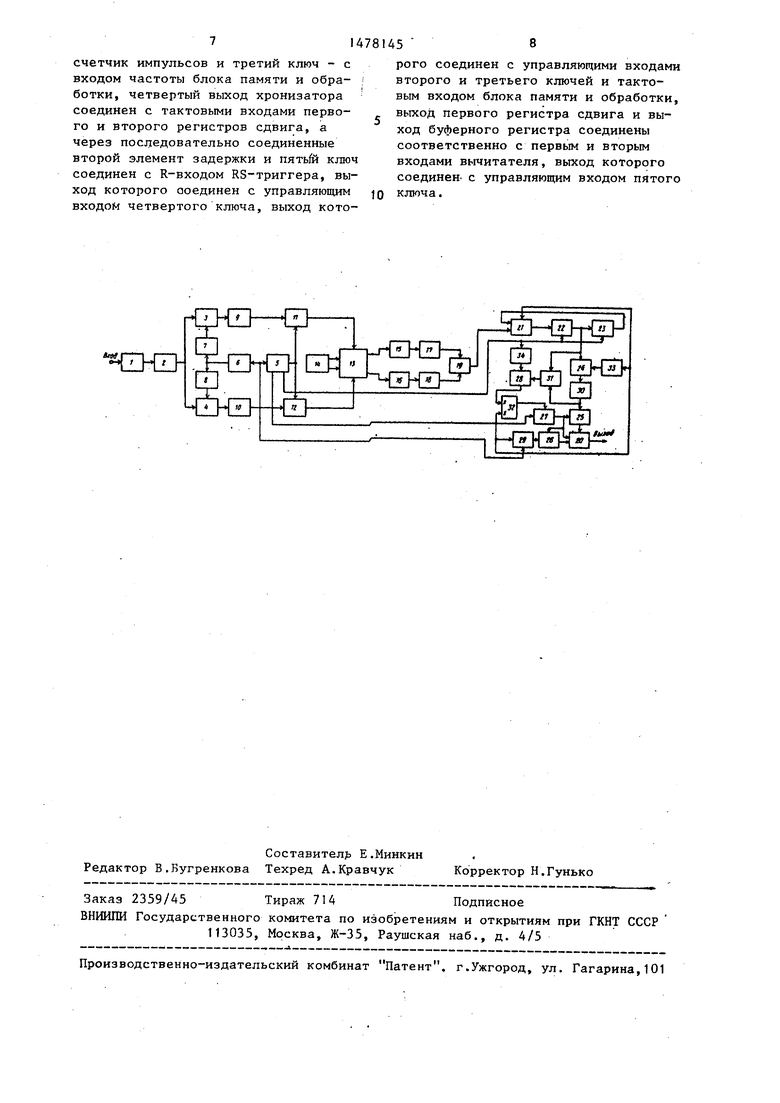

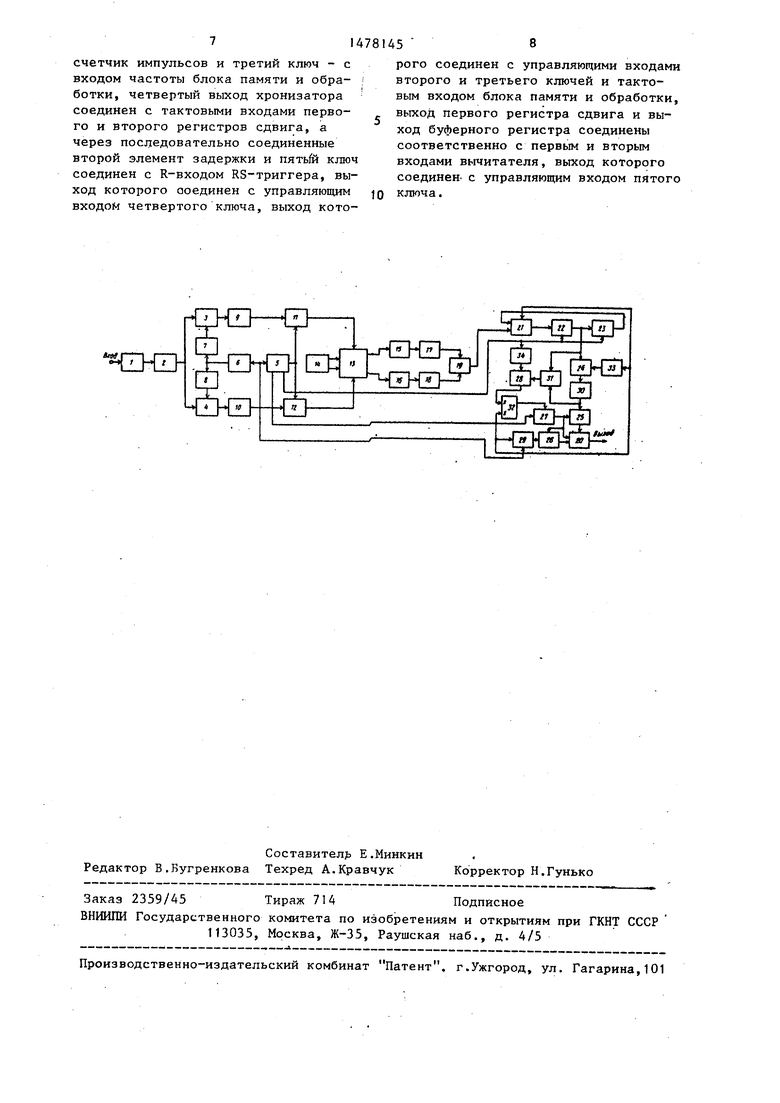

На чертеже показана функциональная, схема устройства.

Устройство содержит полосовой фильтр 1, аналого-цифровой преобразователь 2, первый и второй перёмно- жители 3 и 4, хронизатор 5, генератор 6 кода фазы, первый и второй преобразователи 7 и 8 кода фазы, первый и второй фильтры 9 и 10 нижних частот, первый и второй оперативные запоминающие блоки 11 и 12, перемножитель 13 комплексных сигналов, постоянный запоминающий блок 14, первый и второй накапливающие сумматоры 15 и 16, первый и второй блоки 17 и 18 возведения в квадрат, сумматор 19, блок 20 памяти и обработки, коммутатор 21, два регистра 22 и 23 - сдвига, пять ключей 24 - 28, счетчик 29 импульсов, буферный регистр 30, вычитатель 31, RS-триггер 32 и два элемента 33 и 34 задержки.

Выход полосового фильтра 1 соединен с входом аналого-цифрового преобразователя 2, выход которого соеди- нен с первыми входами первого и второго перемножителей 3 и4, первый

4

00

4Ь СП

вход хронизатора 5 соединен с входом генератора 6 кода фазы, выход которого через первый преобразователь 7 кода фазы соединен с вторым входом первого перемножителя 3 и через второй преобразователь 8 кода фазы соединен с вторым входом второго перемножителя 4, выходы первого и второго перемножителей 3-й 4 через фильтры 9 и Ю нижних частот соединены с входами первого и второго оперативных запоминающих блоков 11 и 12, тактовые входы которых соединены с вторым выходом хронизатора 5, выходы первого и второго оперативных запоминающих блоков 11 и 12 соединены с первыми входами перемножителя 13 комплексных сигналов, вторые входы которого соединены с выходами постоянного запоминающего блока 14, каждый из выходов перемножителя I3 комплексных сигналов через последовательно соединенные накапливающий сумматор 15 (16) и блок 17 (18) возведения в квадрат соединен с соответствующим входом сумматора 19, выход которого соединен с первым входом коммутатора 21. Второй вход коммутато-- ра 21 соединен с его выходом через два последовательно включенных регистра 22 и 23 сдвига, выход первого группового регистра 22 сдвига через последовательно включенные первы ключ 24, буферный регистр 30 и второй ключ 25 соединен с входом уровня блока 20 памяти и обработки. Первый выход хронизатора 5 соединен с входом сброса счетчика 29 импульсов, третий выход хронизатора 5 соединен непосредственно с S-входом RS-триг- гера, входом четвертого ключа 27, управляющим входом коммутатора 21, через первый элемент 33 задержки - с управляющим входом первого ключа 24 и через последовательно соединенные счетчик 29 импульсов и третий ключ 26 - с входом частоты блока 20 памяти и обработки, четвертый ключ 26 - с входом частоты блока 20 памяти и обработки, четвертый выход хронизатора 5 соединен непосредственно с тактовыми входами первого и второго регистров 22 и 23 сдвига и через последовательно соединенные второй элемент 34 задержки и пятый ключ 28 соединен с R-входом RS-триггера 32, выход которого соединен с управляющим входом четвертого ключа 27, вы0

5

0

5

0

5

0

5

0

5

ход которого соединен с управляющими входами второго 25 и третьего 26 ключей и тактовым входом блока 20 памяти и обработки, вхыод первого регистра 22 сдвига и выход буферного регистра 30 соединены соответственно с первым и вторым входами вычитате- ля 31, выход которого соединен с управляющим входом пятого ключа 28.

Устройство работает следующим образом.

После предварительной фильтрации сигнала полосовым фильтром I и перевода его в цифровую форму аналого- цифровым преобразователем 2 вычисляется его дискретный спектр, для чего сначала сигнал при помощи генератора 6 кода фазы, преобразователей 7 и 8 кода фазы, перемножителей 3 и 4 и фильтров 9 и 10 нижних частот преобразуется в импульс с ЛЧМ-заполнени- ем,а затем в согласованном фильтре, состоящем из двух оперативных запоминающих блоков 11 и 12, перемножителя 13 комплексных сигналов и двух на - капливающих сумматоров 15 и 16 вычисляется свертка ЛЧМ-импульса с импульсной характеристикой согласованного фильтра, записанной в постоянном запоминающем блоке 14. Блоки 17 и 18 и сумматор 19 вычисляют мощность спектральных составляющих сигнала .

Спектральные отсчеты с выхода сумматора 19 через коммутатор 21 поступают на вход первого регистра 22 сдвига, а с его выхода на вход второго регистра 23 сдвига. Между поступлением двух спектральных отсчетов производится рециркуляция отсчетов, содержащихся в регистрах 22 и 23, и сравнение их при помощи вычитателя 31 с отсчетом с выхода регистра 22, переписанным предварительно через ключ 24 в буферный регистр 30. Если ни один из отсчетов, записанных в регистрах 22 и 23, не превысил отсчета, находящегося в буферном регистре 30, ключ 28 останется закрытым, RS-триггер 32 останется в исходном состоянии и тактовый сигнал выхода хронизатора 5 пройдет через ключ 27, обеспечив перезапись спектрального отсчета из буферного регистра 30 и соответствующего этому отсчету значения кода частоты из счетчика 29 (через ключи 25 и 26 соответ51

ственно) в блок 20 памяти и обработки .

Если хотя бы один из отсчетов, находящихся в регистрах 22 и 23, во время рециркуляции превысит отсвет, находящийся в буферном регистре 30, то сигнал с выхода вычитателя 31 откроет ключ 28 и RS-триггер 32 перейдет в состояние, закрывающее ключ 27. При этом перезапись спектрального отсчета из буферного регистра 30 и соответствующего ему значения кода частоты из счетчика 29 в блок памяти и обработки произведена не будет. После поступления очередного спектрального отсчета с выхода сумматора 19 процедура рециркуляции и сравнения повторяется. Хронизатор . 5 обеспечивает также тактирование генератора 6 кода фазы, первого и второго оперативных запоминающих блоков 11 и 12, счетчика 29 импульсов, первого и второго многоразрядных регистров 22 и 23 сдвига, запись очередного отсчета с выхода -сумматора 19 через коммутатор 21 в многоразрядный регистр -сдвига 22, сброс счетчика 29, установку RS-триггера 32 в исходное состояние и перезапись отсчета с выхода регистра 22 в буферный регистр 30. Элементы 33 и 34 задержки служат для того, чтобы перезапись отсчетов происходила в установившемся режиме.

I

Положительный эффект от предлагаемого устройства достигается за счет того, что в блок 20 памяти и обработки будут поступать не все спектральные отсчеты, превышающие заданный порог, а лишь отсчеты, являющиеся локальными максимумами в частотной окрестности

uf vn. т-1,

п - скорость перестройки частоты на выходе преобразователей 7 и 8 кода фазы;

Т - период поступления отсчетов с выхода сумматора 19;

1 - длина регистров 22 и 23 сдвига.

Формула изобретения

Устройство для обнаружения сигналов и измерения их параметров, содержащее полосовой фильтр, вход которо-.

781456

го является входом устройства, а выход соединен с входом аналого-цифрового преобразователя выход которого соединен с первыми входами первого и второго перемножителей, первый выход хронизатора соединен с входом генератора кода фазы, выход которого через первый преобразователь коЮ да фазы соединен с вторым входом первого перемножителя, а через второй преобразователь кода фазы соединен с вторым входом второго перемножителя, выходы первого и второго пе15 ремножителей через первый и второй фильтры нижних частот соответственно соединены с входами первого и второго оперативных запоминающих блоков, тактовые входы которых соедине20 ны с вторым выходом хронизатора, выходы первого и второго оперативных запоминающих блоков соединены соответственно с первыми и вторыми входами перемножителя . комплексных сиг25 налов, третий и четвертый входы которого соединены с выходами постоянного запоминающего блока, первый и второй выходы перемножителя комплексных сигналов через последова30 тельно соединенные накапливающий сумматор и блок возведения в квадрат соответственно соединены с входами сумматора, а также блок памяти и обработки, выход которого является

25 выходом устройства, о т л и ч а го- ид е е с я тем, что, с целью повышения достоверности обнаружения сигналов, в него введены коммутатор, два регистра сдвига, пять ключей, счет40 чик импульсов, буферный регистр, вычитатель, RS-триггер и два элемента задержки, причем выход сумматора соединен с первым входом коммутатора, выход которого через два по45 следовательно соединенных регистра сдвига соединен с вторым входом коммутатора, выход первого регистра сдвига через последовательно соединенные первый ключ, буферный регистр 0 и второй ключ соединен с входом уровня блока памяти и обработки, первый выход хронизатора соединен с входом сброса счетчика импульсов, третий выход хронизатора соединен с S-входом

5 RS-триггера, входом четвертого ключа, управляющим входом коммутатора, через первый элемент задержки - с управляющим входом первого ключа и через последовательно соединенные

счетчик импульсов и третий ключ - с входом частоты блока памяти и обработки, четвертый выход хронизатора соединен с тактовыми входами первого и второго регистров сдвига, а через последовательно соединенные второй элемент задержки и пять/и ключ соединен с R-входом КЗ-триггера, выход которого соединен с управляющим входом четвертого ключа, выход кото

рого соединен с управляющими входами второго и третьего ключей и тактовым входом блока памяти и обработки, выход первого регистра сдвига и выход буферного регистра соединены соответственно с первым и вторым входами вычитателя, выход которого соединен с управляющим входом пятого ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи телеметрической информации | 1983 |

|

SU1129641A1 |

| Устройство обнаружения сигналови изМЕРЕНия иХ пАРАМЕТРОВ | 1979 |

|

SU830251A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Анализатор сигнала тактовой синхронизации | 1990 |

|

SU1781834A2 |

| Устройство для сжатия и передачи информации | 1988 |

|

SU1515183A1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1103275A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

Изобретение относится к анализаторам спектра. Цель изобретения - повышение достоверности обнаружения сигналов. Для достижения цели в устройство для обнаружения сигналов и измерения их параметров введены коммутатор, два регистры сдвига, пять ключей, счетчик импульсов, буферный регистр, вычитатель, RS - триггер и два элемента задержки. Устройство также содержит полосовой фильтр, аналого-цифровой преобразователь, два перемножителя, хронизатор, генератор кода фазы, два преобразователя кода фазы, два фильтра нижних частот, два оперативных запоминающих блока, перемножитель комплексных сигналов, постоянный запоминающий блок, два накапливающих сумматора, два блока возведения в квадрат, сумматор, блок памяти и обработки. Устройство обнаружения сигналов и измерения их параметров может быть использовано в многоканальных приемных системах со случайным доступом для обнаружения нескольких сигналов с неизвестными частотой и амплитудой на фоне шума и широкополосных помех. 1 ил.

nt

| Устройство обнаружения сигнала и определения его частоты | 1978 |

|

SU742818A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство обнаружения сигналови изМЕРЕНия иХ пАРАМЕТРОВ | 1979 |

|

SU830251A1 |

Авторы

Даты

1989-05-07—Публикация

1987-02-12—Подача