|оо

4 О 00

СЛ

Изобретение относится к области вычислительной техники и предназначено для непрерывного отсчета астрономического времени (функция час), для фиксации заранее заданного момента времени (функция компаратор), для измерения истекшего времени работы процессора (функция таймер процессора) и для формирования продвигающих импульсов с заданной частотой следования, предназначенных для продвижения интервального таймера, и может быть применено в ЭВМ любого класса, например, в ЕС ЭВМ, а также в мультипроцессорных системах.

Цель изобретения - расширение области применения устройства за счет синхронизации часов в мультипроцессорных системах и повышение точности формирования временных интервалов продвижения интервального таймера,

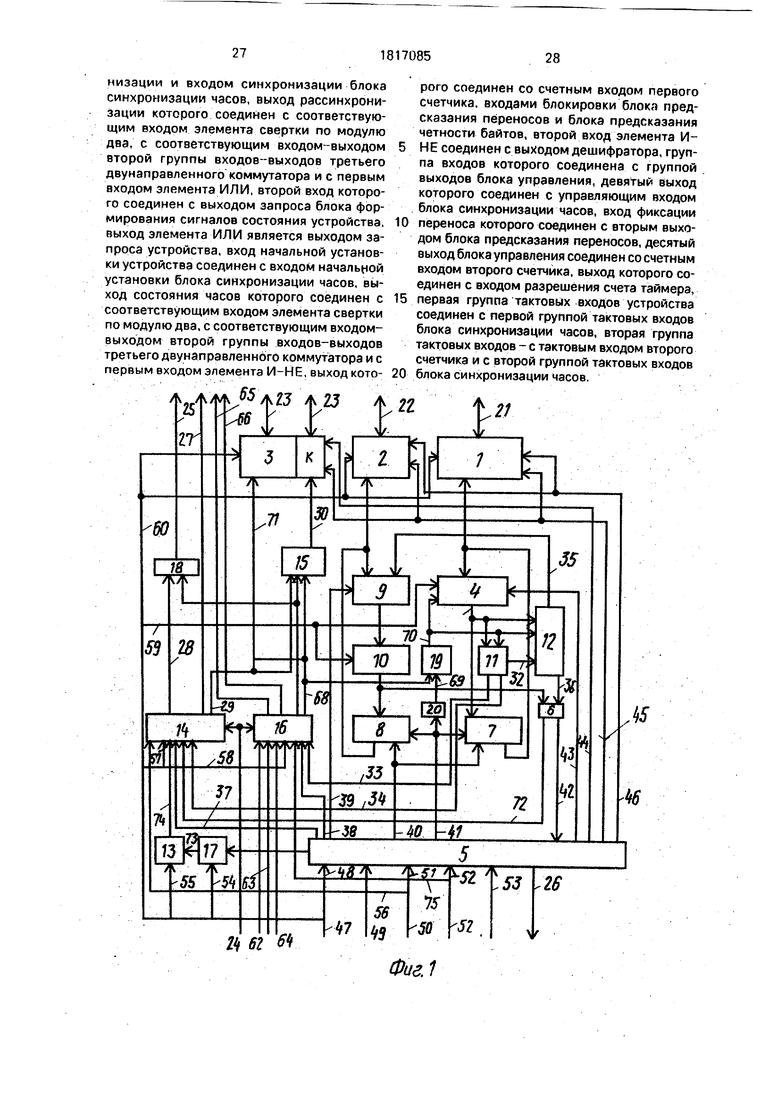

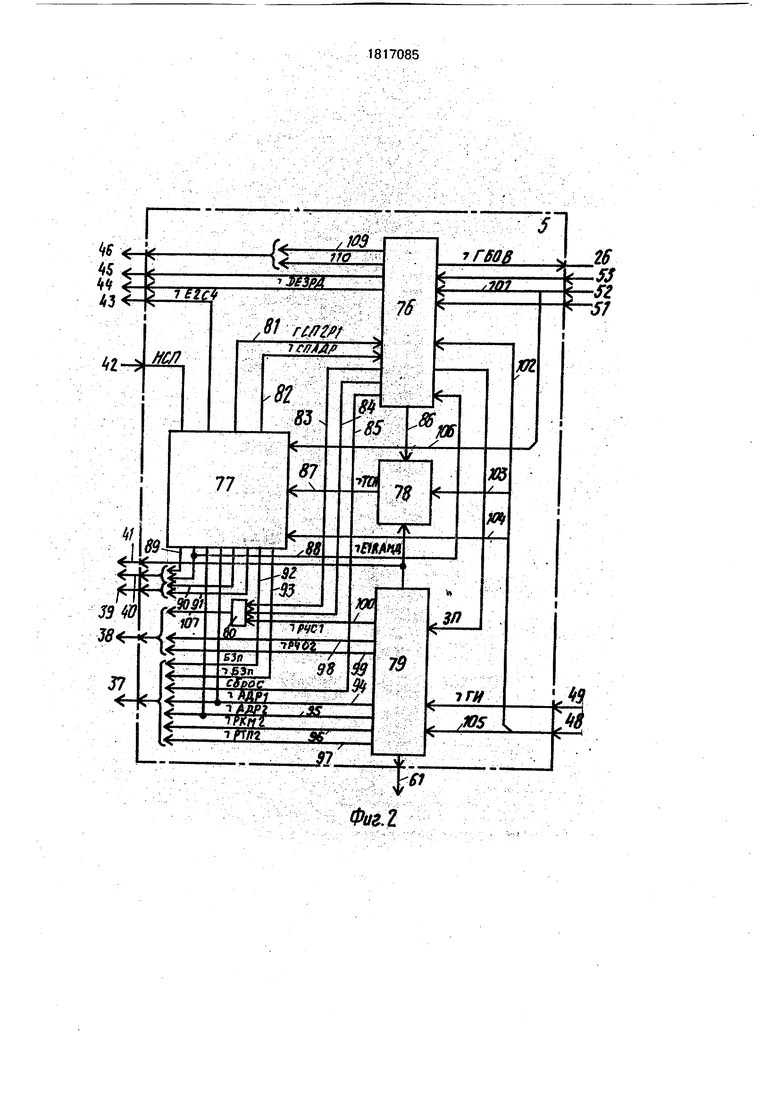

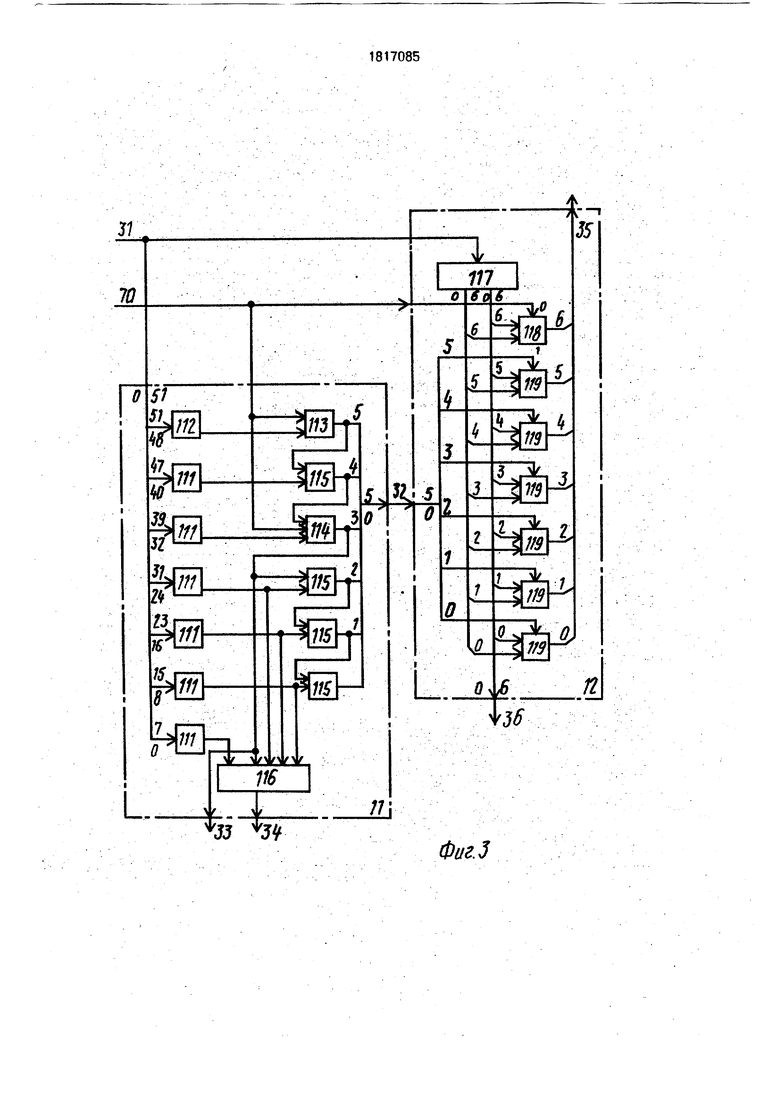

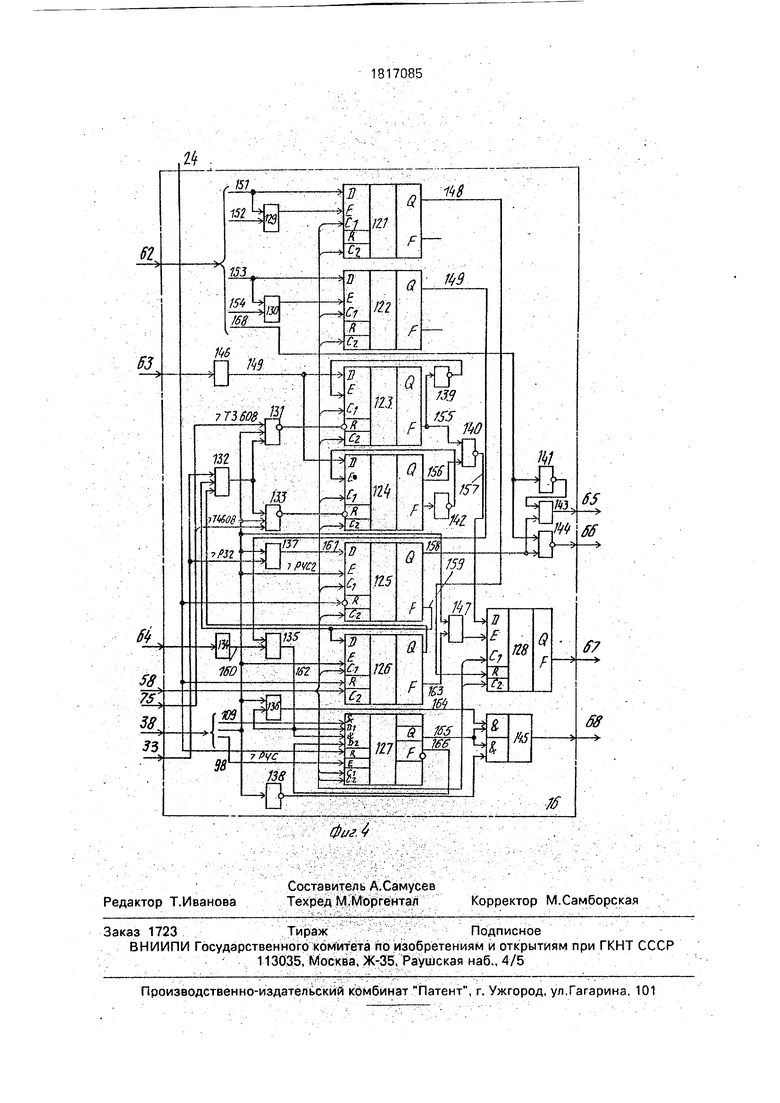

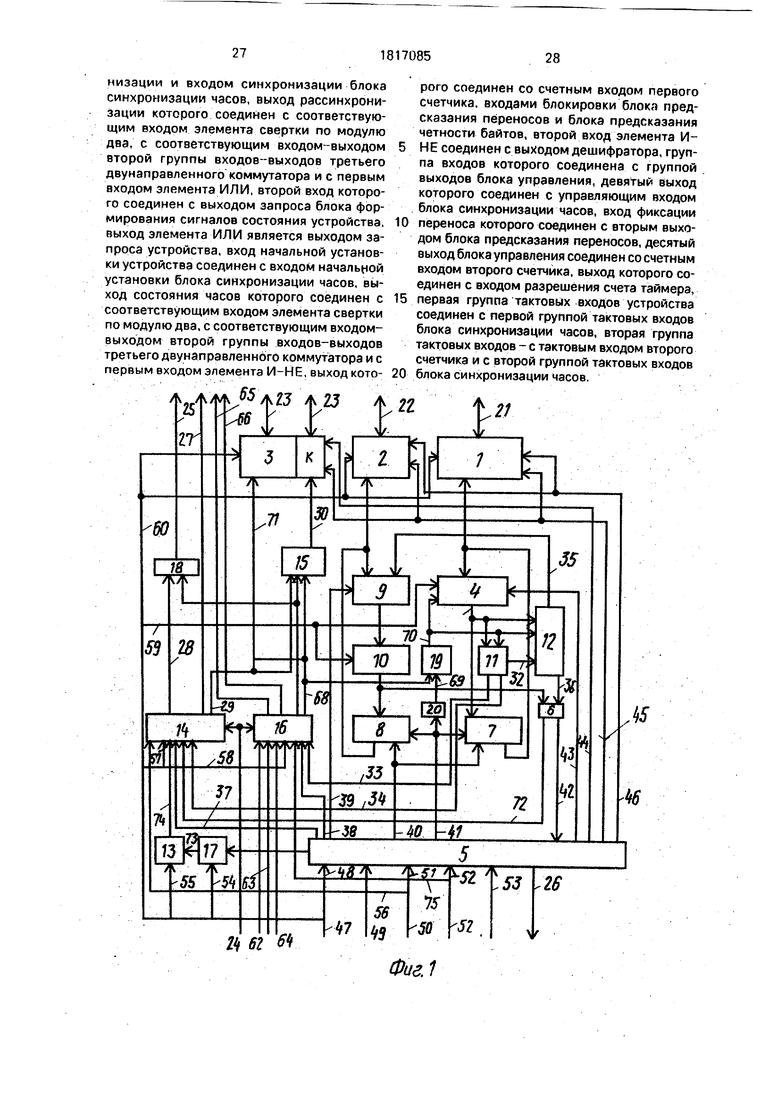

На фиг.1 изображена структурная схема устройства; на фиг.2 - структурная схема блока управления; на фиг.З - функциональные схемы блока предсказания переносов и блока предсказания четности байтов; на фиг.4 - функциональная схема блока синхронизации часов.

На фиг.1-4 приняты следующие обозначения:

1 - первый двунаправленный коммутатор;

2 - второй двунаправленный коммутатор;-....

3 - третий двунаправленный коммутатор;

4 - первый счетчик;

5 - блок управления; 6-блок сравнения;

7 - блок памяти информационных разрядов.

8 - блок памяти контрольных разрядов;

9 - коммутатор; 10-регистр;

11 - блок предсказания переносов;

12 - блок предсказания четности байтов;

13-таймер;

14 - блок формирования сигналов состояния устройства;

15 - элемент свертки по модулю два;

16 - блок синхронизации часов;

17 - второй счетчик; 18-элемент ИЛИ;

19 - элемент И-НЕ;

20 - дешифратор;

21 - первая группа входов-выходов коммутатора 1, группа входов-выходов задания времени устройства;

22.- первая группа входов-выходов коммутатора 2, группа входов-выходов контрольных разрядов;

23 - первая группа входов-выходов вместе с входом-выходом разряда контроля четности коммутатора 3, группа входов-вы-. ходов сигналов состояния вместе с входом- выходом разряда контроля четности устройства;

0 24 - вход начальной установки устройства и блоков 14, 16;28 - выход запроса блока 14, второй вход элемента 18;

26 - выход конца операции внешнего 5 обмена блока 5 и устройства;

27 - выход ошибки устройства и выход ошибки записи/чтения блока 14;

25 - выход запроса устройства, выход элемента 18;

0 29-группа выходов состояния блока 14, соответствующие-входы элемента 15, соответствующие входы-выходы второй группы входов-выходов коммутатора 3;

30 - вход-выход разряда контроля чет- 5 ности второй группы информационных входов-выходов коммутатора 3, выход элемента 15;

31 - группа разрядных выходов счетчика 4, группа информационных входов блока 0 7, первая группа входов блока 12;

32 - группа выходов блока 11, вторая группа входов блока 12;

33 - второй выход блока 11, вход фиксации переноса блока 16;

5 34 - первый выход блока 11, вход фиксации переполнения блока 14;

35 - вторая группа выходов блока 12, вторая группа информационных входов коммутатора 9;

0 36 - первая группа выходов блока 12, вторая Группа входов блока 6;

37 - управляющий вход блока 14, пятый выход блока 5;с

38 - управляющий вхЪд блока 16, вось- 5 мой выход блока 5;

39 - управляющий вход коммутатора 9, седьмой выход блока 5;

40-управляющий вход блоков7 и 8, шестой выход блока 5;

0 41 - группа адресных входов блоков 7, 8, вход дешифратора 20, группа адресных выходов блока 5;

42 - выход неравенства блока 6, вход блокировки записи блока 5; 5 . 43 - вход разрешения счета счетчика 4, первый выход блока 5;

44 - вход управления передачей информации коммутатора 3, четвертый выход блока 5;

45 - вход запрета коммутаторов 1, 2, 3, второй выход блока 5; /

46 - вход управления передачей информации коммутаторов 1, 2, 3, третий выход блока 5; : - -.- ;;./ - ;- . v;. ; ; ;- ;v:; .

47 - вторая группа тактовых входов устройства; ., . ...-. -. / :.-.1М ...; ;

48 - вторая группа тактовых входов блока 5; . . .. : ,:. ; ; . :..:,: ;::: ;У л 49-вход запуска устройства и блока 5;

50 первая группа входов задания начальных условий устройства; : ; v :i

51 - группа входов задания нач льнйх условий блока 5; : v; : 1:;№:.л;

52 - первая группа тактовых входов устройства и блока 5;; V ;

53 - вход задания операций внешнего

обмена устройства и блока 5; ; ;vi;;

54, 55, 57. 59, 60 - группы входов соответственно второго с тчцй; таймера, блока 14, первого енётчйкаи pjervr-: стра, коммутаторов 1 .Зу-ср тву йчй е тактовые входы группы входов 47; 1 ,. - -;

56 - группа входов задания начальных условий блока 14; ; :.. г, - - : -й::Л/-:№ ;

58- вторая группа тактовых вхойо&бло; ка 16; . ... ..-,. :../,.-;.;.;;.. : .Vv; ;--7M-:

61 - счетный вход счётчика 17, девятый выход блока 5; .:-, .:-: -./

62 - вторая группа задания условий устройства, группа зз&ШяйвйапьНЫХ УСЛОВИЙ блока 16;;5 VO :Л ; :; Ч

63, 64 - входы соответственно; контроля синхронизации и синхронизации; устройства, входы соответственно синхронизации и синхронизации б окаТЙ;

65, 66 - выходы соответствен i HtPO: ля синхронизации и сйнхр о йз ац а в; устройства, выходы срртв ст йнвМнтрб ля синхронизации и сйн ро изйцми Вдок|| 16; -...;-.. ....:--v:V ; g$&Ј:

67 - выход рассинхронизации б/foka 1б. соответствующий вход элемента 15, cppt- ветствующий вход-выход второй группу информационных входов-вШойов комму татора 3, первый вход элемента 18; ; Й:

68 - выход состояния часрв блока 16, соответствующий вход элекгента 15, ;Соот ветствующий вход-выход BTid т-pynw информационных входов -вых;рдрв крМму- татора 3, первый вход элемент 19; : 69 - второй вход элемента 19, выход дешифратора 20;, v :: : :v

70 - счетный .вход счетчика 4v выход элемента 19, вход блокировки блоков 11,

71 - вторая группа информационных входов-выходов коммутатора 3 без входа- выхода разряда 30 контроля четности:

72 - выход равенства блока 6, вход фиксации ошибки блока 14;

73 - выход счетчика 17, вход разрешения счета таймера 13;

74 - выход таймера, вход фиксации им- , пульсов продвижения интервального тай- 5 мера блока 14;

; 75 -- первая группа тактовых входов бло

: ка 1 б, соответствующие входы группы вхо

дов 52; . . . . . : / . -.. 76-узел управления внешним обменом

10 блока 5;

77-узел внутреннего управления блока

ff T- - ;:V;.:y:... v. . ;..;. ;.::;

; ; 78 - узел сравнения блока 5; ; : ; ; Т9 - узел формирования адресных сиг- 15 налов блока 5;

: 80-элемент И в блоке5;

;ч ; v 81, 82 - выходы сигналов-тСПАДР1,

лСПАДР2 узла 77, соответствующие входы

У; y:3rta76; - ..- .

20 1 : Щ 84, 85 - выходы сигналовлМОЧСБ,

iSnBOB, СБРОС узла 76, соответствующие

. э л ём е;йта 80 (еигналы- МОЧСБ, ЧЗПБОВ) и узла 77 (сигнал ЗПБОВ) и разряд

V: ; шхбДаi37(сигнал СБРОС);

25 , : 86 - группа адресных выходов узла 76, : пер йай группа входов узла 78, вторая группа

входов(которого соединена с группой адрес- : ;rtbix выходов узла 79 и с группой адресных : ; . 36 87- выход сигналатГСП узла 78, соответ ву

S: Ж 88 - выход сигн алатЕ1НАМД узла 77, : . соответствующий вход узла 76, сортветству- : ющий разряд выхода 40, 35 ,89 - выход сигнал а-МРРАМД узла 77, . Г; сортвётствующий; разряд выхода 40;

90,91 - выходы сигналов узла :;; 77, разряды выхода 39; У 92, 93 -выходы сигналов БЗГЬБЗПузла 40 77, соответствующие разряды выхода 37; v н ;- 04, 95 - выходы сигналов АДР 1,iАДР2

узла 79, соответствующие входы узла 77, ::ii;, срответствующие разряды выхода 37; ;:;:: f ; 96, 97 - выходы сигналов РКМ2, 45 узла 79, соответствующие разряды выхода :37;-.. . ; /,.. -:- . -. . ; . ;

; : 98, 99 - выходы сигналов7РЧС2,-7РЧС узла 79, соответствующие разряды выхода

ВО;Ж- - ; , . -- .

:;;::100-выход сигнала1РЧС1 узла79, соответствующий вход элемента 80; : 101 - первая группа тактовых входов узла 76, тактовых сигналовтТТ2-С1 ,iTT4-C2,

55 1РТЙ1П1лТТ5-С1, РТИ2ВлТ5БОВ, соответствующие входы группы входов 52;

102 - вторая группа тактовых, входов узла 76 тактовых сигналов - С1БОВД, 1С2БОВД,тТЙ2-С2лТИЗ-С2, сортветствую- щие входы группы входов 48:

103 - группа тактовых входов узла 78 тактовых сигналов СИ2-БОВрСИ4-БОВ, соответствующие входы группы входов 48;

104 - вторая группа тактовых входов узла 77 тактовых сигналовчСУИ-БОВггСИб- БОВ. соответствующие входы группы входов 48;

105 - группа тактовых входов узла 79 тактовых сигналовлСИ1-БОВаСИ6-БОВ, соответствующие входы группы входов 48;

106 - первая группа тактовых входов узла 77 тактовых сигналов7ТЗБОВ,УГ4БОВ, соответствующие входы группы входов 52;

107 - выход элемента 80, соответствующий разряд выхода 38;

109,110 - выходы сигналовОЕ 1 РДлЗРД узла 76, соответствующие разряды выхода 46;

111, 112 - элементы И в блоке 11;

113, 114, 115, 116-элементы И в блоке 11; , . :. -.- ;;. v . .

117 - узел формирования сигналов, четности в блоке 12;

118, 119 - коммутаторы в блоке 12;

120 - выход предсказанных сигналов четности байтов узла 117;

121-128 - триггеры в блоке 16;

129, 130 - элементы ИЛИ в блоке 16;

131, 133-элементы И-НЕ в блоке 16;

132-элемент ИЛ И-НЕ в блоке 16;

134- буферный элемент И в блоке 16;

135, 136. 137, 147-элементы И в блоке 16;:

138,141,139,142-элементы НЕ в блоке 16; . . : ..,

140 - элемент И-НЕ в блоке 16;

143 - буферный элемент ИЛИ в блоке 16;

144 - буферный элемент И-НЕ в блоке 16;

145 - элемент 2И-ИЛИ в блоке 16;

146 - буферный элемент И в блоке 16;

148-167- связи между элементами и триггерами в блоке 16.

Идентификаторы сигналов, приведенные над соответствующими связями на фиг.2-4, соответствуют принятым идентификаторам (обозначениям) этих же сигналов (и связей) в прототипе.

Цифры около групп входов и выходов на фиг.З обозначают номера разрядов или входов и выходов.

Обозначение (К-1) на фиг.4 обозначают количество разрядов входов 63 и 64, где К - количество процессоров в мультипроцессорной системе.

Двунаправленные коммутаторы 1, 2, 3 предназначены для подключения устройства к общей магистрали центрального процессора и организации обмена

информацией с центральным процессором ЭВМ, По структуре и функционированию коммутаторы 1, 2, 3 идентичны одноименным коммутаторам прототипа и могут быть

построены на микросхемах типа KM500PG3 или КС1543ИР1. Коммутаторы 1, 2, 3 функ-. ционируют следующим образом При установке на входе 45 логического нуля обеспечивается запрет записи информации

0 с любой группы входов-выходов коммутаторов во внутренний регистр, При установке на входе 45 логической единицы обеспечивается запись информации во внутренний регистр коммутаторов 1, 2, 3 с первой или

5 второй группы информационных входов- выходов коммутаторов (в зависимости от управляющих сигналов на входе 46, 44} под действием тактовых импульсов на тактовых входах 60. Группа 60 тактовых входов состо0 ит из двух тактовых входов, на первый из которых подается тактовый сигнал-КМБОВ, фиксирующий входную информацию, а второй - сигнал1С2БОВ, фиксирующий информацию для передачи на выходы. При

5 установке на разряде 109 выхода 46 логического нуля передача информации на входы- выходы со входов внутреннего регистра блокируется. При логической единице на разряде 109 и логическом нуле на разряде

0 110 обеспечивается передача информации со второй группы информационных входов- выходов на информационные входы внутреннего регистра для записи в регистр и передача информации с выходов внутрен5 него регистра на первую группу информационных входов-выходов коммутаторов, а при логической единице на разряде 109 и логической единице на разряде 110 обеспечивается аналогичная передача информации в

0 обратном направлении.

Первый счетчик 4 предназначен для промежуточного запоминания значений часов, компаратора, таймера процессора, и для модификации (счета) указанных значе5 ний. Счетчик 4 может быть реализован, например, на микросхемах типа КМ500СТ2 или КС1543ИЕ1. Счетчик 4 функционирует следующим образом. При логическом нуле на входе 43 счетчик 4 устанавливается в

0 режим записи кода с информационной группы входов под действием тактовых сигналов на входах 59. При логической единице на входе 43 счетчик 4 устанавливается в режим счета при логической единице на входе 70

5 или - в режим хранения при логическом нуле на входе 70.

Блок 5 управления (фиг.2) предназначен для формирования управляющих сигналов для всех узлов и блоков устройства, для фор мирования адресов часов, коммутатора и

таймера процессора в требуемый временной промежуток времени и для формирования сигнала конца операции внешнего обмена на выходе 26.

Структурная схема блока 5 изображена на фиг.2. Блок 5 содержит узел 76 управления внешним обменом, узел 77 внутреннего управления, узел 78 сравнения, узел 79 формирования адресных сигналов, элемент 80 и. . . . .- - -.; ,.;

Структурная схема блока 5 отличается от структурной схемы блока управления прототипа наличием дополнительного элемента 80 со связями 107, 84, 83, ЮР и выхода 38 с разрядами 107, 98, 99. Блок управления 5 функционирует так же как и блок управления прототипа с тем отличием, что на выходе 38 формируется набор сигналов РЧСлРЧС2,бРЧС1ЬЗПБОВШОЧСБ).

Блок 6 сравнения предназначен для сравнения значений контрольных разрядов с группы выходов регистра 10 и с группы выходов 36 для формирования сигнала равенства (на выходе 72) или сигнала неравенства (на выходе 42).:

Блок 7 памяти информационных разрядов и блок 8 памяти контрольных разрядов предназначены для хранения кодов текущих значений часов (компаратора, таймера процессора) и контрольных кодов значений побайтных сигналов четности кодов текущих значений часов (компаратора, таймера .процессора). Блоки7, Зфункционируютсле;- дующим образом/При нулевом коде на разряде 88 входа 40 выходы блоков 7, 8 блокируются, а при единичном коде на разряде 88 и нулевом, коде на разряде 89 входа 40 на выходы блоков 7, 8 считывается информация, хранимая в блоках по адресу, код которого установлен на входах 41. При единичном коде на разряде 89 входа 40 в блоках 7,8 осуществляется операция записи по адресу, код которого установлен на входах 41.

Коммутатор 9 предназначен для передачи контрольных кодов сигналов чётности с группы выходов блока 8 (при коде на разрядах 90, 91 входа 39, равном 10) или с группы выходов35 (при коде на разрядах90, 91 (входа 39, равном 01).

Регистр 10 предназначен для временного хранения контрольных кодов сигналов четности, передаваемых с выходов блока 8 или выходов 35 блока 12.

Блок 11 предсказания переносов (фиг.З) предназначен для формирования сигналов побайтных предсказанных переносов на выходах 32, предсказанного сигнала переноса в 32-ой разряд кода, установленного на входах 31 (на выходе 33) и предсказанного сигнала переноса из нулевого разряда кода,

установленного на входах 31 (на еыходе 34). Блок предсказания переносов может быть построен на элементах И 111, 112, 113, 114,

115, 116 (фИГ.З),

Структура и функционирование блока 11 идентичны структуре и функционированию одноименного блока прототипа с rewi отличием, что дополнительно введен элемент И 113 со связями и выход 33. Функци

онирование блока 11 однозначно

поясняется функциональной (логической) схемой на фиг.З и не требует дополнительных пояснений.

Блок 12 предсказания четности байтов

(фиг.З) предназначен для формирования побайтных сигналов четности (на выходах 36) для кода, установленного на входе 31 и предсказанных побайтных сигналов четности (на выходах 35) для кода, установленного на входе 31 после его модификации. Блок 12 содержит узел формирования сигналов чётнрстей, коммутаторы 118,119. На выходе 36 формируются побайтные сигналы четностей для кода, установленного на входе 31.

На выходах 120 формируются предсказанные сигналы четности для каждого байта кода, установленного на входе 31, т.е. предполагается, что к значению кода каждого

байта (в младший разряд байта) гфибавлена

единица и для полученного кода - суммы формируется предсказанный сигнал четности на соответствующем выходе 120. Узел

117 может быть построен на элементах ПЗУ, соответствующим образом закодированных

(как в прототипе).

В зависимости от наличия или отсутствия переноса в байт кода на соотвётствую- щий выход 35 передается сигнал либо с

соответствующего входа 120, либо с соответствующего входа 36, В том случае, когда код на входе 31 не модифицируется, например; при режиме Стоп часов, на входе 70 устанавливается нулевой код, под действием которого на выходах 32 устанавливается нулевой код (означающий отсутствие переносов), а на выходы 35 передается код со входов 36, Структура блока 12 отличается от структуры одноименного блока прототипа

наличием дополнительного коммутатора

т, ,-.;.:- ;

Так как введение элемента И 113 в блок П и коммутатора 118 в блоке 12 обусловленоналичием признака - связи 70. то авторы считают нецелесообразным описывать структуру блоков 11 и 12 в формуле изобретения.

Таймер 13 предназначен для формирования 1/300 секунды для продвижения интервального таймера.

Блок 14 формирования сигналов состояния устройства предназначен для формирования следующих сигналов состояния: количество импульсов частотой 1/300 секунды, прерывание от таймера процессора, прерывание от компаратора, легкая ошибка устройства, тяжелая ошибка устройства, сигнал запроса, сигнал ошибки записи/чтения.

Блок 16 синхронизации часов предназначен для формирования сигнала контроля синхронизации часов, сигнала синхронизации часов, сигнала рассинхронизации часов, сигнала состояния часов.

На фиг.4 изображена (в качестве примера) функциональная схема блока 16. Блок 16 может содержать восемь триггеров 121, 122,123,124,125,126,127,128, два элемента ИЛИ 129, 130, три элемента И-НЕ 131, 133, 140, четыре элемента И 135, 136, 137, 147, четыре элемента НЕ 138, 139, 142, 141, элемент ИЛИ-НЕ 132, элемент 2И-ИЛИ .145, буферные элементы И 146, 134, ИЛИ 143, И-НЕ 144. С помощью триггера 121 и входов 151, 152 включается или выключается контроль синхронизации часов. При установке на входе 151 логической единицы в триггере 121 запоминается логическая единица под действием тактовых сигналов -тТИ2-С2 (на входе С1) и-гСИ1-БОВ, которая устанавливается на выходе 148, разрешая устанавливать (разблокируя) триггер 128. Все триггеры 121-126, 128 идентично функционируют. При установке на входах R логического нуля осуществляется сброс триггеров под действием тактовых сигналов на входах С1 и С|. При этом на выходах F нулевые коды устанавливаются только при действии тактового сигнала на входе С2. При установке на входе Е логического нуля, а на входе R логической единицы триггера переходят в режим хранения. При установке на входе Е и R логической единицы в триггерах запоминается код, установленный на входе D. При этом запомненный код передается на выход F только при действии тактового сигнала на входе С2. Триггеры 121-126, 128 могут быть реализованы на микросхемах КС1543ТМ2 или КМ500ТТ2. Триггер 127 функционирует аналогично описанным триггерам с тем отличием, что по входам и реализуется функция 2И-ИЛИ. Триггер 127 идентичен микросхеме КМ500ТТ или КС1543ТМ1.

При блокировке триггера 128 (при логическом нуле на входе 148) на выходе 67 устанавливается (под действием тактовых сигналовтСИЗ-БОВ И7СИ4-БОВ на входах С1 и С2) логический ноль, не влияющий на

функционирование устройства. Для этого на входах 151, 152 устанавливается код 01.

С помощью триггера 122 осуществляется включение или выключение синхронизации часов. При установке на входе 153 логической единицы в триггер 122 записывается логическая единица (под действием тактовых сигналов тТИ2-С2,тСИ1-БОВ на входах С1, С2. На выходе 149 устанавлива0 ется логическая единица, означающая, что синхронизация часов включена, Элемент И 135 разблокировывается и сигнал синхронизации (логический ноль), поступающий на разряды входа 64 хотя бы от одного из (k-1)

5 других процессоров поступает (при отсутствии рассинхронизации) через вход 160 элемента 135 на выход 162 в момент появления сигнала логической единицы на разряде 107 входа 38 (т.е. в момент записи (установки)

0 нового значения часов, т.к. на выходах 83, 84, 100 (фиг.2) устанавливаются логические единицы и, следовательно, устанавливается логическая единица на выходе 107 именно в момент записи (установки) нового значения

5 часов). Так как в этот же момент устанавливается логическая единица и на разряде 98 входа 38, то в триггер 127 под действием тактовых сигналов- СИЗ-БОВ,7-СИ4-БОВ на входах С1, С2 записывается логический

0 ноль, так как на входе 162 устанавливается логический ноль и на выходе 68 устанавливается логический ноль, означающий, что часы запущены в момент установки нового значения часов вследствие совпадения это5 го момента с моментом появления импульса синхронизации на входе 64. Если в момент записи (установки) нового значения часов сигнал синхронизации на входе 64 отсутствует, то на входе 160 и выходе 162 устанав0 ливается логическая единица и в триггер 127 записывается логическая единица, которая устанавливается на выходе 165 и на выходе 68, т.к. на выходе (входе) 164 также устанавливается логическая единица. Логи5 ческая единица на выходе 68 означает, что часы установлены, но переведены в режим Стоп. Логическая единица на выходе 68 сохраняется до тех пор, пока на входе не появится импульс синхронизации (логиче0 ский ноль), который при логической единице на разряде 99 передается на выход 68 через элементы 136, 145 сразу без задержки, а через элемент 135 и выход 162 переводит триггер 127 в нулевое состояние под дейст5 вием тактовых сигналовСИЗ-БОВ и СИ4- БОВ. Передача логического нуля на выход 68 через элемент 136 без задержек необхо-. дима для того, чтобы до появления тактовых сигналов СИЗ--БОВ итСИ4-БОВ подготовить первый счетчик для модификации (счета), а блоки 11, 12 - для соответствующего формирования сигналов четности. При появлении логического нуля на входе 160 и 162 в момент, когда на разряде 99 входа 38 установлен логический ноль, логический ноль на выходе 68 установится только после записи логического нуля в триггер 127 со входа 162, так как логическая единица установлена на входе 167 через элемент НЕ 138. При логическом нуле на разряде 98 триггер 127 находится в режиме хранения. Пока на входе 64 сигнала синхронизации часов не появляется логический ноль, на выходе 162 удерживается логическая единица, которая всякий раз при появлении логической единицы на разряде 98 подтверждает единичное состояние триггера 127 и выхода 68 благодаря логической единице на входе 166. В нулевое состояние триггер 127 переводится и при записи в триггер 122 логического нуля (отключения синхронизации) путем установки на входах 153, 154 кода 01, т.к. на входе 162 в этом случае устанавливается логический ноль. Логический ноль на выходе 68 означает, что часы идут.

Контроль синхронизации часов осуществляется через вход 63. Сигнал контроля синхронизации (логическая единица) на выходе 150 появляется, когда на всех разрядах входа 63 установятся все логические единицы. Достаточно появиться сигналу контроля синхронизации на выходе 150 на время действия тактовых сигнал6втС15БОВД, т С2БОВД (в сумме 40 не), чтобы триггеры были переведены в единичное состояние и сохраняли эти состояния не более чём в течение одной микросекунды до появления логической единицы на разряде 99, если, при этом на входе 33 не появится логическая единица, то триггеры 123, 124 сбрасываются благодаря установке логического нуля на выходах элементов 131, 133 и входах R триггеров 123, 124. Тактовые сигналы ТЗБОВ и-тТ4БОВ на группе входов 75 необходимы для согласования действия тактовых сигналов 7С1БОВД (на входе С1 триггера 123 и на входе С2 триггера 124) и , -/С2БОВД (на входе С2 триггера 123 и на входе С1 триггера 124) с моментом возможного появления сигнала логической единицы на входе 33. Фиксация единичных состояний триггеров 123,124 осуществляется благодаря наличию обратной связи выхода F через элементы НЕ 139, 142 со входом F триггеров 123, 124. При нулевом состоянии триггеров 123, 124 на выходах 155, 156 устанавливается логический ноль, а на выходе 157 -логическая единица. Если на входе 33 появится логическая единица, а она может появиться только при логической

единице на разряде 99, то на входе 161 установится логическая единица, которая под действием тактовых сигналов СИЗ- БОВ (на входе С1)и тСИ4-БОВ (на входе С2) 5 запоминается в триггере 125. При этом через элемент ИЛИ-Н Е 132 сигналами с входа 33, а затем с выхода 159 (F) триггера 122 предотвращается сброс триггеров 123, 124, если они установлены или установятся в

0 единичное состояние в течение двух микросекунд (до третьего появления логической единицы на разряде 99), При этом логическая единица со входа 159 перезапоминается с появлением второго сигнала логической

5 единицы на разряде 99 в триггер 126, т.к. на тактовые входы С1, С2 триггера 126 действуют тактовые сигналыгСИЗ-БОВ и/СИ4- БОВ. С появлением третьего сигнала логической единицы на разряде 99, на входе

0 Е триггера 128 (через элемент И 147) появляется сигнал (логическая единица) разрешения записи в триггер. Если не более чем за одну микросекунду до появления сигнала (логической единицы) на входе 33 или в те5 чение Одной последующей микросекунды пока на выходе 159 установлена логическая единица или в течение третьей микросекун-- ды пока на выходе 163 установлена логическая единица на входе 63 контроля

0 синхронизации появится единичный код на время не менее 40 не, то триггеры 123, 124 установятся в единичное состояние и будут удерживаться в таком состоянии до окончания третьей микросекунды. При этом на вы5 ходе 157 элемента 140 устанавливается логический ноль,, который записывается в триггер 128 под действием тактовых сигна- лов- СИЗ-БОВ,7СИ4-БОВ и на выходе 67 устанавливается логический ноль, означаю0 щий, что рассинхронизации часов нет. Если в течение указанных трех микросекунд импульс контроля синхронизации на выходе 150 не появляется, то на входе 157 удерживается логическая единица, которая записы5 вается в триггер 128, а на выходе 67 устанавливается логическая единица, означающая, что часы рассинхронизированы. После появления единичного сигнала на входе 33 и записи его (через элемент И 137)

0 в триггер 125 на выходе 158 триггера 125 устанавливается логическая единица, которая формирует (через элемент 144) сигнал (логический ноль) синхронизации часов на выходе 66, и (через элемент 143) сигнал (ло5 гическую единицу) контроля синхронизации часов на выходе 65, Сформированные на выходах 65, 66 сигналы удерживаются в течение одной микросекунды, т.к. через одну микросекунду (при РЧС2 1) на входе 33

установится уже логический ноль, который

записывается в триггер 125 и на выходах 158, 65 устанавливается логический ноль, а на выходе 66 устанавливается логическая единица. При этом логическая единица с выхода 159 успевает перезаписаться в триггер 126, Однако к концу второй микросекунды (с момента появления логической единицы на входе 33) на входе 159 установится логический ноль, который записывается в триггер 126 с появлением третьего сигнала (логической единицы) на разряде 99, т.е. триггеры 125,126 переходят в исходное состояние. При этом состояние триггера 128 и выхода 67 может удерживаться в течение более чем одной секунды до появления нового сигнала на входе 33 или в триггере 128 и на выходе 67 может быть установлено нулевое состояние после установки триггера 121 в нулевое состояние. После установки триггера 121 вновь в единичное состояние цикл контроля синхронизации повторяется. Сигналы синхронизации на выходе 66 и контроля синхронизации на выходе 65 формируются при условии установки на входе 168 логической единицы. При установке на входе 168 логического нуля выходы 65, 66 блокируются, т.е. часы отключаются от микропроцессорной системы. При этом синхронизация их и контроль синхронизации может быть сохранен.

Второй счетчик 17 предназначен для формирования сигнала (на выходе 73) через каждые 256 мкс. Счетчик 17 - восьмиразрядный и может быть построен, например, на микросхемах типа КМ500СТ2 или КС15433ИЕ1. Счетчик 17 функционирует следующим образом. При установке на входе 61 логической единицы счетчик 17 переходит в режим счета и к содержимому счетчика, прибавляется единица под действием тактовых сигналов на входах 54. В момент, когда счетчик должен обнулиться при появлении логической единицы на входе 61, на выходе также появляется логическая единица.

На выходе 69 дешифратора 20 появляется логическая единица, если на выходе 41 устанавливается код адреса часов или компаратора. Дешифратор 20 представляет собой стандартный узел.

Устройство работает следующим образом.

В исходном состоянии на входы 47, 52 не поступают тактовые сигналы. После включения электропитания по последовательным цепям сброса, не показанным на чертежах, во все триггёрные и регистровые элементы памяти заносятся нулевые коды. На входах 53. 62 устанавливается нулевой код. На входах 50 устанавливаются требуемые коды начальных условий. На вход 49

подается запускающий сигнал, представляющий импульсы длительностью 500 не, поступающие на вход 49 с периодичностью 1 мкс. Затем осуществляется запуск тактовых

сигналов на входах 47, 52. На вход 47 начинают поступать тактовые сигналы задающей серии -7С1БОВ(7С1БОВД), тС2БОВ (7С2БОВД), основной серии -гСШ-БОВ, 7СИ2-БОВ, - СИЗ-БОВлСИ4-БОВ, 7СИ60 БОВ, процессорной серии -гТИ2-С2,7ТИЗС2. На вход 52 начинают поступать тактовые

сигналы вспомогательной основной серии 7ТЗБОВ,--Т4БОВ,-гТ5БОВ и вспомогатель-1

ной процессорной серии - ТТ2-С1 ,тТТ4

5 С2лТТ5 С1,тРТИ1П1, РТИ2В. Сигналы -7С1БОВ (тС1БОВД) и 7С2БОВ (С2БОВД) представляют собой импульсы длительностью меньшей 20 не и большей 10 не, поступающие каждый на свой тактовый вход с

0 периодичностью 40 не. При этом, при отсутствии импул bead БОВ (tC1 БОВД) появляется импульс 7С2БОВ (тС2БОВД) и наоборот. Сигналы 7СИ1-БОВ,тСИ2-БОВ,7СИЗ-БОВ, 7СИ4-БОВ, 7СИ5-БОВ, тСИ6-БОВ пред5 ставляют собой сигналы, длительностью такой же, как и сигналы -тС1БОВ (тС2БОВ), поступающие последовательной каждый на свой, соответственно, первый, второй, третий, четвертый, пятый, шестой тактовые

0 входы. Периодичность поступления каждого импульса на своем тактовом входе равна 120 не. При этом импульс СШ-БОВ появляется на i-ом тактовом входе через 20 не после начала появления импульса СИ

5 (Ы)-БОВ на (Ы)-ом тактовом входе. Сигналы тТИ2-С2 и тТИЗ-С2 соответствуют сигналам -7СИ2-БОВ и СИЗ-БОВ, но появление - импульсов7ТИ2-С2 и- ТИЗ-С2 не синхронизировано с появлением импульсов СИ20 БОВ игСИЗ-БОВ. По этой причине моменты появления импульсов-Л И2-С2 могут совпадать с моментами появления импульсов 7СИ2-БОВ или7СИ4-БОВ,7СИ6-БОВ, а моменты появления импульсовтСИЗ-С2 могут

5 совпадать с моментами появления импульсов тСИ1-БОВ.7СИЗ-БОВ,7СИ5-БОВ. Сигнал тСИ5-БОВ в устройстве не используется.

Сигналы тТЗБОВлТ4БОВ,-ГГ5БОВ пред0 ставляют собой импульсы длительностью 40 не, поступающие каждый на свой тактовый вход с периодичностью 120 не. При этом импульсУГЗБОВ действует во время действия импульсов СИ2-БОВ, 7СИЗ-БОВ, им5 пульс 7Т4БОВ действует во время действия импульсов7СИЗ-БОВ,СИ4-БОВ, импульс Т5БОВ действует во время действия импульсов 7СИ4-БОВ, - СИ5-БОВ. Тактовые сигналы Т1БОВ,Т2БОВ,тТ6БОВ в устрой стве не используются.

Сигналы 7TT2-C2,rTT4-C2,- TT5-Ci аналогичны сигналам -гТ2БОВ,7Т4БОВ,7Т5Бр0, но формируются асинхронно, т.е. сигналы :; 7 ТТ2-С2 (JTT4-C2) могут совпадать пр времени появления с сигналами 7T2j5(DB, 5 -fT4BOB,VT650B, а сигна пТТ5-С1 может ; совпадать с сигналами 7Т1ЁОВ, 1ТЗБОВ, Т5БОВ. ,: ;-.- ; :; :; .ji.i ::;;;;

Сигналы7РТИ1П1 и РТЙ2Вi прёщабля- ют собой импульсы, длительность 1 6торь1Х Ю кратна 120 не, а периодичность прйвления ; асинхронна, т.е. моменты появления заранее не определены, т.к. соответрт т - : . ментам включения (выкинем и я) синхронизации центрального процессора 15 при приостановках его работы в связи с . взаимодействием оперативной памяти с каналами ввода-вывода.. .. у.;

Сигналы 7ТТ2-С2; ГТТ4-С2, 7ТТ5-С1, 7 РТЙ1Л.1, РТИ2В, 1ТИ2-С2,-|ТИЗ-С2 необ- 20 ходимо использовать для частичной синхронизации работы устройства с работой центрального процессора при обмене информацией, что связано с конкретной реализацией устройства и его применением, 25 Затем микропрограммно (с помощью центрального процессора) через входы/выходы 22, 21 устанавливаются нулевые показания (нулевой код) часов, компаратора, таймера процессора путем установки на входах 53 30 последовательно, каждый раз преде появления сигнала готовности на выходе 26 кода записи показаний часов, компаратора, таймера процессора. Затем на входе 53 устанавливается код чтения часов и, побле 35 появления сигнала готовности на выходе 26, на вход 24 подается сигнал сброса (СБР- ОШЗП) длительностью 120 не. Затем на входах 53 устанавливается код записи компаратора и через входы/выходы 21, 22 в 40 компаратор записывается единичный код.

На выходе 25 и выходе 28 должен появиться сигнал запроса на прерывание, а на выходах 29 формируется код с признаком прерывания от компаратора.45

После указанной последовательности операций устройство считается приведенным в исходное состояние.:

Таким образом, на входах 53 могут уста- ; навливаться следующие коды: 50 . - нулевой код - при отсутствии операций внешнего обмена информацией (с цен- ральным процессором);

- код записи часов (КЗЧ) - для записи нового значения часов;55

-, код записи Компаратора (КЗК) - для записи нового значения компаратора;

. код записи таймера процессора (КЗТ) У

для записи нового значений таймера роцессора;

-v - код чтенияi часбв (КЧЧ) - для чтения

значения ча1е0 ; . : ..;v-:..- -

- - код (КЧК) - для

чтения знфЦйнщя KjciMrra|pTOpa;

; -: код чтения T$8Wfepa npduiecqp (КЧТ)

- для чтения значейй таймера ripbifeccOpa. ,Й: При этому при установке на входах 53 ОдОв , КЗК, КЗТ на входах/выходах 21 уйтанё.вййваютея коды значений часов, компаратора таймера процессора, передаваемых из центрального процессора, а на входах-выходах 22 - их контрольные коды чётности, В блоке 5, после появления сигнала (логической единицы) тТСП на входе 87 узла 77 и появления последовательно сигна- лов АДР и -АДР2 на выходах Й4, 95 узла 79 на.вмходах 81,82 появляются в соответству- юидей последовательности сигналы з СПАДР1 и 1СПАДР2. Под действием сигнала i ЕШАМД на входе 88 и кода на входах 53 узла 76 и совокупности тактовых сигналов на входах 102, 101 узла 76, на выходах 44,45,46 (разрядах 109,110) узла 76 и блока 5 формируются сигналы в требуемой последовательности, обеспечивающие запись кодов, установленных на входах-выходах 21, 22 во внутренний регистр коммутаторов 1, 2, Однако только после появления требуемой комбинации сигналов УПР, УПРлЕ2СЧ

-г WRRAMfl, тЕШАМД на выходах 39 (разряды 90, 91), 43/40 (разряды 89, 88), обеспечивающих перезапись кодов из внутренних регистров коммутаторов 1, 2 в счетчик 4 и регистр 10 и далее в блоки памяти 7, 8, под действием сигнала СПАДР2 на входе 82 узла 76 на выходе 26 появляется сигнал (логическая единица) конца операции внешнего обмена. Параллельно осуществляется контроль по четности принятых кодов с помощью блоков 11, 12. Если имеет место ошибка, то на выходе 72 формируется логическая единица, которая под управлением сйгнала-|АДР1 на разряде 94 запоминается в соответствующем триггере состояния блока 14 под действием тактовых сигналов рЙ1-БОВ, 7СИ6-БОВ на входах 57. В результате на выходе 27 устанавливается логическая единица, информирующая, что при выполнении записи произошла ошибка. Запись кодов в счетчик 4 и регистр 10 осуществляется йбД действием тактовых Сигналов . 7СЙЗ-60В,7СИ4-БОВ дважды, в момент Действия сйШалатСПАДР1 и 7СПАДР2. На выходах 6S, 66, 67, 68 в рассматриваемом случае установлены логические нули, кото- ры% не влияют на функционирование счет- чМаъ4. .. . . .-.. ..

Следует заметить, что если имеет место ошибка при записи, то на выходе 42 устанав- ливается логический ноль, который устанавливает на выходе 89 узла 77 логическую единицу, благодаря чему предотвращается запись ошибочного кода и его контрольного кода в блоки памяти 7, 8. Сигналы (логические единицы) 1АДР1, АДР2 появляются по- следовательно друг за другом на время 120 не каждый (в промежуток времени (СИ1- БОВлСИб-БОВ) с периодичностью 240 не. СигналыСПАДР1,7СПАДР2 идентичны сигналам соответственно ДДР1,7 АДР2, но по- являются только при появлении сигнала ТСП на входе 87 узла 77.

Описанный режим функционирования устройства является режимом записи (РЗ).

При установке на входах 53 кодов КЧЧ, КЧК, КЧТ в устройство начинает функционировать в режиме чтения, который отличается от режима счета, устанавливаемого при нулевом коде на входе 53, только тем, что во время действия сигнала СПАДР1 на выхо- дах 44, 45, 46 .блока 5 формируется такая совокупность сигналов, которая обеспечивает запись кодов, считанных из блоков 7, 8 и из выходов 29, 30 во внутренний регистр коммутаторов 1, 2, 3 и выдачу их на входы- выходы 21, 22, 23 в требуемый момент времени, определяемый моментом появления тактового сигнала 7ТЙ2-С2. При этом, как и в режиме записи, сигнал (логическая единица) на выходе 26 появляется под действием сигнала 7СПАДР2 в момент действия тактового сигнала ЛТ4-С2. Установка логического нуля на выходе 26 как при режиме записи, так и при режиме чтения осуществляется через 120 не в моменты действия сигналов ТТ4-С2, РТИ2В.

В режиме чтения осуществляется также формирование сигнала (логического нуля) сброса (СБРОС) на выходе 85 (см. фиг.2), под действием которого осуществляется сброс (обнуление) всех триггеров состояния в блоке 14, выходы которого соединены с выходами 25, 29, т.к. коды указанных триггеров записываются во внутренний регистр коммутатора 3 для передачи в центральный процессор для хранения и анализа.

Параллельно осуществляется запись в соответствующие разряды внутреннего регистра коммутатора 3 кодов с выходов 67,68 блока 16 для анализа их с целью определе- ния наличия (или отсутствия) рассинхрбни- зации часов и состояния часов. С выхода 30 в контрольный разряд внутреннего регистра коммутатора 3 записывается код значения четности для кода на входе-выходе 71 для контроля достоверности передачи кода состояния с первой группы входов-выходов коммутатора 3 в центральный процессор,

Сигнал тТСП на выходе 87 узла 78 формируется под действием тактовых сигналов

1 СИ2-БОВ, СИ4-БОВ при равенстве кодов адреса на выходе 41 и на выходе 86. На выходе 86 формируется код адреса часов или компаратора, или таймера процессора в зависимости от кода операции, установленного на входе 53 соответственно КЗЧ, КЧЧ или КЗК, КЧК, или КЗТ, КЧТ.

В режиме счета (когда на входах 53 установлен нулевой код) на выходах 86 (фиг.2) также устанавливается нулевой код, В результате на выходе 87 и, следовательно, на выходах 81, 82 устанавливается нулевой код. На выходах 44, 45, 46 устанавливается такая комбинация сигналов, при которой коммутаторы 1,2,3 отключаются от входов- выходов. С каждым появлением сигнала (логической единицы)тГИ на входе 49 начинает формироваться последовательность сигналов- АДР1 на выходе 94 И-ДЦР2 на выходе 95, а на выходе 41 формируется последовательно код адреса часов, код адреса компаратора, код адреса таймера процессора. Каждый новый код на выходе 41 удерживается в течение действия сигналовт АДР1 и 7 АДР2. Появление сигнала (логической единицы)7РЧС1 (|РЧС2,1РЧС)на выходе (разряде) 100 совпадает по времени с появлением сигнала 1АДР1 (тАДР2,7АДР1 и АДР2) и установкой на выходе 41 кода адреса часов. Появление сигнала РКМ2 на выходе (разряде) 96 совпадает по времени с появлением сигнала т АДР2 и установкой на выходе 41 кода адреса компаратора. Появление сигнала -I РТП2 на выходе (разряде) 97 совпадает по времени с появлением сигнала АДР2 и установкой на выходе 41 кода адреса таймера процессора. Сигналы 7рШ2, тРТП2 управляют фиксацией сигнала переполнения со входа 34 блока 14 отдельно для компаратора и таймера процессора.

Сигналы АДР1 итАДР2 на разрядах 94, 95 управляют фиксацией сигнала ошибки со входа 72 блока 14 отдельно соответственно после чтения информации из блока 7 и после модификации кода в счетчике 4.

Сигналы БЗП, БЗП на разрядах 92, 93 управляют фиксацией сигнала ошибки со входа 72 блока 14 отдельно при режиме записи и устройстве и при режиме счета.

В режиме счета (так же как и чтения) в течение действия сигналатАДР1 осуществляется чтение кодов из блоков 7, 8 и запись их в регистр 10 и счетчик 4 под действием тактовых сигналов СИЗ-БОВ, СИ4-БОВ благодаря установке соответствующей комбинации управляющих сигналов на выходах 39, 40, 43. Состояние выхода 70 может быть произвольным. На выходах 36 формируется контрольный код, который сравнивается с контрольным кодом с выходов регистра 10.

Сигнал ошибки (если он появился) фиксируется со входа 72 и передается на выход 27. В течение действия сигнала АДР2 осуществляется модификация (счет) кодов, запомненных в счетчике 4 и запись в регистр 10 предсказанного контрольного кода со входов 35 под действием тактовых сигналов -/СИЗ-БОВ,тСИ4-БОВ благодаря установке на выходах 39, 44 соответствующей комбинации управляющих сигналов.

При этом на выходе 70 должна быть установлена логическая единица. В случае, когда часы переходят в состояние Стоп и их значение модифицировать (считать) так же, как и значение компаратора, нельзя, то на выходе 68 в этом случае устанавливается логическая единица. На выходе же 69 также устанавливается логическая единица при установке на выходе 41 кода адреса часов или компаратора. На выходе 70 устанавливается нулевой код, благодаря которому модификация кода в счетчике 4 не происходит (т.к. счетчик переходит в режим хранения), При этом на выходах 35 формируется контрольный код, равный коду на выходах 36, благодаря чему обеспечивается правильный контроль ошибок, т.к. на выходах регистра 10 должен быть (при отсутствии ошибок)установлен код, равный коду на вьй ходах 36.

Во всех остальных случаях на выходе 70 устанавливается логическая единица и обеспечивается счет в счетчике 4.

Далее в момент дейст вия тактового сигнала уСИб-БОВ осуществляется запись в блоки 7, 8 кодов с выходов регистра 10 и счетчика 4 благодаря формированию соответствующих сигналов на выходе 40, При этом в блоке 14 под управлением сигнала т АДР2 фиксируется сигнал ошибки с выхода 72 (если он появился) и на соответствующем выходе 29 устанавливается логическая единица.

Далее, с появлением тактового сигнала 7СИ1-БОВ вновь формируются сигналы АДР1,7АДР2, но с новым адресом на выходе 41, и алгоритм работы устройства повторяется.

При действии сигнала АДР2 и установки кода адреса часов на выходах 41 на выходе 61 появляется сигнал (логическая единица) и в счетчике 17 происходит модификация (прибавление единицы) содержимого счетчика 17 под действием тактовых сигналов7СИЗ-БОВ,СИ4-БОВ.

При появлении на входе 61 256-го по счету сигнала на выходе 73 переполнения счетчика 17 также устанавливается сигнал (логическая единица), под действием которого к содержимому таймера 13 прибавляется единица под действием тактовых сигналов СИЗ-БОВ,СИ4-БОВ. При этом счетчик 17 обновляется. Когда на входе 73 появится 13-й по счету сигнал, на выходе 74 5 также появится сигнал (логическая единица), который зафиксируется в блоке 14 Шк, сигнал продвижения интервального тайме- ра под действием тактовых сигналов СЙЗ- БбВ, СИ4-БОВ. При этом на

0 соответствующем выходе 29 устанавливается логическая единица. При всех случаях фиксации сигналов ошибки на входе 72, сиг-, налов переполнения на входе 34 и сигналов продвижения интервального таймера не

5 входе 74 блока 14, осуществленные при действии сигнала, АДР2 и режиме счета устройства, на соответствующих выходах 29 и выходе 25, 28 устанавливается логическая единица. Логическая единица на выходе 28

0 информирует центральный процессор b необходимости обработки байта состояния на входах-выходах 71. По сигналу на выходе 28 центральный процессор задает в устройстве режим чтения по адресу часов путем

5 установки на входах 53 кода КЧЧ. В центральном процессоре по состоянию соответствующих битов считанного кода состояния с выходов 29, 68, 67 распознаются наличие Ошибок, переполнение компаратора и тай0 мера процессора, наличие запросов на про- : движение интервального таймера и количество продвижений, з также состояние часов и признак рассинхронизации часов.

5 Таким образом, сигнал продвижения интервального таймера всегда формируется с периодичностью Т 256 х 13 3328 мкс- «1/300 с.

В прототипе, при установке нового зна0 чения часов возможна потеря максимум 256 мкс либо удлинение во времени интервала : продвижения на максимум 256 мкс. В результате точность формирования интервалов продвижения интервального таймера в

5 прототипе находится в пределах +256 256 мкс. В заявляемом устройстве точность формирования интервалов продвижения интервального таймера находится в пределах долей микросекунды.:

0 Следовательно, достигается цель изобретения - повышение точности формиро- - вания временных интервалов продвижения интервального таймера.

Указанный количественный эффект за5 явленного устройства достигается при условии использования прототипа и заявленного устройства в одной и той же области применения, т.е. в однопроцессорной вычислительной системе. В многопроцессорных вычислительных системах прототип (его структуру) невозможно использовать вследствие еще большего ухудшения точности (до 1 с) формирования интервалов продвижения интервального таймера вследствие необходимости задавать состояние Стоп часов.

С целью обеспечить требуемую точность формирования интервалов продвижения интервального таймера и обеспечить одновременно синхронизацию часов и контроль синхронизации часов (что необходимо для расширения области применения устройства, т.е. обеспечить возможность применения в мультипроцессорных системах) и введен счетчик 17, элементы 19, 18, дешифратор 20, блок 16.

Синхронизация часов и контроль синхронизации часов может быть выключен (в однопроцессорной вычислительной системе) или включен путем установки соответствующих кодов на входы 62 в произвольный момент функционирующего устройства (см. описание блока 16). Включение (выключение) осуществляется (в рассматриваемом примере (фиг.4)) в момент действия тактового сигнала 7ТИ2-С2. На вход 63 поступают входные сигналы контроля синхронизации часов, а на вход 64 - входные сигналы синхронизации часов. На выходе 65 формируются выходные сигналы контроля синхронизации часов, а на выходе 66 формируются выходные сигналы синхронизации часов. Каждый раз при записи нового значения часов (при коде КЗЧ на входе 53) и при включении контроля синхронизации и синхронизации часов, часы в устройстве переходят в состояние Стоп, если в момент записи часов сигнал синхронизации часов на входе 64 отсутствует (см. описание блока 16). При этом на выходе 68 устанавливается логическая единица, под управлением которой в счетчике 4 предотвращается модификация (счет) значений часов и компаратора (см. описание режима счета устройства).

Фиксация состояния Стоп часов осуществляется под управлением соответствующей комбинации сигналов на выходе 38 (см. описание блока 16).

Часы переходят в состояние идут из состояния Стоп, если на входе 64 появится сигнал синхронизации (хоть один логический ноль) или если через входы 62 будет отключена синхронизация часов. В этом случае на выходе 68 устанавливается логический ноль, обеспечивающий модификацию (счет) часов и компаратора. При появлении сигнала переноса в 32-ой разряд с выхода 33 в блоке 16 осуществляется фиксация сигнала (логической единицы) контроля синхронизации на выходе 65 и сигнала (логического нуля) синхронизации на выходе 66. Сигналы на выходах 65, 66 удерживаются в течение 1 мкс. Если за одну

микросекунду до появления сигнала на входе 33 или в течение одной микросекунды в течение действия сигналов на выходах 65, 66 или в течение одной микросекунды после исчезновения сигналов на выходах 65, 66

0 появится сигнал контроля синхронизации (единичный код) на входе 63, то в блоке 16 фиксируется состояние отсутствия рассинх- ронизации часов и на выходе 67 фиксируется логический ноль. В противном случае в

5 блоке 16 фиксируется состояние рассинхро- низации часов и на выходе 68 устанавливается логическая единица, которая устанавливается на выходе 28, информируя центральный процессор о необходимости

0 обработки байта состояния устройства с входов 71. Точность контроля синхронизации + 1 мкс в заявленном устройстве обусловлена допустимой точностью работы часов, принятой в прототипе и заявленном

5 устройстве.

Таким образом, обеспечивается работоспособность устройства в мультипроцессорных системах за счет возможности обеспечивать состояние Стоп часов, синх0 ронизацию часов и контроль синхронизации часов. Следовательно, достигается поставленная цель изобретения - расширение области применения за счет применения в мультипроцессорных системах

5 одновременно с достижением дополнительного положительного эффекта - повышение точности формирования интервалов продвижения интервального таймера (см. описание выше).

0 Формула изобретения

Устройство для отсчета времени, содержащее три двунаправленных коммутатора, первый счетчик, блок управления, блок сравнения, блок памяти информационных

5 разрядов, блок памяти контрольных разрядов, коммутатор, регистр, блок предсказания переносов, блок предсказания четности байтов, таймер, блок формирования сигналов состояния устройства, элемент свертки

0 по модулю два, причем группа адресных входов блока памяти контрольных разрядов соединена с группой адресных входов блока памяти информационных разрядов и с группой выходов блока управления, вход запу5 ска которого является входом запуска устройства, вход задания операций внешнего обмена которого соединен с одноимент ным входом блока управления, группа входов задания начальных условий которого является соответствующей частью первой группы входов задания начальных условий устройства, оставшаяся часть входов первой группы входов задания начальных условий устройства соединена с группой входов задания начальных условий блока формирования сигналов состояния устройства, первая группа тактовых входов блока управления является первой группой тактовых входов устройства, вход блокировки записи блока управления соединен с выходом неравенства блока сравнения, выход равенства которого соединен со входом фиксации ошибки блока формирования сигналов состояния устройства, вход фиксации переполнения которого соединен с первым выходом блока предсказания переносов, группа выходов которого соединена со второй группой входов блока предсказания четности байтов, первая труппа входов которого соединена с группой входов блока предсказания переносов, с группой разрядных выходов первого счетчика и с группой информационных входов блока памяти информационных разрядов, вход записи которого соединен с входом записи блока памяти контрольных разрядов и с первым выходом блока управления, второй выход которого соединен с управляющим входом коммутатора, группа выходов которого соединена с группой информационных входов регистра, а вторая группа информационных входов коммутатора соединена с второй. группой выходов блока предсказания четности байтов, первая группа выходов которого соединена со второй группой входов блока сравнения, первая группа входов которого соединена с группой разрядных выходов регистра и с группой информационных входов блока памяти контрольных разрядов, группа выходов которого соединена с первой группой информационных входов коммутатора и с второй группой информационных входов-выходов второго двунаправленного коммутатора, вторая группа информацией- ных входов-выходов первого двунаправ- ленного коммутатора соединена с группой выходов блока памяти информационных разрядов и с группой информационных входов первого счетчика, вход разрешения счёта которого соединена с третьим выходом блока управления, четвертый выход которого соединен с входами разрешения первого, второго и третьего двунаправленных коммутаторов, входы управления передачей информации первого и второго двунаправленных коммутаторов соединены с пятым выходом блока управления, шестой выход которого соединен с входом управления передачей информации третьего двунаправленного коммутатора, первая группа

информационных входов-выходов первого двунаправленного коммутатора является группой входов-выходов задания кода времени устройства, первая группа информационных входов-выходов второго двунаправленного коммутатора является группой входов-выходов контрольных разрядов устройства, первая группа информационных входов-выходов вместе с входом-выходом разряда контроля четности третьего двунаправленного коммутатора является труппой входов-выходов сигналов состояния вместе с входом-выходом разряда контроля четности устройства, выход ошибки которого соединен с выходом ошибки блока формирования сигналов состояния устройства, группа выходов состояния которого соединена с группой входов элемента свертки по модулю два и входами- выходами второй группы информационных входов-выходов третьего двунаправленного коммутатора, вход-выход разряда контроля четности второй группы информационных входов-выходов которого соединен с выходом элемента свертки по модулю два, выход таймера - с входом фиксации блока формирования сигналов состояния устройства, управляющий вход которого соединен с седьмым выходом блока управления, восьмой выход которого является выходом конца операции внешнего обмена устройства, вход начальной установки устройства соединен с входом начальной установки блока формирования сигналов состояния устройства, вторая группа тактовых входов которого соединена с группами тактовых входов первого, второго и третьего двунаправленных коммутаторов, счетчика, регистра, блока формирования сигналов состояния устройства, таймера и с второй группой тактовых входов блока управления, отличающее с я тем, что, с целью расширения области применения устройства и повышения точности формирования временных интервалов продвижения интервального таймера, устройство дополнительно содержит элемент ИЛИ, элемент И-НЕ, дешифратор, второй счетчик, блок синхронизации часов, причем вторая группа входов задания начальных условий устройства соединена с группой задания начальных условий блока синхронизации часов, выход контроля синхронизации и выход синхронизации которого являются соответственно выходом контроля синхронизации часов и выходом синхронизации часов устройства, вход контроля синхронизации часов и вход синхронизации часов которого соединены соответственно со входом контроля синхронизации и входом синхронизации блока синхронизации часов, выход рассинхрони- зации которого соединен с соответствующим входом элемента свертки по модулю два, с соответствующим входом-выходом второй группы входов-выходов третьего двунаправленного коммутатора и с первым входом элемента ИЛИ, второй вход которого соединен с выходом запроса блока формирования сигналов состояния устройства, выход элемента ИЛИ является выходом запроса устройства, вход начальной установки устройства соединен с входом начальной установки блока синхронизации часов, выход состояния часов которого соединен с соответствующим входом элемента свертки по модулю два, с соответствующим входом- выходом второй группы входов-выходов третьего двунаправленного коммутатора и с первым входом элемента И-НЕ, выход которого соединен со счетным входом первого счетчика, входами блокировки блока предсказания переносов и блока предсказания четности байтов, второй вход элемента И- НЕ соединен с выходом дешифратора, группа входов которого соединена с группой выходов блока управления, девятый выход которого соединен с управляющим входом блока синхронизации часов, вход фиксации переноса которого соединен с вторым выходом блока предсказания переносов, десятый выход блока управления соединен со счетным входом второго счетчика, выход которого соединен с входом разрешения счета таймера, первая группа тактовых входов устройства соединен с первой группой тактовых входов блока синхронизации часов, вторая группа тактовых входов - с тактовым входом второго счетчика и с второй группой тактовых входов 0 блока синхронизации часов.

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Устройство для отсчета времени | 1990 |

|

SU1784959A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для сопряжения ЦВМ с линиями связи | 1986 |

|

SU1462328A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство таймеров | 1983 |

|

SU1163309A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1580442A1 |

| УСТРОЙСТВО СБОРА И РЕГИСТРАЦИИ ПОЛЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

SU1825189A1 |

Изобретение относится к вычислительной технике и предназначено для непрерывного отсчета астрономического времени (функция часы), для фиксации заранее заданного момента времени (функция компаратора), для измерения истекшего времени работы процессора (функция таймер процессора) и для формирования продвигающих импульсов с заданной частотой следования, предназначенных для продвижения интервального таймера. Цель изобретения - расширение области применения устройства за счет синхронизации часов в мультипроцессорных системах и повышение точности формирования временных интервалов продвижения интервального таймера. Устройство содержит три двунаправленных коммутатора, первый счетчик, блок управления, блок сравнения, блок памяти информационных разрядов, блок памяти контрольных разрядов, коммутатор, регистр, блок предсказания переносов, блок предсказания четное™ байтов, таймер, блок формирования сигналов состояния устройства, элемент свертки по модулю два, элемент ИЛИ, элемент И-НЕ, дешифратор, второй счетчик, блок синхронизации часов. Устройство обеспечивает состояние стоп часов, синхронизацию часов и контроль синхронизации часов. 4 ил. ел с

Фие.1

ФШ

J5

A

Фиг.З

| Приспособление для перекатки колесных пар по железнодорожному пути | 1918 |

|

SU2665A1 |

| Техническое описание, ч.2 | |||

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| Устройство радиостанций с быстродействующими аппаратами Юза и Бодо | 1922 |

|

SU2130A1 |

| Техническое описание, ч.1 | |||

| Общие сведения | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1993-05-23—Публикация

1990-04-09—Подача