дои вычислительной ячейки. Коррелятор выполняет вычисление корреляционной функции М-разрядной входной последовательности x(i) с одноразрядными корреляционными коэффициентами

N-1

a(i) по формуле у(р) a(i)x(i+p) ,

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах, применяемых для цифровой обработки сигналов, работаю- 5 их в реальном масштабе времени, например, в радио и гидролокации 5 геоизике, медицине и других областях народного хозяйства.

Цель изобретения - повышение бы- Ю стродействия.

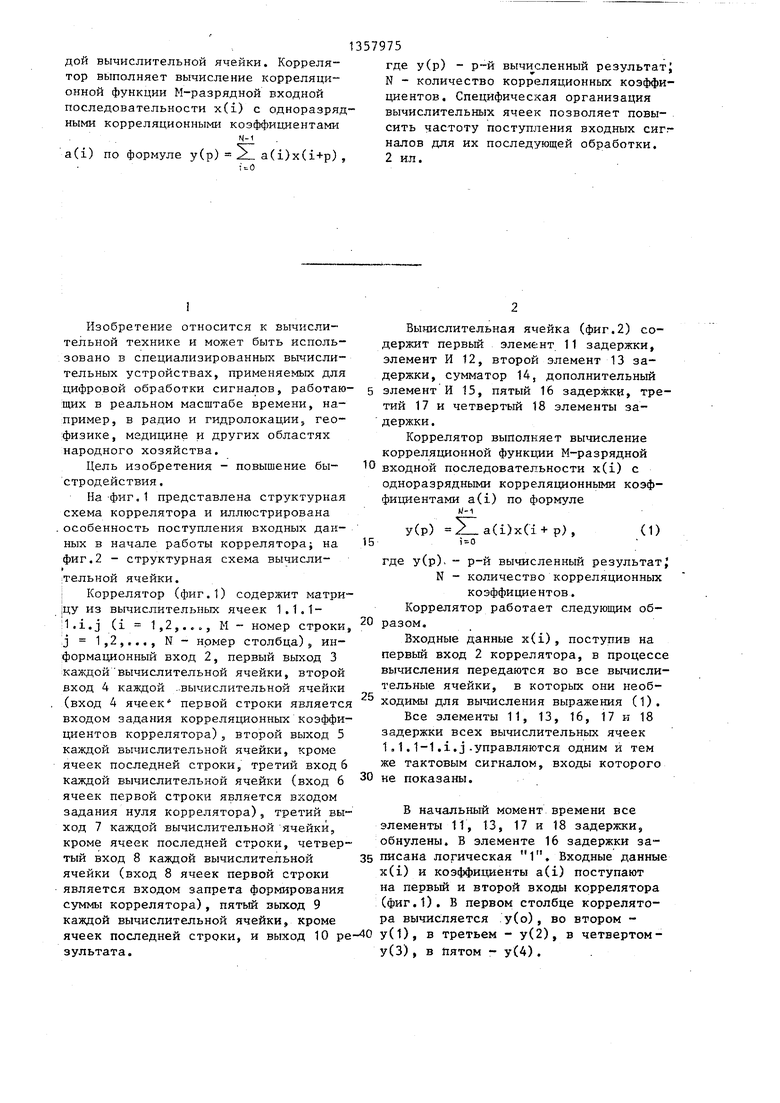

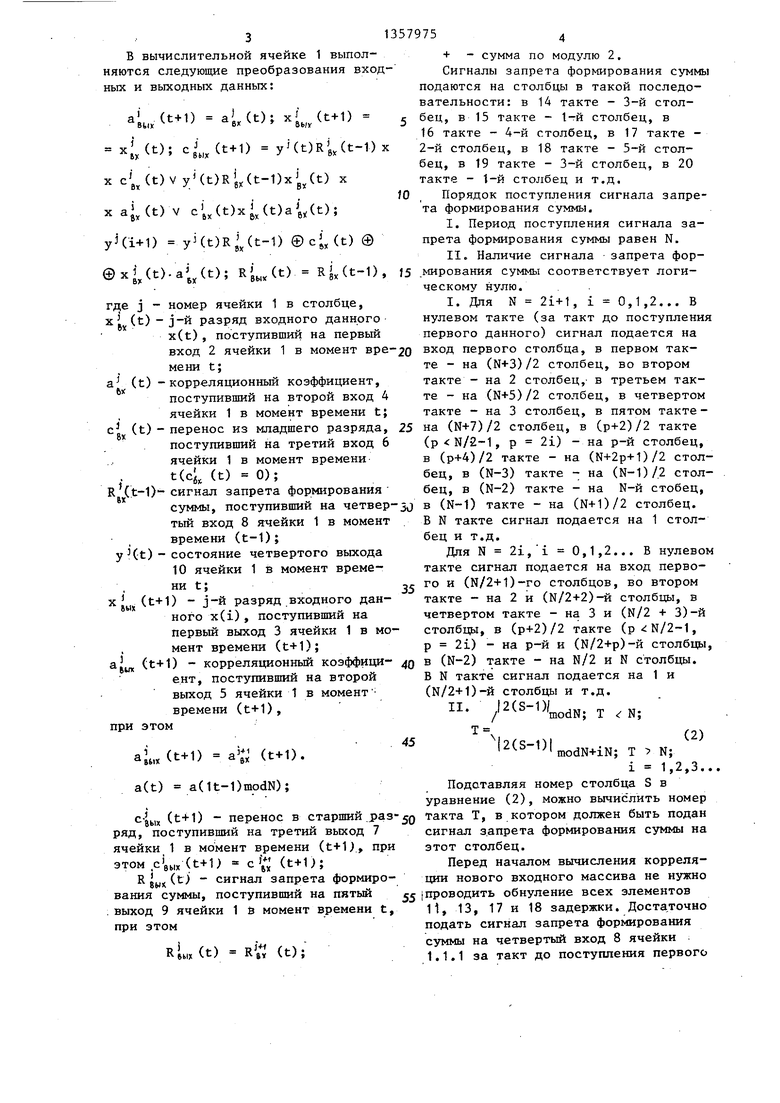

На-фиг, представлена структурная схема коррелятора и иллюстрирована особенность поступления входных данных в начале работы коррелятора; на 5 фиг.2 - структурная схема вычислительной ячейки.

Коррелятор (фиг.1) содержит матри- цу из вычислительных ячеек 1.1.1- 1.i.j (i 1,2,..., М - номер строки, j 1,2,,.., N - номер столбца), инормационный вход 2, первый выход 3 каждой вычислительной ячейки, второй вход 4 каждой ..вычислительной ячейки (вход 4 ячеек первой строки является входом задания корреляционных коэффициентов коррелятора), второй выход 5 каждой вычислительной ячейки, кроме ячеек последней строки, третий вход 6 каждой вычислительной ячейки (вход 6 ячеек первой строки является входом задания нуля коррелятора), третий вы- ход 7 каждой вычислительной ячейки, кроме ячеек последней строки, четвертый вход 8 каждой вычислительной 35 ячейки (вход 8 ячеек первой строки является входом запрета формирования суммы коррелятора) , пятый зьпсод 9 каждой вычислительной ячейки, кроме ячеек последней строки, и выход 10 зультата.

25

где у(р) - р-й вычисленный результатJ N - количество корреляционных коэффициентов. Специфическая организация вычислительных ячеек позволяет повысить частоту поступления входных сигналов для их последующей обработки. 2 ил.

Вычислительная ячейка (фиг.2) содержит первый элемент 11 задержки, элемент И 12, второй элемент 13 задержки, сумматор 14, дополнительный элемент И 15, пятый 16 задержки, третий 17 и четвертый 18 элементы задержки .

Коррелятор выполняет вычисление корреляционной функции М-разрядной входной последовательности x(i) с одноразрядными корреляционными коэффициентами a(i) по формуле

U

у(р) 2 a(i)x(i+р) ,

(1)

i 0

где у(р). - р-й вычисленный результатJ N - количество корреляционных коэффициентов.

Коррелятор работает следующим образом.

Входные данные x(i), поступив на первый вход 2 коррелятора, в процессе вычисления передаются во все вычислительные ячейки, в которых они необходимы для вычисления выражения (1).

Все элементы 11, 13, 16, 17 и 18 задержки всех вычислительных ячеек 1,1.1-1,i.j-управляются одним и тем же тактовым сигналом, входы которого не показаны.

Б начальный момент времени все элементы 11, 13, 17 и 18 задержки, обнулены. В элементе 16 задержки записана логическая 1. Входные данные x(i) и коэффициенты a(i) поступают на первый и второй входы коррелятора (фиг.1). В первом столбце коррелятора вычисляется у(о), во втором - у(1), в третьем - у(2), в четвертом- у(3), в Пятом - у(4).

3

В вычислительной ячейке няются следующие преобразоных и выходных данных:

, J

H.x(t+1) ai,(t)i x/,(t+1) xL(t); cL(t+1) y4t)R (t-1)x

IX

Вых

X c g(t) V y (t)Rj,(t-1)) X xa(t)v c j(t)x(t)(t); y4i+1) y4t)R(t-1) @c(,(t) ® ®xL(t).); ) RL(t-l),

B)i

БХ

I. Для N 21+1, i 0,1,2... В нулевом такте (за такт до поступления первого данного) сигнал подается на

тце j - номер ячейки 1 в столбце,

i (t) - j-й разряд входного данного x(t), поступивший на первый вход 2 ячейки 1 в момент вре-20 вход первого столбца, в первом так- мени t;те - на (N+3)/2 столбец, во втором

a,(t) -корреляционный коэффициент, такте - на 2 столбец, в третьем такбх

поступивший на второй вход 4 ячейки 1 в момент времени t;

те - на (N+5)72 столбец, в четвертом такте - на 3 столбец, в пятом такте с (t) - перенос из младшего разряда,25 на (N+7)/2 столбец, в Ср+2)/2 такте

поступивший на третий вход 6(p N/2-1, р 21) - на р-й столбец,

ячейки 1 в момент временив (р+4)/2 такте - на (N+2p+1)/2 столt(c4 (t) 0);бец, в (N-3) такте - на (N-1)/2 столR (t-1)- сигнал запрета формирования бец, в (N-2) такте - на N-й стобец, суммы, поступивший на четвер-зо в (N-1) такте - на (N+1)/2 столбец, тый вход 8 ячейки 1 в момент

. В N такте сигнал подается на 1 столбец и т.д.

времени (t-1);

уHt) - состояние четвертого выхода 10 ячейки 1 в момент времени t;

(t+1) - j-й разряд входного данного x(i), поступивший на первый выход 3 ячейки 1 в момент времени (t+1);

. В N такте сигнал подается на 1 столбец и т.д.

Для N 21,i 0,1,2... В нулево такте сигнал подается на вход первоэг го и (N/2+1)-ro столбцов, во втором такте - на 2 и (М/2+2)-й столбцы, в четвертом такте - на 3 и (N/2 + 3)-й столбцы, в (р+2)/2 такте (p :N/2-1, р 21) - на р-й и (N/2+p)-й столбцы

а (t+1) - корреляционный коэффици- 0 (N-2) такте - на N/2 и N столбцы.

ент, поступивший на второй выход 5 ячейки t в момент времени (t+1),

В N такте сигнал подается на 1 и (К/2+1)-й столбцы и т.д.

- / 2( Т .N;

при этом

а

l.,.(t-H) а : (t+l). a(t) a(lt-l)inodN);

{ых (t+1) - перенос в старший ра3-50 Такта Т, в котором должен быть подан

ряд, поступивший на третий выход 7 ячейки 1 в момент времени (t+1, при этом с вых (t+1) (t+O;

Rjy(t) - сигнал запрета формирования суммы, поступивший на питый : выход 9 ячейки 1 в момент времени t, при этом

сигнал запрета формирования суммы на этот столбец.

Перед началом вычисления корреляции нового входного массива не нужно 55 проводить обнуление всех элементов 11, 13, 17 и 18 задержки. Доста.точно подать сигнал запрета формирования суммы на четвертый вход 8 ячейки 1.1.1 за такт до поступления первого

RL (t)

RV (t);

+ - сумма no модулю 2.

Сигналы запрета формирования суммы подаются на столбцы в такой последовательности: в 14 такте - 3-й стол- бец, в 15 такте - 1-й столбец, в 16 такте - 4-й столбец, в 17 такте - 2-й столбец, в 18 такте - 5-й столбец, в 19 такте - 3-й столбец, в 20 такте - t-й столбец и т.д. Порядок поступления сигнала запрета формирования суммы.

I.Период поступления сигнала запрета формирования суммы равен N.

II.Наличие сигнала запрета фор- .мирования суммы соответствует логическому нулю.

I. Для N 21+1, i 0,1,2... В нулевом такте (за такт до поступления первого данного) сигнал подается на

вход первого столбца, в первом так- те - на (N+3)/2 столбец, во втором

те - на (N+5)72 столбец, в четвертом такте - на 3 столбец, в пятом такте бец, в (N-2) такте - на N-й стобец, в (N-1) такте - на (N+1)/2 столбец,

В N такте сигнал подается на 1 столбец и т.д.

Для N 21,i 0,1,2... В нулевом такте сигнал подается на вход первого и (N/2+1)-ro столбцов, во втором такте - на 2 и (М/2+2)-й столбцы, в четвертом такте - на 3 и (N/2 + 3)-й столбцы, в (р+2)/2 такте (p :N/2-1, р 21) - на р-й и (N/2+p)-й столбцы.

(N-2) такте - на N/2 и N столбцы.

5

В N такте сигнал подается на 1 и (К/2+1)-й столбцы и т.д.

- / 2( Т .N;

Т

N2(5-1)1

(2)

modN+lN; Т N;

1 1,2,3...

Подставляя номер столбца S в уравнение (2), можно вычислить номер

Такта Т, в котором должен быть подан

сигнал запрета формирования суммы на этот столбец.

Перед началом вычисления корреляции нового входного массива не нужно проводить обнуление всех элементов 11, 13, 17 и 18 задержки. Доста.точно подать сигнал запрета формирования суммы на четвертый вход 8 ячейки 1.1.1 за такт до поступления первого

данного нового массива, а на остальные столбцы коррелятора подавать сигналы запрета формирования суммы в соответствии с изложенным, что дает . возможность без перерыва приступать к обработке данных входного массива х , в то время когда в старших столб- цйх коррелятора заканчивается обработка данных предыдущего массива х.

Так .как длина столбца коррелятора М соответствует требуемой разрядности чисел преобразованной последователь™ мости, а при вычислении производится N суммирований, то количество значащих разрядов чисел входной последовательности должно быть на меньше, чем в числах преобразованной последовательности (JA - ближайшее большее целое).

Формула из обр.е тения

Коррелятор, содержаш;ий матрицу из- N столбцов (где-N - длина корреляционной последовательности) и М строк (где М - разрядность чисел входной последовательности) вычислительных ячеек, каждая из которых состоит из элемента И, сумматора, первого, второго, третьего и четвертого элементов задержки, причем первый .вход элемента И объединен с входом первого элемента задержки и является первым входом вычислительной ячейки, выход первого элемента задержки является первым выходом вычислительной ячейки, второй вход элемента И объединен с входом второго элемента задержки и является вторым входом вычислительной ячейки, выход второго элемента задержки является вторым выходом вычислительной ячейки, выход элемента И соединен с первым входом сумматора, второй вход которого является третьим входом вычислительной ячейки, первый и второй выходы сумматора соединены с входами третьего и четвертого эле

5 о

5

0

5

ментов задержки соответственно, выходы которых являются третьим и чет- .вертым выходами вычислительной ячейки соответственно, первый вход каждой вычислительной ячейки первого столбца является соответствующим информационным входом коррелятора, первые входы вычислительных ячеек каждого последующего столбца соединены с первыми выходами вычислительных ячеек предыдущего столбца соответственно, вторые входы всех вычислительных ячеек первой строки являются входами задания корреляционных коэффициентов коррелятора соответственно, третьи входы которых являются входами задания нуля соответственно, в каждом столбце вторые и третьи входы каждой последующей вычислительной ячейки столбца соединены с вторым и третьим выходами предьщущей вычислительной ячейки столбца соответственно, отличающийся тем, что, с целью повышения быстродействия, в каждую вычислительную ячейку введены дополнительный элемент И и пятый элемент задержки, вход которого, является четвертым входом вычислительной ячейки, выход пятого элемента задержки соединен с первым входом дополнительного элемента И и является пятьм выходом вычислительной ячейки, второй вход дополнительного элемента И соединен с выходом четвертого элемента задержки, выход дополнительного элемента И.подключен к третьему входу.сумматора, четвертые входы всех вычислительных ячеек первой строки являются входами запрета формирования суммы коррелятора, в каждом столбце четвертый вход каждой последующей вычислительной ячейки столбца соединен с пятым выходом предьщущей вычислительной ячейки, четвертый выход i,j-й (i 1,2s ... М, j 1,2,. .. N) вычислительной ячейки является соответствующим выходом результата кор релятора.

-п

I HРедактор О.Головач

Составитель Е.Ефимова

Техред М.Ходанич . Корректор В.Бутяга

Заказ 6001/51Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1985 |

|

SU1381539A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ АРИФМЕТИЧЕСКИХ ВЫЧИСЛЕНИЙ ПО ЗАДАННОМУ МОДУЛЮ | 2011 |

|

RU2477513C1 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Ячейка однородной вычислительной среды | 1987 |

|

SU1513471A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| РЕЦИРКУЛЯЦИОННЫЙ КОРРЕЛЯТОР РАЗРЕШЕНИЯ ФАЗОКОДОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2005 |

|

RU2283541C1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах, пpимeняe 6lПC для цифровой обработки сигналов, работающих в реальном масштабе времени, на- пример в геофизике, медицине. Цель изобретения - повьшение быстродействия. Коррелятор содержит матрицу из вычислительных ячеек 1.1.1-1.i.j (i 1,2М- номер строки, j 1, 2,..., N - номер столбца), входы 2, 4, 6, 8, выходы 3, 5, 7 9 Ю кая.оо ел со сд результат Фиг.1

| Мс.СаЪе, B.Arembepola и др | |||

| New algorithms and architectures for VLSI | |||

| Journal of Science .and Technology | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-12-07—Публикация

1985-01-24—Подача