00

ас

ел

со со

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах, применяемых для цифровой обработки сигнапов, работающих в реальном масштабе времени.

Цель изобретения - повышение быстродействия .

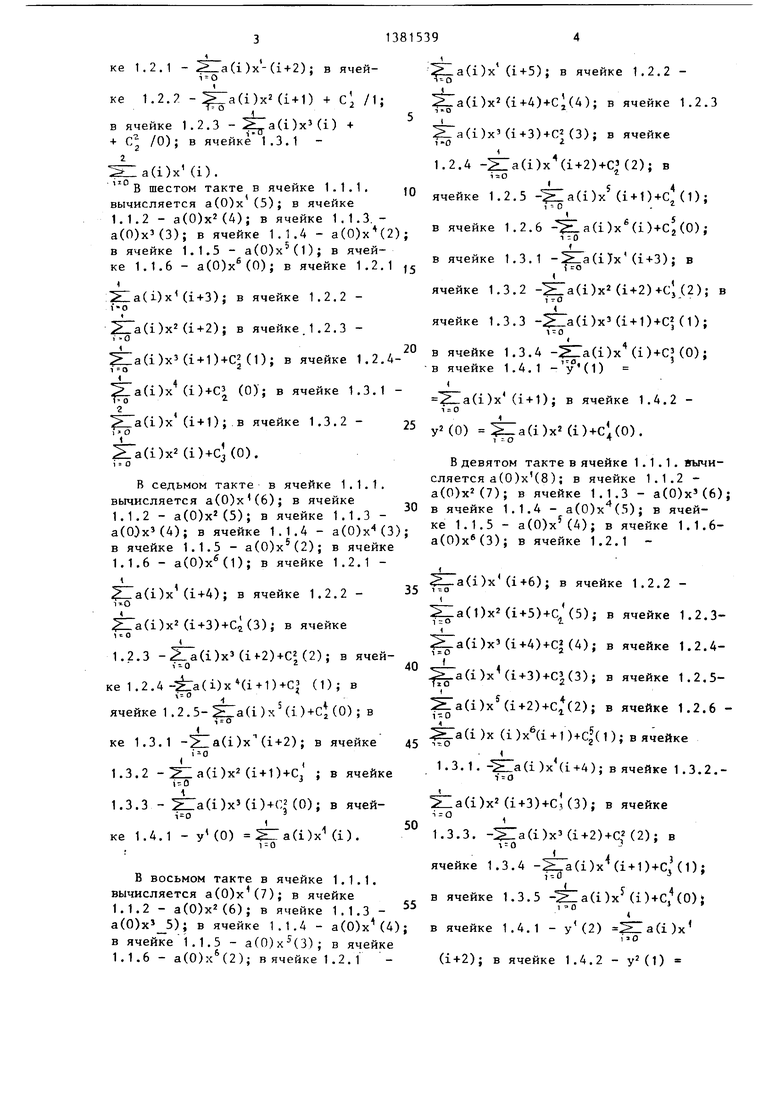

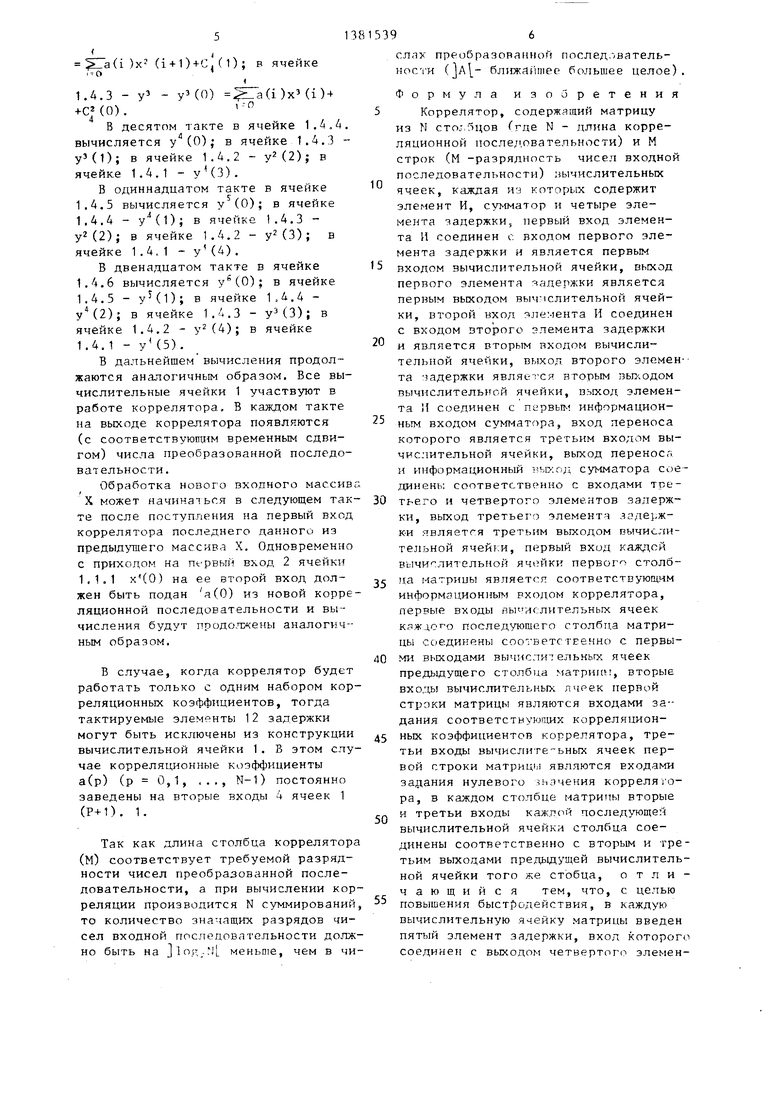

На фиг, 1 представлена структурная схема коррелятора; на фиг. 2 - схема вычислительной ячейки,

На фиг. 1 обозначено: - данные.. не входя1цие в результат; р - длина преобразованной последовательности,

Коррелятор (фиг. 1) содержит матрицу из вычислительных ячеек 1,1,1,- 1Л.. (i 1,2,.,,.М - номер строки, 1j 2,,..,N номер столбца), информационный вход 2, в каждой ячейке матрицы первый выход 3,второй вход 4, второй выход 5 (кроме ячеек последней строки), третий вход 6 (вход 6 ячеек первой строки является входом задания нуля коррелятора), третий выход 7 (кроме ячеек последней строки), четвертый вход 8 (входы 8 ячеек первой строки является вхо- дш- запрета формирования суммы кор- рехштора), четвертый выход 9 резуль-- тата,

Вычислительная Я /ейка (фиг. 2 содержит первый элемент 10 задержкн, элемент И 11, второй элемент 12 задержки, сумматор 13, третий, четвертый и пятый элементы 1, 15 и 16 задержки.

Коррелятор выполняет вычисление корреляционной функции М-разрядной входной последовательности X(i) с одноразрядными корреляционными коэффициентами a(i) по формуле

у(Р) где у(р)

м-

а(г) (i + р) ,

(1)

1 -- о

р-и вычислительный ре;ъуль-- тат; N - количество корреляционных

коэффициентов.

Рассмотрим работу коррелятора, Для наглядности будет описан случай N А, М 6, 1 , ,

В корреляторе входные данные Xd), поступив на первый вход коррелятора в процессе вычисления, передаются во все вычислите.пьные ячейки, в которых они необходиь-п., для вычис.пения выражения (1),

Все тактируемые элементы 10, 12, 1А, 15 и 16 задержки всех ячеек 1 управляются одним и тем же сигналом.

1а фиг, 1 и 2 условно не изображены тактируюп1ие входы ячеек 1 и всех так- тируаг-ых элементов 10, 12, 14, 15 и 16 задержки.

Входные данные X(i) и коэффициенты а(1) поступают на входы коррелятора., как показано на фиг. 1,

Так как направление передачи входных данных совпадает с направле- иием передачи результата, то нет необходимости проводить предварительное обнуление тактируемых элементов 10, 12, 14, 15 и 16 задержки.

0

5

Вычисления, проводимые в каждой ячейке 1. описаны с момента, когда в этой ячейке начинаются полезные вычисления„

информации в тактируемые: у.1гементы 10, 12, 14, 15 и 16 задержки осушествляется в начале каждого такта,

В оервом гакте в ячейке , 1. 1 . вычисляется одноразрядное произве- Л -;ние. ..ч(О)хЧо) J где х (0) - самый .шацший разряд х(0),

Bf; ;j7opo:v( такте в ячейке 1.1.1, гльиис 1 ле гея a(0)x ( 1)j р ччейке L Ь 2 a(0jx5 (0),

В третьем такте в ячейке 1,1,1, вычисляется а(0)х (2); в ячейке .. 1,:: - а(0)хЧ1); в ячейке 1,1,3 - а ГОх(0); в ячейке 1,2,1,1.(i)x (i),

В че -вертом такте в ячейке 1,1,1, вычигпяетсл а(0)х (3); в ячейке 1 ,-Ь 2 а(0)хЧ2); в ячейке 1,1,3 - .з(0)х (1); в ячейке 1,1,4 - а(0)х (0); к ячейке 1 . 2 , (i )х (i + 1) , в:

I а

1 ,

ячейке 1 ,2.2 (i)x2 (i)4-Cj(0) cl (0) - паренное, возникший в ячейке 2-го стопбца обрабатывающей, пар- вые разрядь) входных чисел при вычислении у (0) .

В пятом такте в ячейке 1.1,1. ВЫЧНС.Л-пвтся а(0): (4); в ячейке К 1,2 а(О)хЧЗ); в ячейке 1,1,3 - а(); в ячейке 1,j,4 - а(0)х (1). в ячейке К 1.5 - а(0)х (0) в ячей31381539 4

ке 1.2.1 - a(i)x -(i + 2); в ячей- a(i )х (i+5); в ячейке 1.2.2 1 -

ке 1.2.2 - (i)x4i-H) + a(i)x4i+4)+ci(4); в ячейке 1.2.3

-,0

в ячейке 1.2.3 - .. a(i)x (i) ,., ,. . „, х-ч

С- /0); в ячейкП.З. )x4i.3).q (3); в ячейке

a(i)x4i).1.2.A-±a(i).2).q(2); в

,iO

В шестом такте в ячейке 1.1.1.щ „ г /-ч 5/- « /,

ХГ.Ч --cs ячейке 1.2.5 (i)x (i + 1)+C,(l): вычисляется а(0)х (5); в ячейке{Т г

1.1.2 - а(0)х2 (4); в ячейке 1.1.3. - „ i -, .L ,- N «/-N /пч а(0)хЗ(3); в ячейке 1.1.4 - а(0)хП2); (О+Сг(0),.

в ячейке 1.1.5 - a(0)x4l); в ячей- - i о i « с / о

. . , ..«ч и/лч - т 4 В ячейке 1.3.1 - - я i.i ТУ (и-3); в

ке 1.1.6 - а(0)х (0); в ячейке 1.2.,--0

ila(i)); в ячейке 1.2.2 - 3.2 (i)x4i42) .с;.(2); в

±-a(i)x4i-2); в ячейке 1.2.3 - .З -±a(i ))q d) ;

,.0

f - f 4 f, - 1 Т В ячейке 1.3.4 (i)x (i)+CHO); - a(i)) (1); в ячейке 1.2.4- „ . / , з 2 -в ячейке 1.4.1-у (1)

1 О 4

a(i)x (i).C|(0); в ячейке 1.3.1 - .ц),- (i.) . , „,,,, ..г ETaCDx a.l);в ячейке 1.3.2 -25 у,о) fca(i )x4i )(0) .

1,

a(i)x4i)-t-c(0).„ , . 1

,. „ В девятом такте в ячейке 1.1.1. вычиDf. . . сляется а(0)х (8); в ячейке 1.1.2 В седьмом такте в ячейке 1.1.1. , . , .,. , , ..„ч ,//-ч

вь сляется а(О)хЧб); в ячейке, а(0)х (7); в ячейке .1 3 - а(0)х (6);

1.1.2 - а(0)хЧ5); в Ячейке 1.1.3 - 1.1.4 - а(0)х (5); в ячеи- а(0)хЗ(4); в ячейке 1.1.4 - а(0)х(3); ;. .L ячейке 1.1.5 - а(0)х (2); в ячейке

50. : :::е.;: а(0)х«(3); в ячейке 1.2.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1985 |

|

SU1357975A1 |

| Устройство для выполнения операций над матрицами | 1990 |

|

SU1741153A1 |

| Коррелятор | 1990 |

|

SU1730640A1 |

| Устройство для треугольного разложения ленточных матриц | 1988 |

|

SU1587540A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1802363A1 |

| Устройство для LU-разложения матриц | 1986 |

|

SU1401478A1 |

| КОНВЕЙЕРНЫЙ АРИФМЕТИЧЕСКИЙ УМНОЖИТЕЛЬ | 2013 |

|

RU2546072C1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Устройство для вычисления сумм произведений | 1988 |

|

SU1569826A1 |

| Коррелятор | 1989 |

|

SU1674154A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах, применяемых для цифровой обработки сигналов, работающих в реальном масштабе времени, например в геофизике, медицине. Цель изобретения - повышение быстродействия.Коррелятор выполняет вычисление корреляционной функции М-разрядной входной последовательности X(i) с одноразрядными корреляционными коэффициентами а(1). Специфическая организация вычислительных ячеек позволяет повысить частоту поступления входных сигналов для их последующей обработки. 2 ил. S (Л

,(1)x4i+5)+c45); в ячейке 1.2.3a(i)x4i+3)+C(3)i в ячейке °

4- ,(i)xMi+4)+q(4); в ячейке 1.2.41.2.3 -Z(i))+CH2); в ячей- °

1-0 40 . 4

, ,л ,., 4/- .4 п- (i)x4i-t-3)+CU3); в ячейке 1.2.5ке 1 .2.(i)x(i + 1)+Cj (1); вТГо 2

ячейке 1.(i))ci(0); в a(i))(2) ; в ячейке 1.2.6 i O

ке 1.3.1 -i:fl(i)x(i+2); в ячейке 45 ) (i )(i + О+С.С 1 ); в ячейке

(0

I,

0

1 0л оJ

: .

ячейке 1.3.4 (1)х (i + 1 )+q ( 1); В восьмом такте в ячейке 1.1.1.

вычисляется а(0)хЧ7); в ячейке в ячейке 1.3.5 (i )x4i )+€, (0) J

440 / f t f .Л..ЛSS1эл

4

в ячейке 1.1.5 - а(0)х(3); в ячейке °

4

a(i )х (i+1)+C(l); в ячейке

i-O

В десятом такте в ячейке 1.,4. вычисляется у (0); в ячейке 1.4.3 -- у (1); в ячейке 1.4.2 - у(2); в ячейке 1.4.1 - у ЧЗ) .

В одиннадцатом такте в ячейке

В двенадцатом такте в ячейке

В дальнейшем вычисления продолжаются аналогичным образом. Все вычислительные ячейки 1 участвуют в работе коррелятора, В каждом такте на выходе коррелятора появляются (с соответствуюпц{м временньп сдвигом) числа преобразованной последовательности.

Обработка нового входного массив X может начина1ься в следующем такте после поступления на первый вход коррелятора последнего данного из предыдущего массива X. Одновременно с приходом на первый вход 2 ячейки 1.1.1 х (0) на ее второй вход должен быть подан а(О) из новой корреляционной последовательности и вычисления будут продолжены аналогич-- ным образом.

В случае, когда коррелятор будет работать только с одним набором корреляционных коэффициентов, тогда тактируемые элементы 12 задержки могут быть исключены из конструкции вычислительной ячейки 1. В этом случае корреляционные коэффициенты а(р) (р О,1, ..., N-1) постоянно заведены на вторые входы 4 ячеек 1 (Р+1). 1.

Так как длина столбца коррелятора (М) соответствует требуемой разрядности чисел преобразованной последовательности, а при вычислении корреляции производится N суммирований то количество значащих разрядов чисел входной последовательности должно быть на , l меньше, чем в чи

сллх преобразованной послед,- ватель- нос ги ( ближаГииее большее целое).

Формула изооретения Коррелятор, содержащий матрицу из N сто;|3цов где N - длина корреляционной последовательности) и М строк (М -разрядность чисел входной последовательности) нычислительнмх ячеек, каждая из которых содержит элемент И, сумматор и четыре элемента задержки, первый вход элемента И соединен с входом первого элемента задержки и является первым

входом вычислительной ячейки, выход первого элемента задержки является первым выходом вычислительной ячейки, второй вхо/г элемента Н соединен с входом второго элемента задержки

и является вторым входом вычислительной ячейки, выход второго элемен-- та :задержки является вторым выходом вычислительной ячейки, выход элемента И соединен с первым информационным входом сумматора, вход переноса которого является третьим входом вычислительной ячейки, выход переноса и информационный ько;; сумматора сое- динень; соответственно с входами третьего и четвертого элементов задержки, выход третьего элемента ладерж- к-и является третьим выходом вычислительной ячейки, первый вход каждой вычислительной яч1Н1ки первог столб 13 матрицы является соответствующим информационньгч входом коррелятора, первые входы вычислительных ячеек каждог-о последующего столбца матрицы соединены соогветстЕвнно с первыми выходами вычислительных ячеек

предыдущего столбца матрикн, вторые входы вычислительных лчеек первой строки матрицы являются входами задания соответстнуюпшх корреляционнык коэффициентов коррелятора, третьи входы вычислите ьных ячеек первой строки матрицы являются входами задания нулевого значения корреляуо- ра, в каждом столбце матрипы вторые и третьи входы каждой последующей вычислительной ячейки столбца соединены соответственно с вторым и третьим выходами предыдущей вычислительной ячейки того же стобца, отличающийся тем, что, с целью

повышения быстродействия, в каждую вычислительную ячейку матрицы введен пятый элемент задержки, вход которого соединен с выходом четвертого элемен

та задержки, а выход является четвертым выходом вычислительной ячейки, второй информационный вход сумматора является четвертым входом вычислительной ячейки, четвертые входы всех вычислительных ячеек первого столбца являются входами запрета формирования суммы коррелятора.

C f oScfAfUff

f/t/ce с Л/47г/ /fас/гf o fey - f/yb Cfrrt с coo/rr fmc /n a ceP c/fff 4 /УСХЗ/У ЛУ/

в каждой строке матрицы четвертьт выход предыдущей вычислительной ячейки соединен с четвертым входом последующей вычислительной ячейки, четвертый выход последней вычислительной ячейки матрицы является соответствующим выходом результата коррелятора.

(pue.Z

| Me Cabe и др | |||

| New algorithus ahd architectures for VLSI GEC.- Journal of Science Technology, v | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

Авторы

Даты

1988-03-15—Публикация

1985-01-24—Подача