Изобретение, относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является повышение точности работы.

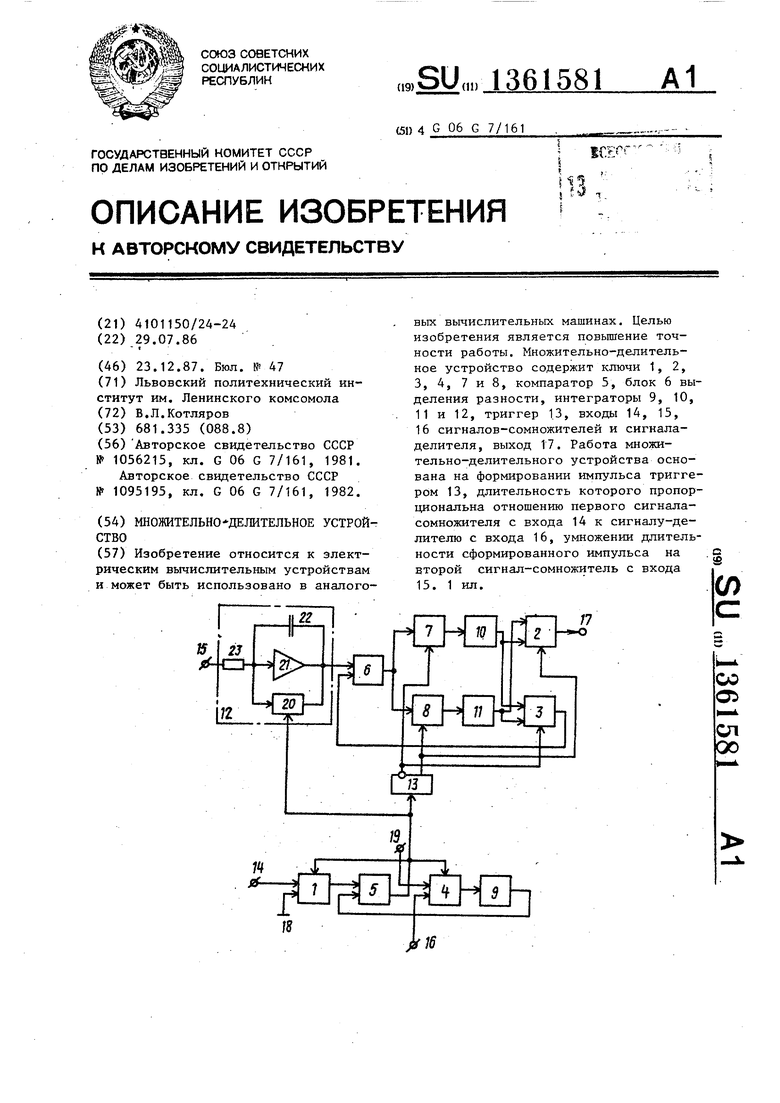

На чертеже изображена функциональная схема множительно-делитель- ного устройства.

На схеме обозначены двухпозицион- ные первый 1, второй 2, третий 3 и шестой 4 ключи, компаратор 5, блок 6 вьщеления разно сти, четвертый 7 и пятый 8 ключи, первый 9, второй 10, третий 11 и четвертый 12 интеграто- ры, триггер 13 и вход 14 первого сигнала-сомножителя, вход 15 второго сигнала-сомножителя, вход 16 сигналанию сиг-нала-делителя с входа 16,разрядный ключ 20 четвертого интегратора 12 размыкается и на выходе четвер( того интегратора 12, т.е. на выходе операционного усилителя 21, происходит рост напряжения со скоростью, пропорциональной напряжению второго сигнала-сомножителя с входа 15. Во

10 время обратного хода напряжения на выходе Интегратора 9 разрядный ключ 20 замыкается и накопительный конденсатор 22 разряжается. В момент замыкания разрядного ключа 20 перекиды15 вается триггер 13, вызывая срабаты- вание ключей 7 и 8 и ключей 2 и -3. При этом, когда в замкнутом состоянии находится ключ 7, второй ключ 2 подключает к выходу 17 выход интегратоделителя, выход 17, шина 18 нулевого 20 Рэ 11 а ключ 3 подключает к первому

потенциала, вход 19 задания напряжения смещения, разрядньш ключ 20,операционный усилитель 21, накопительный конденсатор 22 и масштабный резистор 23.

Множительно-делительное устройство работает следующим образом.

При наличии на выходе компаратора 5 напряжения, подключающего через ключ 1 сигнал первого сигнала-сомножителя с входа 14 к входу компаратора 5, ключ 4 подключает к входу первого интегратора 9 сигнал-делитель с входа 16. Напряжение на выходе первого интегратора 9 растет со скоростью 5 пропорциональной величине сигнала- делителя. Когда напряжение на выходе интегратора 9 достигнет уровня напряжения первого сигнала-сомножителя с

входу блока 6 выделения разности выход интегратора 10. Когда в замкнутом состоянии находится ключ 8 (ключ 7 в это время разомкнут), ключ 2

25 подключает к выходу 17 выход интегратора 10, а ключ 3 подключает к входу блока 6 выделения разности выход интегратора 11. Второй 10 и третий 11 интеграторы работают поочеред30 но в двух режимах: хранения информации и повторения выходного напряжения четвертого интегратора 12.

Режим хранения обеспечивается отсутствием заряда или разряда интег- (раторов 10 и 11 при разомкнутых ключах на их входах. Режим повторения обеспечивается подачей на входы интеграторов 10 и 11 через соответствующий замкнутый, ключ 7 или 8 с вывхода 14, компаратор 5 изменяет свое 40 хода блока 6 выделения разности уси- выходное напряжение, что приводит к ленного разностного напряжения между

напряжением на выходе интегратора 12 и напряжением на выходе второго 10

переключению ключей 1 и 4, благодаря чему вход компаратора 5 переключается к шине 18 нулевого потенциала, а

или третьего 11 интеграторов. Наприк входу первого интегратора 9 подклю- 45 Р когда замкнут ключ 7 и-ключ 3

подключает выход интегратора 10 . к входу блока 6 выделения разности, напряжение на выходе интегратора 10 должно быть равным напряжению на выходе интегратора 12. Если напряжение на вькоде интегратора 10 меньше напряжения на выходе интегратора 12, то на выходе блока 6 выделения разности появляется отрицательное напряжение, которое вызывает ускоренный рост напряжения на выходе интегратора 10. Если напряжение на выходе интегратора 10 больше, чем на выходе интегратора 12, на выходе бло

чается напряжение смещения с входа 19. Под воздействием напряжения смещения напряжения на выходе интегратора 9 уменьшается.с постоянной скоростью до нуля, после чего вновь происходит переключение компаратора 5 и напряжение на выходе первого интегратора 9 начинает линейно расти, пока не достигнет уровня напряжения первого сигнала-сомножителя с входа 14.

Б то время как происходит рост напряжения на выходе интегратора 9 с скоростью, пропорциональной напряжению сиг-нала-делителя с входа 16,разрядный ключ 20 четвертого интегратора 12 размыкается и на выходе четвертого интегратора 12, т.е. на выходе операционного усилителя 21, происходит рост напряжения со скоростью, пропорциональной напряжению второго сигнала-сомножителя с входа 15. Во

время обратного хода напряжения на выходе Интегратора 9 разрядный ключ 20 замыкается и накопительный конденсатор 22 разряжается. В момент замыкания разрядного ключа 20 перекидывается триггер 13, вызывая срабаты- вание ключей 7 и 8 и ключей 2 и -3. При этом, когда в замкнутом состоянии находится ключ 7, второй ключ 2 подключает к выходу 17 выход интеграто5

входу блока 6 выделения разности выход интегратора 10. Когда в замкнутом состоянии находится ключ 8 (ключ 7 в это время разомкнут), ключ 2

5 подключает к выходу 17 выход интегратора 10, а ключ 3 подключает к входу блока 6 выделения разности выход интегратора 11. Второй 10 и третий 11 интеграторы работают поочеред0 но в двух режимах: хранения информации и повторения выходного напряжения четвертого интегратора 12.

Режим хранения обеспечивается отсутствием заряда или разряда интег- (раторов 10 и 11 при разомкнутых ключах на их входах. Режим повторения обеспечивается подачей на входы интеграторов 10 и 11 через соответствующий замкнутый, ключ 7 или 8 с выили третьего 11 интеграторов. Напри0

5

подключает выход интегратора 10 . к входу блока 6 выделения разности, напряжение на выходе интегратора 10 должно быть равным напряжению на выходе интегратора 12. Если напряжение на вькоде интегратора 10 меньше напряжения на выходе интегратора 12, то на выходе блока 6 выделения разности появляется отрицательное напряжение, которое вызывает ускоренный рост напряжения на выходе интегратора 10. Если напряжение на выходе интегратора 10 больше, чем на выходе интегратора 12, на выходе блока 6 выделения разности появляется положительное напряжение, способствующее з. меньшению напряжения на выходе интегратора 10.

Поскольку длительность импульса, поступающего с выхода триггера 13 и размыкающего разрядный ключ 20, пропорциональна напряжению первого сигнала-сомножителя с входа 14 и обратно пропорциональна напряжению сигнала-делителя с входа 16,.то в момент окончания этого импульса,т.е. перед самым переключением триггера 13, напряжение на выходе-интегратора 12 пропорционально длительности выходного импульса триггера 13, умноженной на напряжение второго сигнала-сомножителя с входа 15. Поскольку выходное напряжение на интет раторах 10 и 11 повторяет выходное напряжение интегратора 12 перед переключением триггера 13 и не зависит от их постоянных времени, то на выходе 17 не происходит изменений напряжения при переключении второго ключа 2 из- за неодинаковости постоянных времени интеграторов 10 и 11.

Формула изобретения зо

Множительно-делительное устройство, содержащее компаратор, к первому входу которого подключен выход первого ключа, к второму входу компаратора подключен выход первого интегратора, выход компаратора соединен с управляющим входом первого ключа и счетным входом триггера, прямой выход которого подключен к управляющему входу второго ключа, инверсный выход триггера подключен к управляющему входу третьего ключа, второй и третий интеграторы, к входам которых подключены выходы соответственно четСоставитель О.Отраднов Редактор И.Николайчук Техред А.Кравчук Корректор М.Пожо

Заказ 6293/50 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

10

61581

вертого и пятого ключей, сигнальные входы которых объединены, выходы второго и третьего.интеграторов подключены соответственно к первым сигнальным входам второго и третьего ключей, первый сигнальньш вход первого ключа является входом первого сигнала-сомножителя устройства, и шестой ключ, выход которого соединен с входом первого интегратора, отличающееся тем, что.

с целью повьшения точности, в него введены четвертый интегратор и блок выделения разности, причем первый, второй, третий и шестой ключи выполнены двухпозиционными, первый вход блока выделения разности соединен с выходом третьего ключа, выход четвертого интегратора подключен к второму входу блока вьщеления разности, выход которого соединен с объединенными сигнальными входами четвертого и пятого ключей, выход второго интегратора подключен к второму сиго

5

0

нальному входу третьего ключа, выход третьего интегратора подключен к второму сигнальному входу второго ключа, инверсный выход триггера соединен с управляющим входом четвертого ключа, управляющий вход пятого ключа подключен к прямому выходу триггера, счетный вход которого соединен с входом сброса четвертого интегратора, второй сигнальный вход первого ключа подключен к шине нулевого потенциала, первый сигнальный вход шестого ключа является входом задания напряжения смещения устройства, управляющий вход шестого ключа подключен к выходу компаратора, вход четвертого интегратора является входом второго сигнала- сомножителя устройства, входом сигнала-делителя которого является второй сигнальный вход шестого ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель разности длительностей наносекундных интервалов | 1985 |

|

SU1290244A1 |

| Множительно-делительное устройство | 1978 |

|

SU1095195A1 |

| Множительно-делительное устройство | 1974 |

|

SU554540A1 |

| Преобразователь угла поворота вала в код | 1981 |

|

SU972541A1 |

| Цифровой измеритель величины отклонения скорости от заданной | 1981 |

|

SU953570A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1124346A1 |

| Датчик разности фаз | 1980 |

|

SU962817A1 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Преобразователь сигнала тензомоста в интервал времени | 1987 |

|

SU1580260A1 |

| Измеритель нелинейности амплитудной характеристики радиоэлементов | 1986 |

|

SU1370615A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности работы. Множительно-делитель- ное устройство содержит ключи 1, 2, 3, 4, 7 и 8, компаратор 5, блок 6 выделения разности, интеграторы 9, 10, 11 и 12, триггер 1,3, входы 14, 15, 16 сигналов-сомножителей и сигнала- делителя, выход 17. Работа множи- тельно-делительного устройства основана на формировании импульса триггером 13, длительность которого пропорциональна отношению первого сигнала- сомножителя с входа 14 к сигналу-делителю с входа 16, умножении длительности сформированного импульса на второй сигнал-сомножитель с входа 15. 1 Ш1. с (Л со О5 СП 00

| Время-импульсное множительное устройство | 1981 |

|

SU1056215A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Множительно-делительное устройство | 1978 |

|

SU1095195A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1986-07-29—Подача