интеграторов объединены и подключены к выходу устройства.

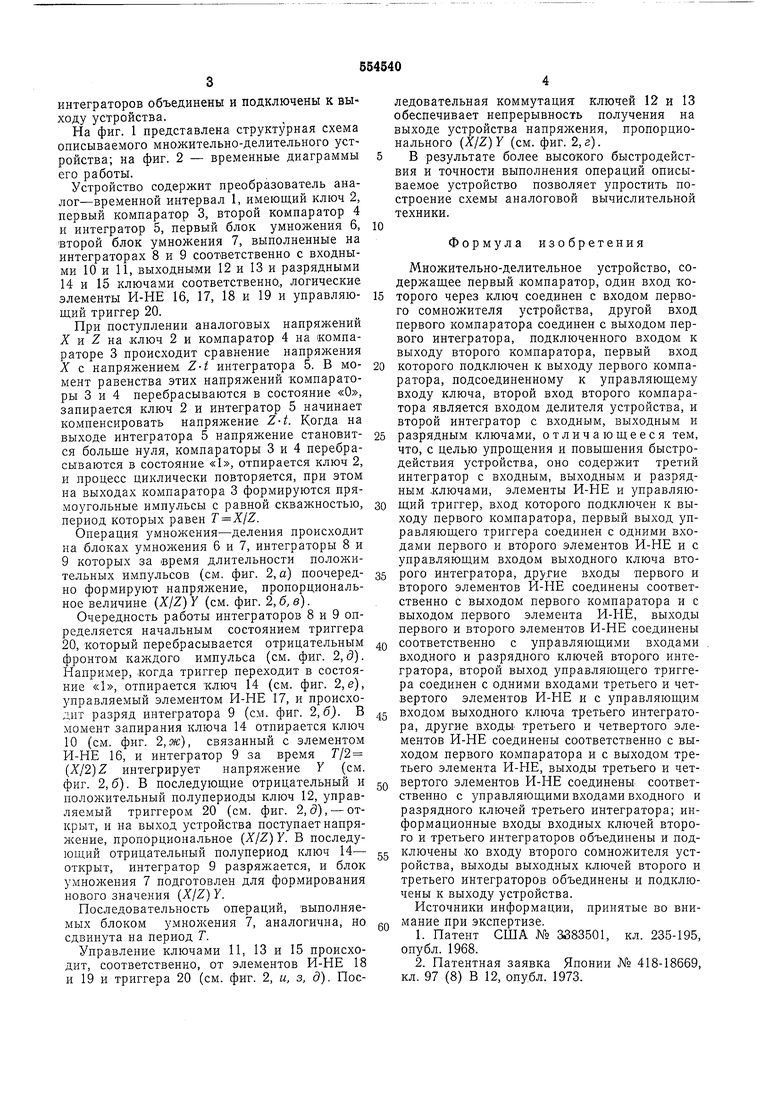

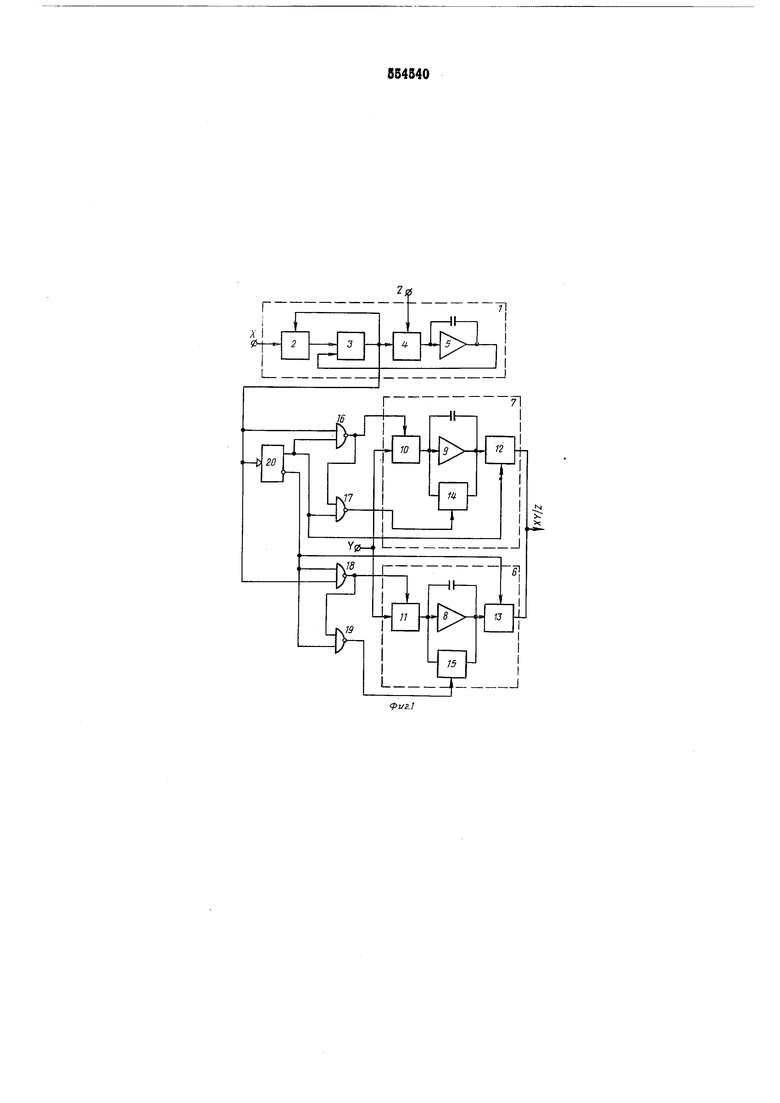

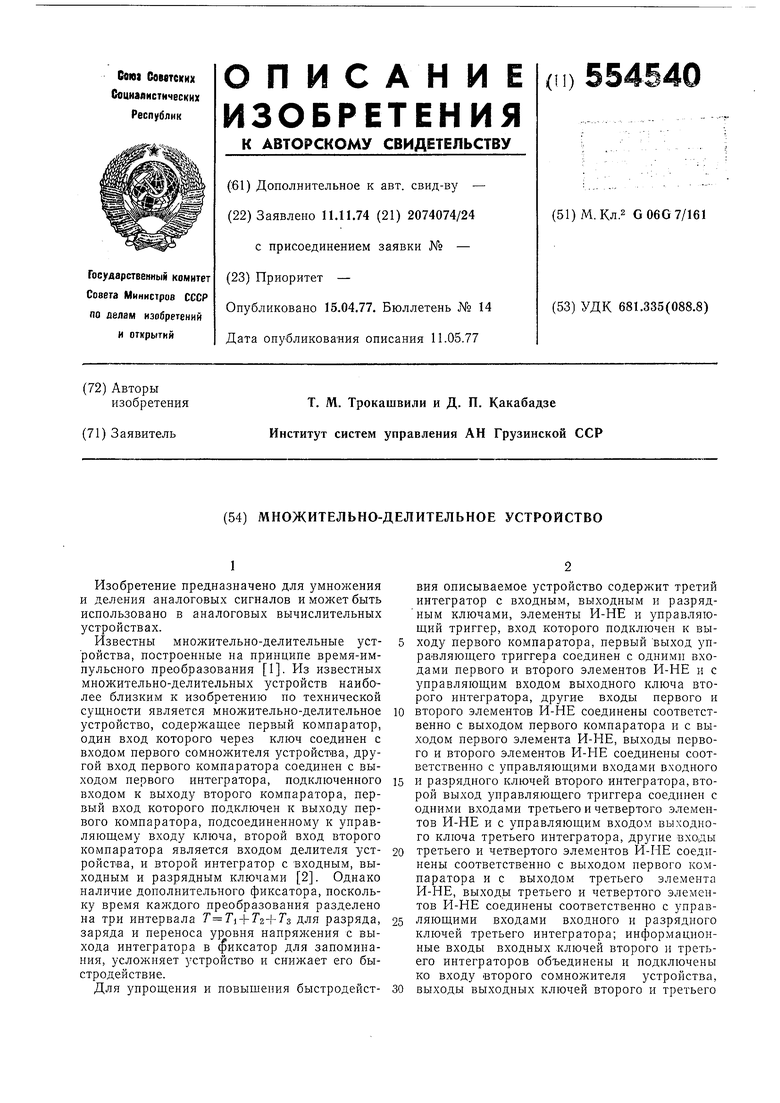

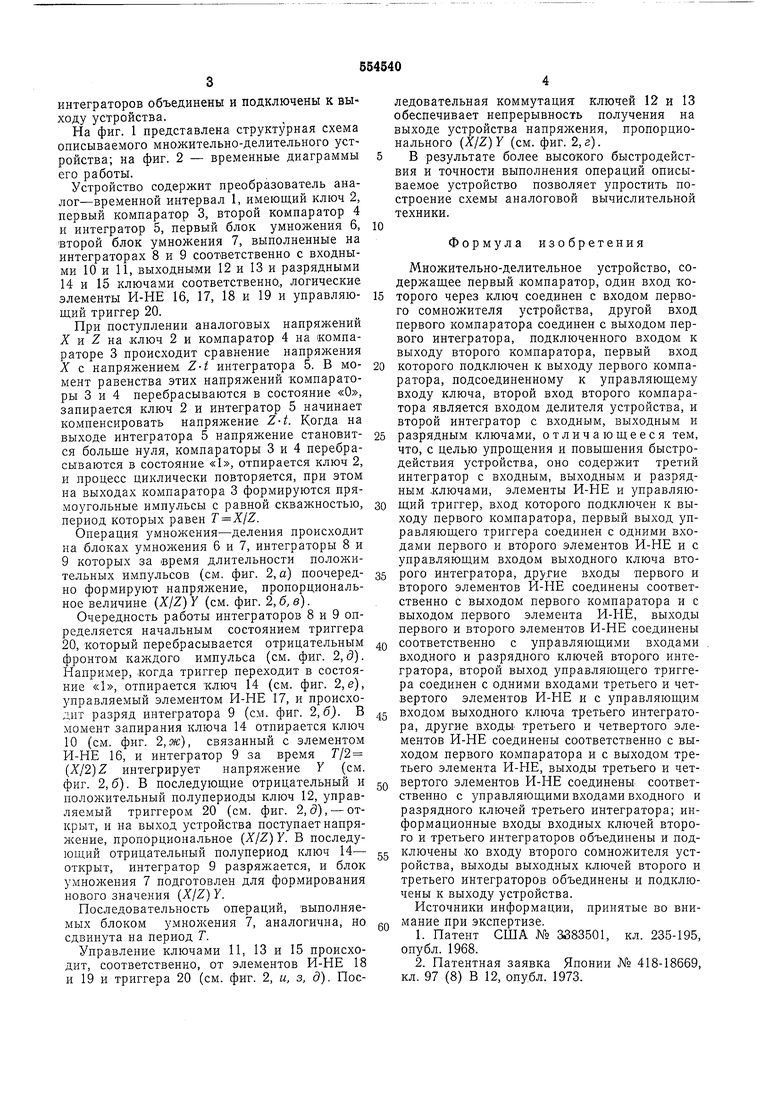

На фиг. 1 представлена структурная схема описываемого множительно-делительного устройства; на фиг. 2 - временные диаграммы его работы.

Устройство содержит преобразователь аналог-временной интервал 1, имеющий ключ 2, первый компаратор 3, второй компаратор 4 и интегратор 5, первый блок умножения 6, второй блок умножения 7, выполненные на интеграторах 8 и 9 соответственно с входными 10 и 11, выходными 12 и 13 и разрядными 14 и 15 ключами соответственно,, логические элементы И-НЕ 16, 17, 18 и 19 и управляющий триггер 20.

При поступлении аналоговых напряжений X и Z на ключ 2 и компаратор 4 на компараторе 3 происходит сравнение напряжения X с напряжением Z-t интегратора 5. В момент равенства этих напряжений компараторы 3 и 4 перебрасываются в состояние «О, запирается ключ 2 и интегратор 5 начинает компенсировать напряжение Z-t. Когда на выходе интегратора 5 напряжение становится больше нуля, компараторы 3 и 4 перебрасываются в состояние «1, отпирается ключ 2, и процесс циклически повторяется, при этом на выходах компаратора 3 формируются прямоугольные импульсы с равной скважностью, период которых равен T XIZ.

Операция умножения-деления происходит на блоках умножения 6 н 7, интеграторы 8 и

9которых за время длительности положительных импульсов (см. фиг. 2, а) поочередно формируют напряжение, пропорциональное величине (X/Z)Y (см. фиг. 2, б, в).

Очередность работы интеграторов 8 и 9 определяется начальным состоянием триггера 20, который перебрасывается отрицательным фронтом каладого импульса (см. фиг. 2,5). Например, когда триггер переходит в состояние «1, отпирается ключ 14 (см. фиг. 2, е). Заправляемый элементом И-НЕ 17, и происходит разряд интегратора 9 (см. фиг. 2,6). В момент запирания ключа 14 отпирается ключ

10(см. фиг. 2,ж), связанный с элементом И-НЕ 16, и интегратор 9 за время 7/2 (XJ2)Z интегрирует напряжение Y (см. фиг. 2,6). В последующие отрицательный и положительный полупериоды ключ 12, управляемый триггером 20 (см. фиг. 2,д), - открыт, и на выход устройства поступает напряжение, пропорциональное (X/Z) У. В последующий отрицательный полупериод ключ 14- открыт, интегратор 9 разряжается, и блок умножения 7 подготовлен для формирования нового значения (X/Z) Y.

Последовательность операций, выполняемых блоком умножения 7, аналогична, но сдвинута на период Т.

Управление ключами И, 13 н 15 происходит, соответственно, от элементов И-НЕ 18 и 19 и триггера 20 (см. фиг. 2, и, з, д). Последовательная коммутация: ключей 12 н 13 обеспечивает непрерывность получения на выходе устройства напряжения, пропорционального (X/Z)Y (см. фиг. 2, г).

В результате более высокого быстродействия и точности выполнения операций описываемое устройство позволяет упростить построение схемы аналоговой вычислительной техники.

Формула изобретения

Множительно-делительное устройство, содержащее первый компаратор, один вход которого через ключ соединен с входом первого сомножителя устройства, другой вход первого компаратора соединен с выходом первого интегратора, подключенного входом к выходу второго компаратора, первый вход

которого подключен к выходу первого компаратора, подсоединенному к управляющему входу ключа, второй вход второго компаратора является входом делителя устройства, и второй интегратор с входным, выходным и

разрядным ключами, отличающееся тем, что, с целью упрощения и повышения быстродействия устройства, оно содержит третий интегратор с входным, выходным и разрядным ключами, элементы И-НЕ и управляюЩий триггер, вход которого подключен к выходу первого компаратора, первый выход управляющего триггера соединен с одними входами первого и второго элементов И-НЕ и с управляющим входом выходного ключа второго интегратора, другие входы первого и второго элементов И-НЕ соединены соответственно с выходом первого компаратора и с выходом первого элемента И-НЕ, выходы первого и второго элементов И-НЕ соединены

соответственно с управляющими входами входного и разрядного ключей второго интегратора, второй выход управляющего триггера соединен с одними входами третьего и четвертого элементов И-НЕ и с управляющим

входом выходного ключа третьего интегратора, другие ВХОДЫ третьего и четвертого элементов И-НЕ соединены соответственно с выходом первого компаратора и с выходом третьего элемента И-НЕ, выходы третьего и четвертого элементов И-НЕ соединены соответственно с управляющими входами входного и разрядного ключей третьего интегратора; информационные входы входных ключей второго и третьего интеграторов объединены и подключены ко входу второго сомножителя устройства, выходы выходных ключей второго и третьего интеграторов объединены и подключены к выходу устройства.

Источники информации, принятые во внимание нри экспертизе.

1.Патент США № 3383501, кл. 235-195, опубл. 1968.

2.Патентная заявка Японии № 418-18669, кл. 97 (8) В 12, опубл. 1973.

.

,.

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1978 |

|

SU1095195A1 |

| Множительно-делительное устройство | 1978 |

|

SU1005081A1 |

| Экспоненциальный функциональный преобразователь | 1977 |

|

SU690506A1 |

| Множительно-делительное устройство | 1986 |

|

SU1361581A1 |

| Множительно-делительное устройство | 1978 |

|

SU723596A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1993 |

|

RU2110091C1 |

| Устройство для умножения | 1977 |

|

SU686035A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1124346A1 |

| Регулятор энергетического цикла сварки | 1987 |

|

SU1512736A1 |

Авторы

Даты

1977-04-15—Публикация

1974-11-11—Подача