Предлагаемое устройство относится к вычислительной технике и предназначено для распределения задач между процессорами в мультипроцессорных системах.

Цель изобретения - увеличение вероятности обслуживания задач за счет учета требуемого объема памяти при обслуживании задач,

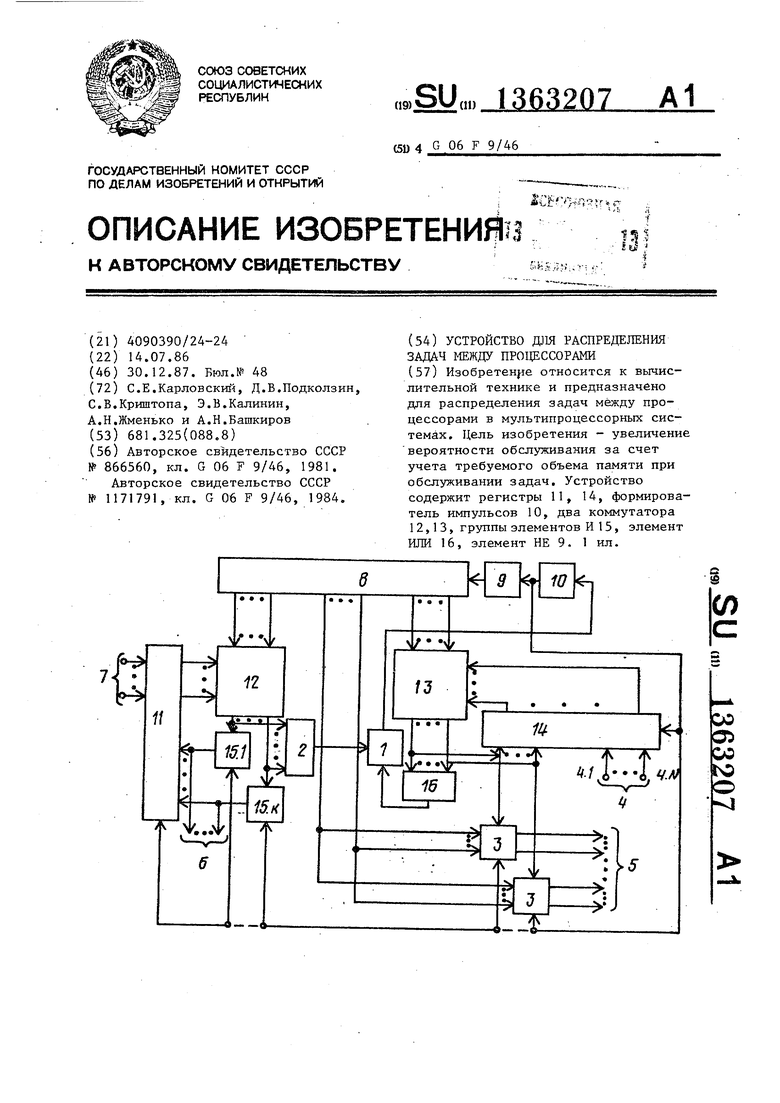

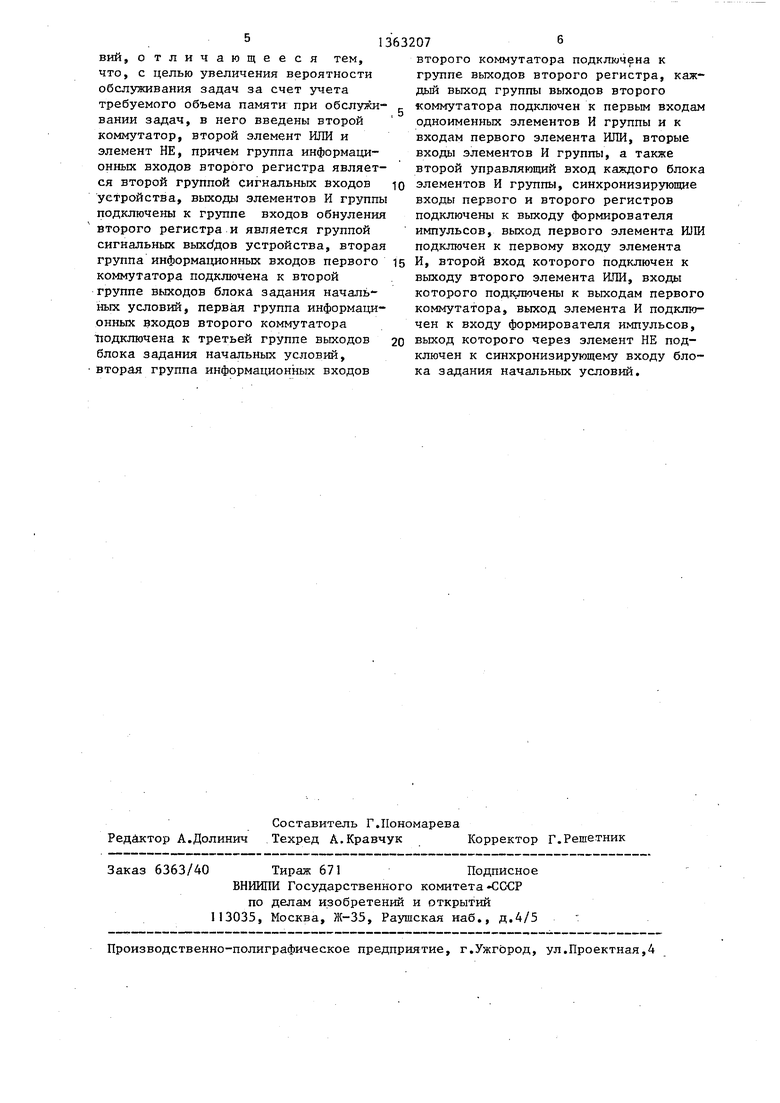

На чертеже приведена структурная схема устройства.

Устройство содержит элемент И 1, элемент ИЛИ 2, блоки элементов И 3, группу сигнальных входов 4 устрой- ства, группу информационных выходов 5 устройства, группу сигнальных выходов 6 устройства, группу сигнальных входов 7 устройства, блок 8 задания начальных условийj .элемент НЕ 9, формировав т ель 10 импульсов, регистр 11, коммутаторы 12, 13, регистры 14, группу элементов И 15, элемент ИЛИ 16.

Устройство работает следуюгцим образом.

В исходном состоянии информация н группах входов 1, 2 и 3 устройства и на группах входов 4 и выходов 6 отсутствует. Регистры 11 и 14 обну- лены. На группе выходов 6 устанавливаются нулевые сигналы. Нулевой сигнал на выходе элемента ИЛИ 2 действует на второй вход элемента И 1, на выходе которого нулевой сигнал действует на вход формирователя 10. В момент пуска устройства нулевой сигнал с вых ода формирователя 10 поступает на вход элемента НЕ 9, где инвертируется. Единичный сигнал с выхода элемента HIi 9 поступает на синхронизирующий вход регистра 8, разрешая запись на регистр 8.

Программа-планировщик операционно системы (ППОС) выдает информацию о задачах в блок 8 группы, npn4ek выдается информация о количестве потребных страниц памяти для решения задачи, номер задачи, количество потребных для ее решения процессоров. Количество потребных для решения задачи процессоров выдается в позиционном коде. Количество потребных для решения задачи страниц оператив- ной памяти выдается в .позиционном коде.

На группу входов поступают сигнал готовности процессоров к обслуживанию задачи, Единичиный сигнал означает то, что процессор готов приступить к обслуживанию задачи, а нулево процессор занят дообслужяванием другой задачи. Количество свободных для обслуживания задачи процессоров выдается в позиционном -коде.

Информация о количестве страниц оперативной памяти, готовых к обслуживанию задачи, поступает на группу входов 7 в позиционном коде.

При работе данного устройства распределения задач между процессора ми с учетом потребного процессорам объема памяти возможны 4 случая:

1)объем свободной памяти не меньше требуемого, количество свободных процессоров больше или равно.требуемому;

2)объем свободной памяти меньше требуемого 5количество свободных процессоров меньше требуемого;

3)объем свободной памяти меньше требуемого,количество свободных процессоров больше или равно требуемому;

4)объем свободной памяти не меньше требуемого, количество свободных процессоров меньше требуемого.

Для объяснения работы устройства целесообразно рассмотреть первый и третий: случаи.

Формирователь 10 предназначен для выработки управляющего импульса и блокировки через элемент НЕ 9 блока 8 на время длительности цикла распределения задачи по свободным процессорам с учетом требуемого объема памяти. В исходном состоянии на входе формирователя действует нулевой сигнал с выхода закрытого элементу И 1. На выходе формирователя 10 действует нулевой сигнал, который действует на синхронизирующие входы регистра 14, синхронизирующий вход регистра 11, не изменяя их состояния и не блокируя запись информации, а также на входы блоков элементов И 3, запирая их. Такое состояние формирователя сохранится до момента, когда в системе будет иметься требуемое количество свободных процессоров и страниц оперативной памяти для решения данной задачи, т.е. когда элемент И 1 откроется и на вход формиро ват еля 10 поступит единичньш сигнал. Единичный сигнал со входа формирователя поступает на выход формирователя 10, с которого он подается на

вход элемента НЕ 9 и синхронизирующие входы регистра 1А и регистра 11, Единичный сигнал подается также на вход1 1 блоков элементов И 3 и на вторые входы элементов И 15. По положительному переходу единичного сигнала в регистре 11 и в регистре 14 происходит динамическое стирание информации по распределенной задаче5 распре- ю свободной памяти меньше требуемого,

деление которой происходит через группу элементов И 15 и группу блоко элементов И 19 по разрешающему еди-- ничному сигналу с формирователя 10. По окончании цикла распределения формирователь 10 возвращается в исходное-нулевое состояние. При этом с выхода элемента НЕ 9 на вход синхронизации блока 8 поступает единичный сигнал, по переднему фронту которого происходит динамическая запись новых данных в блок 8

На входы ком1 -1утаторов 12513 поступают позиционные коды, количества потребных для решения задачи процессоров (страниц оперативной памяти).

Единичные сигналы с выходов коммутатора 13 поступают на входы элемента ИЛИ 16, на управляющие входы соответствующего блока элементов И 3 и на и 1формационные входы регистра 14 в те разряды, которые соответствуют назначенным на распределение задачам

Единичные сигналы с выходов коммутатора 12 поступают на первые входы элементов И 15 и на входы элемента ИЛИ 2, на выходе которого появляется единичный сигнал5 поступающий на второй вход элемента И 1, на первом входе которого действует единичный сигнал с выхода элемента ИЛИ 16. Следовательно, на выходе элемента И 1 и на входе формирователя 10 будет действовать единичный сигнал. По

единичному сигналу на входе формиро- 45 группы выходов первого регистра

ватель сформирует единичньй сигнал на выходе, которьй поступает на входы блоков элементов ИЗ. Блоки элементов ИЗ, соответствуюирие назна- чаг1ным для решения задачи процессорам, открываются и код номера задачи из блока 8 поступает в назначенные, процессоры, которые начинают решение задачи. По окончании цикла распределения единичный сигнал .с выхода формирователя 10 снимается и, если требования задачи полностью удовлетворе- ны на выходе элемента НЕ 9 появляется единичный сигнал, который подается

на тактовый вход регистра 14, на третьи входы блоков элементов И 3, на вторые входы элементов И 15 и на тактовый вход регистра 11, разрешая обнуление информации по задаче и сведений о состоянии процессоров системы в регистре 14,

Рассмотрим случай, когда объем

количество свободных процессоров больше или равно требуемому. Тогда работа устройства будет аналогична до того момент а, пока коммутаторы

12, 13 не выдают единичные сигналы на свои выходы. В этом случае единичный сигнал на выходе элемента И 1 формироваться не будет и формирова тель не будет формировать импульс,

Следовательно, обнуление информации в блоке 8, регистре 11 не будет. Блоки элементов ИЗ, соответствующие назначенным для решения задачи процессором, будут заперты нулевым сигналом

по управляющим входам, соединенным с выходом формирователя 10. Код номера из блока 8 на процессоры поступа1ь не будет, .Задача остается не обслуженной до изменения состояния системы, т.е. до тех пор, пока в регистре 11 не будет записано требуемое число страниц оперативной памяти.

Формула изобретения Устройство для распределения загдач между процессорами, содержащее два регистра, элемент И, группу блоков элементов И, блок задания начальных условий, формирователь импульсов, первьй коммутатор, первьш элемент ИПИ, группу элементов И, причем группа информационных входов первого регистра является первой группой сигнальных входов устройства, выходы

соединены с одноименными входами первой группы информационных входов первого коммутатора, выходы группы выходов первого коммутатора соединены с одноименными входами группы входов обнуления первого регистра и с первыми управляющими входами одноименных блоков элементов И группы, группы выходов блоков элементов И

группы являются группами информационных выходов устройства, группы инфорационных входов блоков элементов И группы соединень с первой группой выходов блока задания начальных уелоВИЙ, отличающееся тем, что, с целью увеличения вероятности обслуживания задач за счет учета требуемого объема памяти при обслуживании задач, в него введены второй коммутатор, второй элемент ИЛИ и элемент НЕ, причем группа информационных входов второго регистра является второй группой сигнальных входов устройства, выходы элементов И группы подключены к группе входов обнуления второго регистра и является группой сигнальных вькс/дов устройства, вторая группа информа1щонных входов первого коммутатора подключена к второй группе выходов блока задания начальных условий, первая группа информаци онных входов второго коммутатора Подключена к третьей группе выходов блока задания начальных условий, вторая группа информационных входов

ю

632076

второго коммутатора подключена к группе выходов второго регистра, каж- дьш выход группы выходов второго коммутатора подключен к первым входам одноименных элементов И группы и к входам первого элемента ИЛИ, вторые входы элементов И группы, а также второй управляющий вход каждого блока элементов И группы, синхронизирующие входы первого и второго регистров подключены к выходу формирователя импульсов, выход первого элемента ШШ подключен к первому входу элемента 15 И, второй вход которого подключен к выходу второго элемента ИЛИ, входы которого подключены к вькодам первого коммутатора, выход элемента И подключен к входу формирователя импульсов, выход которого через элемент НЕ подключен к синхронизирующему входу блока задания начальных условий.

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1988 |

|

SU1636846A1 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1751760A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1569831A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Устройство для распределения задач между процессорами | 1984 |

|

SU1171791A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1543404A1 |

| Многоканальное устройство для включения резервных радиостанций | 1990 |

|

SU1748299A1 |

| Многопроцессорная вычислительная система | 1991 |

|

SU1837309A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524052A1 |

| Устройство для распределения задач между процессорами | 1984 |

|

SU1242950A1 |

Изобретен|1е относится к вычислительной технике и предназначено для распределения задач между процессорами в мультипроцессорных системах. Цель изобретения - увеличение вероятности обслуживания за счет учета требуемого объема памяти при обслуживании задач. Устройство содержит регистры 11, 14, формирователь импульсов 10, два коммутатора 12,13, группы элементов И 15, элемент ИЛИ 16, элемент НЕ 9. 1 ил.

Авторы

Даты

1987-12-30—Публикация

1986-07-14—Подача