(21)4412458/24-24

(22)18.04.88

(46) 15.02.90. Бюл. № 6

(72) Г.Н. Тимонькин, Д.В. Дмитров,

С.Н. Ткаченко и B.C. Карпенко

(53)681.325 (088.8)

(56)Авторское свидетельство СССР № 1111165, кл. С 06 F 9/46, 1983.

Авторское свидетельство СССР № 1269136, кл. G 06 F 9/46, 1985.

(54)УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПРОЦЕССОРАМ

(57)Изобретение относится к вычислительной технике и может быть использовано в отказоустойчивых микропроцессорных системах. Цель изобретения - расширение области применения . Устройство содержит блок регистров, блок элементов ИЛИ, элемент ИЛИ, элемент И-НЕ, элемент И, элемент ИЛИ- НЕ, коммутатор, а в каждом канале - два триггера, два блока элементов И, восемь элементов И, элемент сравнения, регистр, два элемента ИЛИ и од- новибратор. В устройстве введен режим решения задач с повышенной достоверностью. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1988 |

|

SU1636846A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1569831A1 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1751760A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1347081A1 |

| Многопроцессорная система | 1989 |

|

SU1695318A1 |

| Многопроцессорная система | 1989 |

|

SU1735866A1 |

| Многопроцессорная система | 1989 |

|

SU1741144A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1277111A1 |

| Устройство для распределения заданий между ЭВМ | 1988 |

|

SU1575183A1 |

| Многопроцессорная система | 1990 |

|

SU1783538A1 |

Изобретение относится к вычислительной технике и может быть использовано в отказоустойчивых микропроцессорных системах. Цель изобретения - расширение области применения. Устройство содержит блок регистров, блок элементов ИЛИ, элемент ИЛИ, элемент И-НЕ, элемент И, элемент ИЛИ-НЕ, коммутатор, а в каждом канале - два триггера, два блока элементов И, восемь элементов И, элемент сравнения, регистр, два элемента ИЛИ и одновибратор. В устройстве введен режим решения задач с повышенной достоверностью. 3 ил.

Изобретение относится к вычислительной технике и может быть использовано в отказоустойчивых многопроцессорных системах для распределения задач между процессорами.

Цель изобретения - расширение области применения.

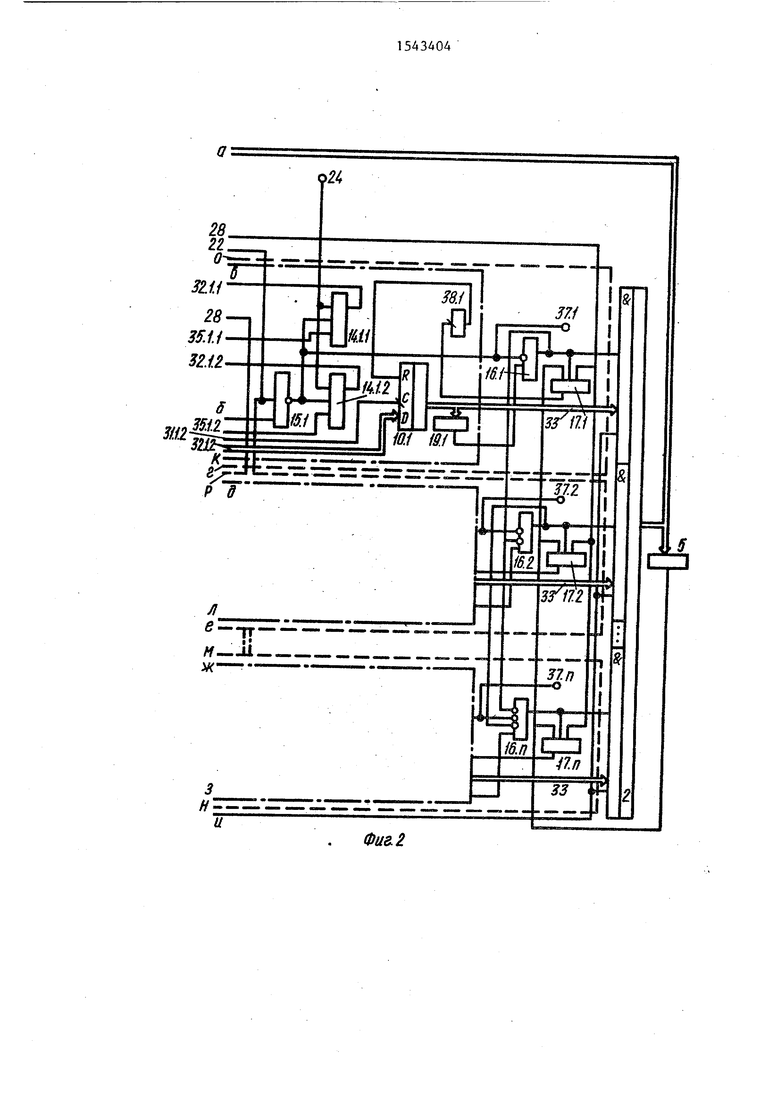

На фиг.1 и 2 приведена функциональная схема устройства; на фиг.З - функциональная схема блока регистров.

Устройство для распределения заданий процессорам содержит блок 1 регистров, коммутатор 2, блок 3 элементов ИЛИ, элемент ИЛИ-НЕ 4, элемент ИЛИ 5, элемент И-НЕ 6, элемент И 7 и каналы, а в каждом канале не входящие в состав устройства первый и второй процессоры 8, каждый канал содержит элемент 9 сравнения и регистр 10, триггер 11 и элементы И 13 и 14, элементы НЕ 15, элементы И 16-18, эле- ненты ИЛИ 19 и 20, информационный вход 21 устройства, вход 22 режима

устройства, входы 23 и 24 синхронизации устройства, группу входа 25 блока 1 регистров, управляющий вход 26 блока 1 регистров, синхронизирующие входы 27 и 28 блока 1 регистров, группу информационных выходов 29 блока 1 регистров, информационные выходы 30 устройства, сигнальные выходы 31 устройства, информационные выходы 32 устройства, группу выходов 33 регистров 10, группы кодовых входов 34 устройства, сигнальные входы 35 устройства, сигнальный выход 36 блока 1 регистров, выходы 37 прерывания устройства, одновибратор 38.

Блок 1 регистров (фиг.З) содержит каналы и в каждом канале регистр 39, блок 40 элементов И, элемент ИЛИ 41, элемент ИЛИ 42, элемент И 43, а также содержит триггер 44, элемент И 45, элемент И 46, блок элементов И 47.

Устройство работает следующим образом.

ся

СП

Ј 00 Ј

В начальном состоянии блок 1 регистров обнулен, в каждом канале триггеры 11 и регистр 10 обнулены (цепи установки в исходное не показаны) ,

Коды задач поступают в блок 1 регистров и с его выхода 29 на информа- ционные входы блоков 12.

Далее устройство может работать в двух режимах: в режиме повышенной производительности; в режиме повышенной достоверности решения задач.

Рассмотрим работу устройства в первом режиме.

В этом режиме каждый процессор решает свою задачу. На входе 22 режима нулевой сигнал. Задача, пришедшая первой, с выхода 29 блока 1 ре- ,гистров поступит для решения в процессор 8.1. Произойдет это следующим образом. Так как все триггеры 11 каналов в нулевом состоянии, то все элементы И 13 будут закрыты нулевым сигналом с выхода элемента И 18.1. Элемент И 13,1.2 будет закрыт нулевым сигналом с выхода элемента ИЛИ 20,1. Поэтому единичный сигнал будет только на выходе элемента И 13,1.1. Этот сигнал разрешит поступление кода задачи через блок 12.1.1 в процессор 8,1.1 для обслуживания, Очередной синхроимпульс с входа 23 пройдет через открытый элемент И 7 и поступит на С-входы всех триггеров 11,1.1, 11.2.2-11.п.1, П.п.2, но в единичное состояние установится только триггер 11.1.1, так как только на его информационном входе присутствует единичный сигнал. Так как триггер 11.1.1 установился в единичное состояние, то на его инверсном выходе появляется нулевой сигнал, который, действуя на инверсный вход элемента ИЛИ 20.1, открывает элемент И 13.1.2. Единичный сигнал с выхода этого элемента разрешит поступление кода следующей задачи в процессор 8,1,2 так, как это описано. После поступления кода второй задачи во второй процессор 8.1.2 триггер 11.1.2 переключится в единичное состояние, на выходе элемента И 18.1 появится единичный сигнал, который откроет элементы И 33.2,1-13.2.2 Код следуютей задачи, поступит в процессор 8.2J и т.д. Если в устройстве нет свободных процессоров, то на выходе элемента И-НЕ 6 появится

5

0

Q

540

30

35

45

50

55

нулевой сигнал, который запретит блоку 1 регистров выдавать задачи для распределения. Все вновь поступившие задачи будут храниться в блоке 1 регистров, ожидая освобождения процессоров.

Если один из процессоров решил задачу, то он выставляет единичный сигнал на соответствующем выходе 35. Так как на входе 22 режима присутствует сигнал О, то на выходе соответствующего элемента И-НЕ 15 будет единичный сигнал. Поэтому очередной синхроимпульс с входа 24 пройдет через открытый элемент И 14 на сброс соответствующего триггера 11, а также в соответствующий процессор 8,2 для установки его в исходное состояние. На выходе соответствующего элемента И 18 появится нулевой сигнал, а на выходе элемента И-НЕ 6 - единичный. Блок 1 регистров выдаст очередную задачу для решения в соответствующий процессор 8.

Рассмотрим работу устройства в режиме повышенной достоверности решения задач.

К определенному типу задач предъявляются повышенные требования по достоверности их решения, поэтому чтобы исключить выдачу ложного результата в случае отказа или сбоя процессора при решении задачи, задача решается в двух процессорах одновременно, после чего результаты решения сравниваются и принимается решение. В этом режиме устройство функционирует следующим образом.

На входе 22 режима присутствует единичный сигнал, который через элементы ИЛИ 20 разрешает,, чтобы одна задача одновременно поступила в два процессора за счет того, что элемент И 13.2 открывается вместе с элементом И 3.1 .

Процесс поступления задачи в процессоры 8 и установка триггеров 11 в единичное состояние аналогичен первому режиму работы устройства. OT-J личие состоит в том, что код задачи с выхода 30.2 блока элементов И 12.2 запишется в регистр 10. Запись произойдет по заднему фронту сигнала с выхода элемента И 13.2.

Далее задача решается в процессорах и по окончании ее решения возможны два случая: коды результатов решения задачи с выходов 34.1 и 34,2 совпадают, т.е. задача решена верно; коды результатов репюния задачи с выходов 34.J и 34.2 не совпадают, т.е. задача решена неверно одним или двумя процессорами.

Б первом случае на выходе элемента 9 сравнения по окончании решения задачи будет нулевой сигнал. Поэто- му на выходе элемента И-НЕ 15 будет единичный сигнал. Следовательно, элементы И 14.1 и 14.2 будут открыты и синхронизирующий сигнал с входа 24 пройдет через элементы И 14.1 и 14.2 и установит триггеры 11 в нулевое положение.

Во втором случае элемент 9 сравнения по окончании решения задачи выдает единичный сигнал. На выходе элемента И-НЕ 15 будет нулевой сигнал, который закроет элементы И 14. Следовательно, сигналы сброса не пройдут на выходе этих элементов, а поэтому данный -сигнал на время про- верки процессоров будет выведен из конфигурации устройства. Единичный сигнал с выхода элемента И-НЕ 15 через элемент И 16 поступает на соответствующий управляющий вход коммута- тора 2. В результате код неверной задачи поступает на вход блока 1 с целью ее повторного распределения и решения на другой паре процессоров. Код задачи поступит на выход коммутатора 2, если нет кода задачи на входе 21 устройства, о чем свидетельствует единичный сигнал на выходе элемента ИЛИ-НЕ 4. После того, как код задачи запишется в блок 1 регистров, по очередному импульсу с входа 24 произойдет обнуление регистра 10.

Если после контроля процессоров окажется, что в одном или обоих процессорах произошел сбой, то для вво- да их в конфигурацию устройства необходимо дать сигналы готовности на выходы 35. Эти сигналы, пройдя через элементы И 14, установят соответствующие триггеры 11 в нулевое состояние после чего данная пара процессоров готова принять очередную задачу.

Формула изобретения

Устройство для распределения за- даний процессорам, содержащее блок регистров, блок элементов ИЛИ, элемент ИЛИ, элемент И-НЕ, элемент И, каналы и в каждом канале первый и

д $

0 5 0

5 0

5

0

второй триггеры, первый и второй блоки элементов И, первый и второй элементы И, причем сигнальный выход блока регистров подключен к первому входу элемента И, первый вход синхронизации устройства подключен к второму входу элемента И, выход элемента И-НЕ подключен к третьему входу элемента И, в каждом канапе инверсные выходы первого и второго триггеров подключены к первым входам первого и второго элементов И соответственно, отличающееся тем, что, с целью расширения области применения, в устройство дополнительно введены элемент ИЛИ-НЕ, коммутатор, в каждый канал - элемент сравнения, регистр, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И, первый и второй элементы ИЛИ, одно- вибратор, причем в каждом канале прямые выходы первого и второго триггеров подключены к первому и второму входам третьего элемента И своего канала, выход которого подключен к соответствующим входам первых и вторых элементов И каналов с большим порядковым номером и к соответветст- вующему входу элемента И-НЕ, выход которого подключен к управляющему входу блока регистров, группа информационных выходов которого подключена к группам информационных входов первого и второго блоков элементов И всех каналов, выходы блоков элементов И каналов являются информационны- ными выходами устройства, выход элемента И подключен к тактовым входам первого и второго триггеров всех каналов, выходы первого и второго элементов И каждого канала подключены к установочным входам первого и второго триггеров своего канала соответственно, в каждом канале выход второго элемента И подключен к синхронизирующему входу регистра своего канала, выходы которого подключены к соответствующей группе информационных входов коммутатора и к входам первого элемента ИЛИ своего канала, в каждом канале инверсный выход первого триггера подключен к инверсному выходу второго элемента ИЛИ своего канала, выход которого подключен к соответствующему входу второго элемента И своего канала, в каждом канале выходы первого и второго элементов И подключены к управляющим входам первого и второго блоков элементов И, а также являются сигнальными выходами устройства, группы кодовых входов устройства под- .ключены к первой и второй группам выходов элемента сравнения, выход которого подключен к первому входу своего канала, выхор элемента в каждом канале подключен к первым входам четвертого и пятого и к инверсному входу шестого элементов И своего канала, выходы четвертого и пятого элементов И каждого канала подключены к входам сброса первого и

15434048

го элемента И в каждом канале через одновибратор подключен к входу сброса регистра своего канала, информационные выходы коммутатора подключены к первой группе входов блока элементов ИЛИ и к входам элемента ИЛИ, выход которого подключен к вторым входам седьмых элементов И всех каналов, группа информационных входов устройства подключена к второй группе блока элементов ИЛИ и к входам элемента ИЛИ-НЕ, выход которого подключен к соответствующим управляющим входам ком10

второго триггеров своего канала выхо-) мутатора, выход блока элементов ИЛИ

дЫ второго блока элементов И канала подключены к информационным входам регистра своего канала, в каждом канале сигнальные входы устройства подключены к вторым входам четвертого и пятого элементов И своего канала соответственно, выход первого элемента ИЛИ в каждом канале подключен к прямому входу шестого элемента И своего канала, выход которого подключен к соответствующему управляющему входу коммутатора, к первому входу седь- мЬго элемента И и к инверсным входам восьмых элементов И каналов с боль20

25

подключен к группе информационных входов блока регистров, вход режима устройства подключен к прямым входам вторых элементов ИЛИ каналов и к вторым входам элементов И-НЕ всех каналов, первый синхронизирующий вход устройства подключен к первому синхронизирующему входу блока регистров, второй синхронизирующий вход устройства подключен к второму синхронизирующему входу блока регистров, к третьим входам четвертого, пятого и седьмого элементов И всех каналов, выходы элементов И-НЕ каналов являются выходами

шим порядковым номером, выход седьмо- 30 прерывания устройства.

мутатора, выход блока элементов ИЛИ

подключен к группе информационных входов блока регистров, вход режима устройства подключен к прямым входам вторых элементов ИЛИ каналов и к вторым входам элементов И-НЕ всех каналов, первый синхронизирующий вход устройства подключен к первому синхронизирующему входу блока регистров, второй синхронизирующий вход устройства подключен к второму синхронизирующему входу блока регистров, к третьим входам четвертого, пятого и седьмого элементов И всех каналов, выходы элементов И-НЕ каналов являются выходами

га

36 -о

29

Ц

Авторы

Даты

1990-02-15—Публикация

1988-04-18—Подача