Изобретение относится к вычислительной технике и может быть использовано в отказоустойчивых многопроцессорных вычислительных системах для распределения заданий между процессорами.

Цель изобретения - сокращение объема оборудования устройства.

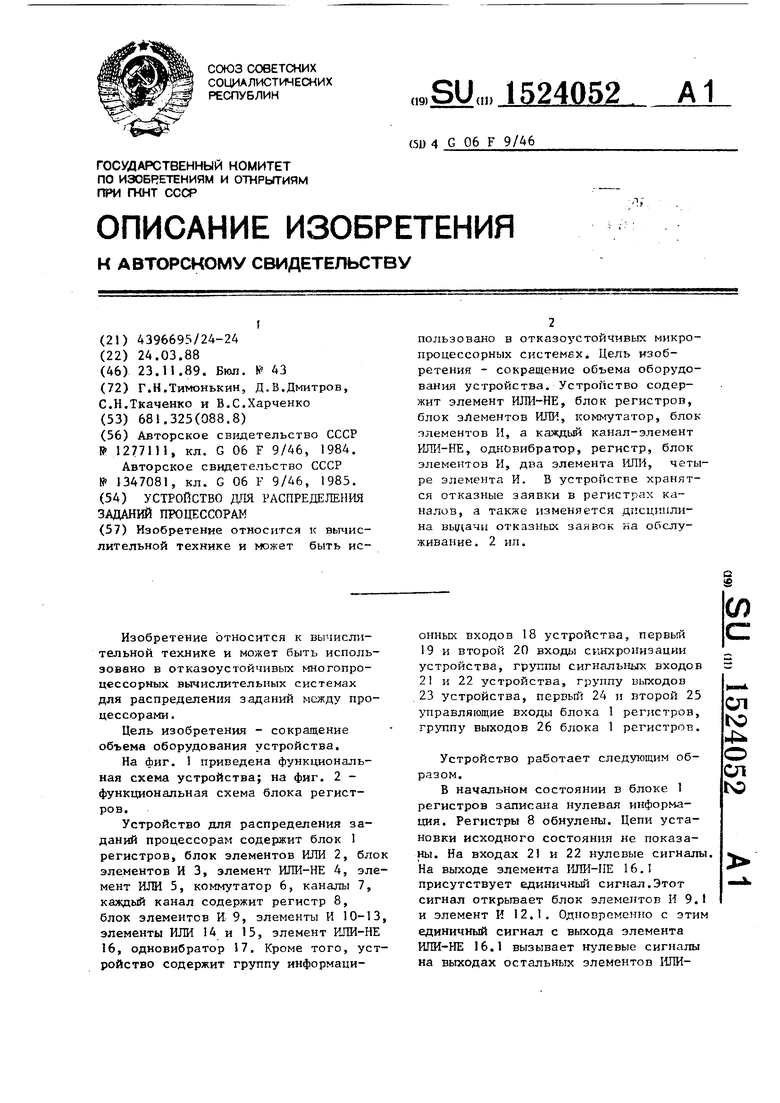

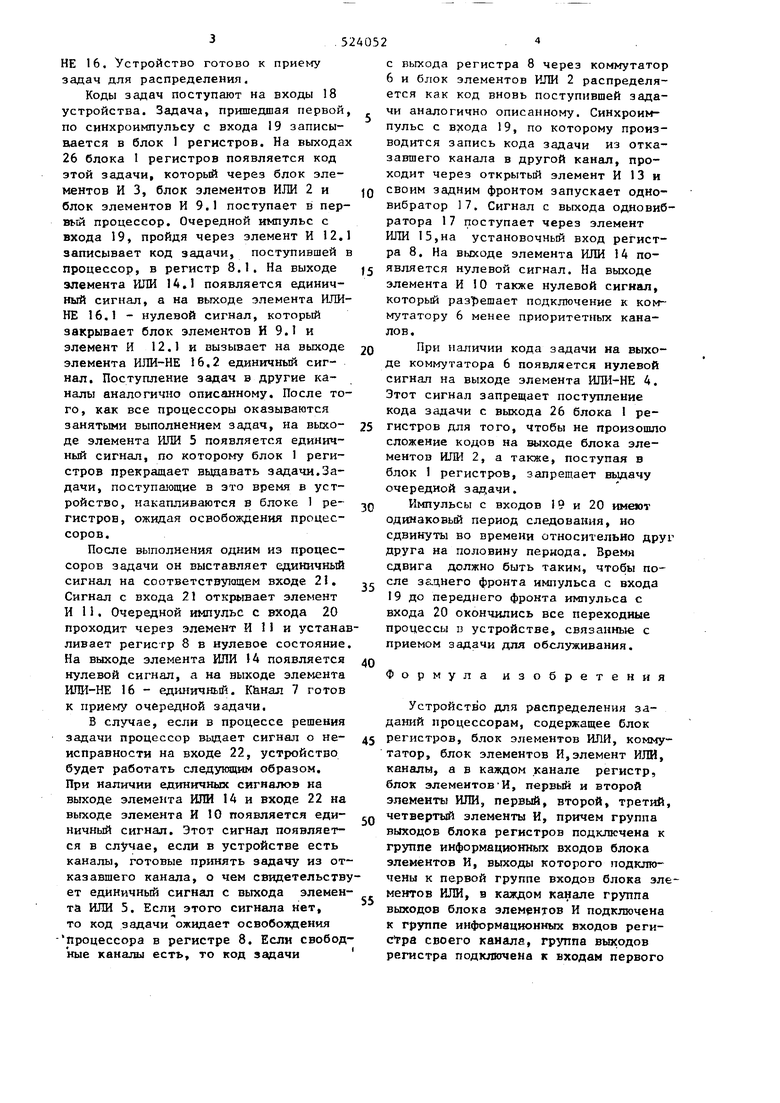

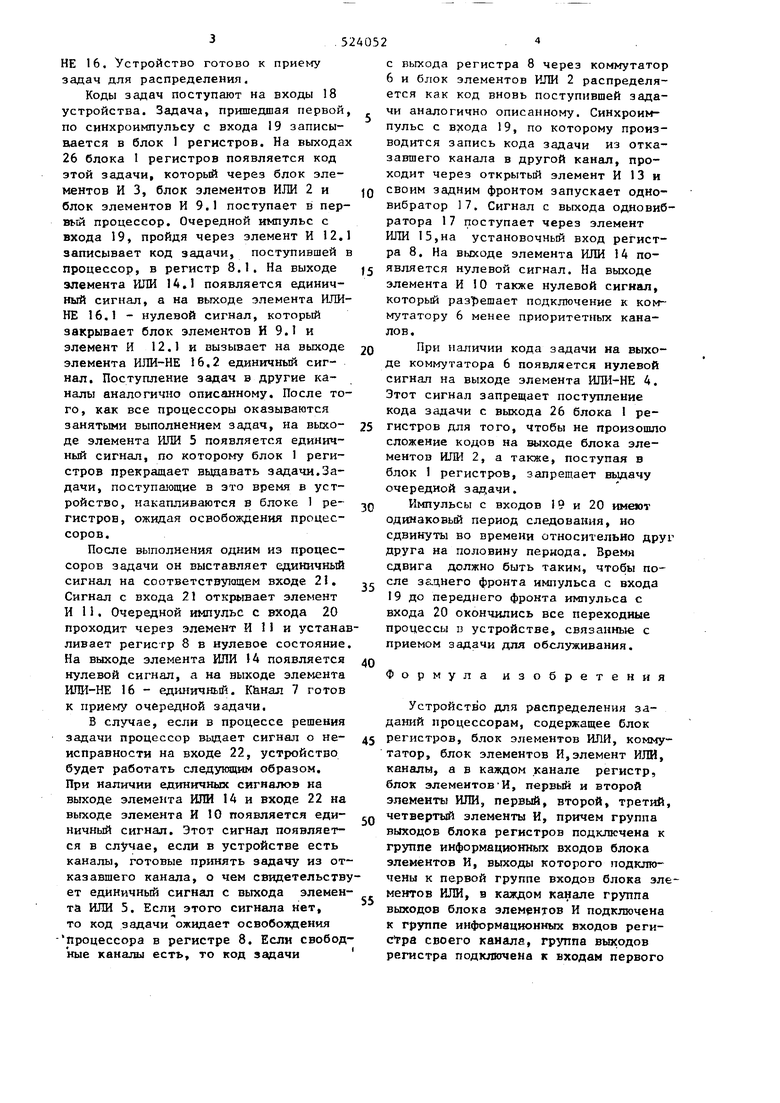

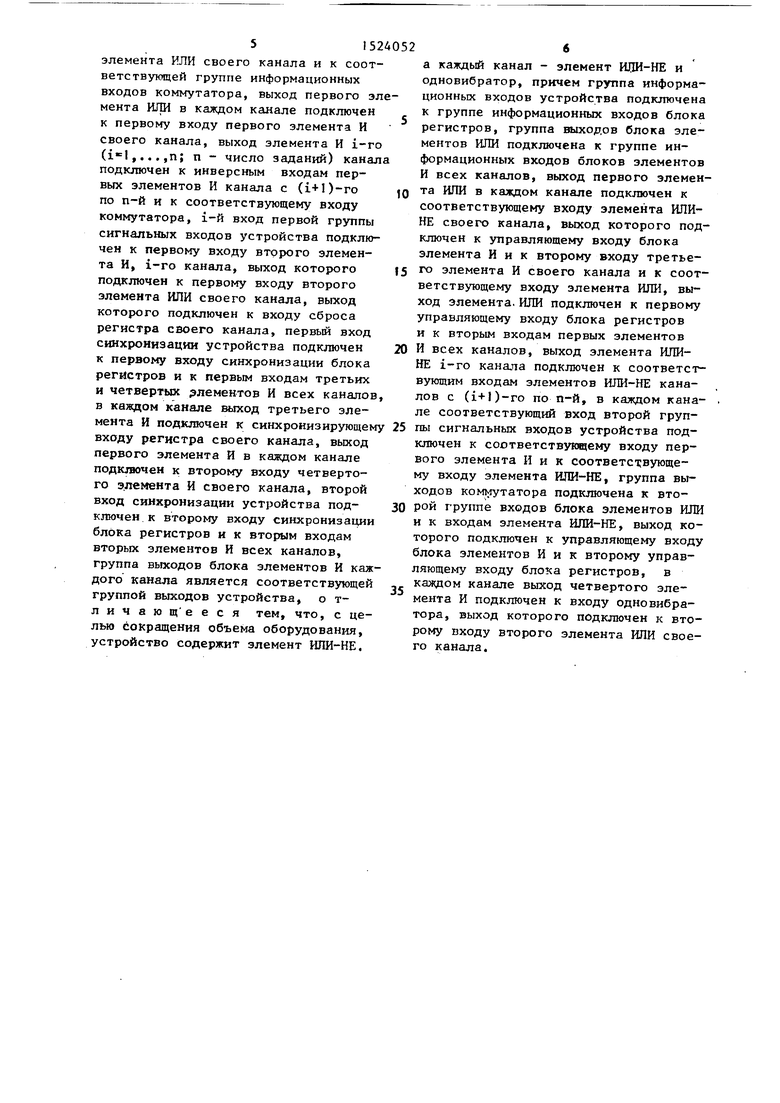

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока регистров.

Устройство для распределения заданий процессорам содержит блок 1 регистров, блок элементов ИЛИ 2, блок элементов И 3, элемент ИЛИ-НЕ 4, элемент ИЛИ 5, коммутатор 6, каналы 7, каждый канал содержит регистр 8, блок элементов И 9, элементы И 10-13, элементы ИЛИ 14 и 15, элемент ИЛИ-НЕ 16, одновибратор 17. Кроме того, устройство содержит группу информационных входов 18 устройства, первый 19 и второй 20 входы синхронизации устройства, группы сигнальных входов 21 и 22 устройства, группу выходов 23 устройства, первьй 24 и второй 25 управляющие входы блока 1 регистров, группу выходов 26 блока 1 регистров.

Устройство работает следующим образом.

В начальном состоянии в блоке 1 регистров записана нулевая информация. Регистры 8 обнулены. Цепи установки исходного состояния не показаны. На входах 21 и 22 нулевые сигналы. На выходе элемента ИЛИ-НЕ 16,1 присутствует единичный сигнал.Этот сигнал открывает блок элементов И 9.1 и элемент И 12.1. Одновременно с этим единичный сигнал с выхода элемента ИЛИ-НЕ 16,1 вызывает кулевые сигналы на выходах остальных элементов 1ШИСП

к:)

4 о

ел

го

НЕ 16. Устройство готово к приему задач для распределения.

Коды задач поступают на входы 18 устройства. Задача, пришедшая первой, по синхроимпульсу с входа 19 записывается в блок 1 регистров. На выходах 26 блока 1 регистров появляется код этой задачи, который через блок элементов И 3, блок элементов ИЛИ 2 и блок элементов И 9.1 поступает в первый процессор. Очередной импульс с входа 19, пройдя через элемент И 12.1 записывает код задачи, поступившей в процессор, в регистр 8.1. На выходе элемента ИЛИ 14.1 появляется единичный сигнал, а на выходе элемента ИЛИ- НЕ 16.1 - нулевой сигнал, который закрывает блок элементов И 9.1 и элемент И 12.1 и вызывает на выходе элемента ИЛИ-НЕ 16,2 единичный сигнал. Поступление задач в другие каналы аналогично описанному. После того, как все процессоры оказываются

35

занятыми выполнением задач, на вько- е элемента ИЛИ 5 появляется единичный сигнал, по которому блок 1 регистров прекращает выдавать задачи,Заачи, поступающие в это время в устройство, накапливаются в блоке 1 регистров, ожидая освобождения процессоров.

После выполнения одним из процессоров задачи он выставляет единичный сигнал на соответствующем входе 2I. Сигнал с входа 21 открывает элемент И 11. Очередной импульс с входа 20 проходит через элемент И 11 и устанавливает регистр 8 в нулевое состояние. На выходе элемента ИЛИ 1А появляется 0 нулевой сигнал, а на выходе элемента ШШ-НЕ 16 - единичньй, КЬнал 7 готов к приему очередной задачи.

В случае, если в процессе решения задачи процессор выдает сигнал о неисправности на входе 22, устройство будет работать следующим образом. При наличии единичных сигналов на выходе элемента ШШ 14 и входе 22 на выходе элемента И 10 появляется единичный сигнал. Этот сигнал появляется в случае, если в устройстве есть каналы, готовые принять задачу из отказавшего канала, о чем свидетельствует единичный сигнал с выхода элемента ИЛИ 5. Если этого сигнала нет, то код задачи ожидает освобождения процессора в регистре 8, Если свободные канала естрь, то код задачи

25

30

45 ,

50

с выхода регистра 8 через коммутатор 6 и блок элементов ИЛИ 2 распределяется как код вновь поступившей зада- чи аналогично описанному. Синхроимпульс с входа 19, по которому производится запись кода задачи из отказавшего канала в другой канал, проходит через открытый элемент И 13 и

своим задним фронтом запускает одно- вибратор 17. Сигнал с выхода одновиб- ратора 17 поступает через элемент ИЛИ 15,на установочный вход регистра 8, На выходе элемента ИЖ 14 появляется нулевой сигнал. На выходе элемента И 10 также нулевой сигнал, который разрешает подключение к коммутатору 6 менее приоритетных каналов,

При наличии кода задачи на выходе коммутатора 6 появляется нулевой сигнал на выходе элемента ИЛИ-НЕ 4. Этот сигнал запрещает поступление кода задачи с выхода 26 блока I регистров для того, чтобы не произошло сложение кодов на выходе блока элементов ШШ 2, а также, поступая в блок 1 регистров, запрещает выдачу очередной зад.ачи,

Импульсы с входов 19 и 20 имеют одинаковьЕЙ период следования, но сдвинуты во времени относительно друг друга на половину периода. Время сдвига должно быть таким, чтобы после зацнего фронта импульса с входа 19 до переднего фронта импульса с входа 20 окончились все переходные процессы 13 устройстве, связанные с приемом задачи для обслуживания.

0

Формула изобретения

Устройство для распределения заданий процессорам, содержащее блок 5 регистров, блок элементов ИЛИ, коммутатор, блок элементов И,элемент ИЛИ, каналы, а в каждом канале регистр, блок элементов И, первый и второй элементы ИЛИ, первый, второй, третий, четвертый элементы И, причем группа выходов блока регистров подключена к группе информационных входов блока элементов И, вьрсоды которого подключены к первой группе входов блока эле- , ментов ИЛИ, в каждом канале группа выходов блока элементов И подключена к группе информационных входов реги- cl-pa своего канала, группа выходов регистра подключена к входам первого

0

5152

элемента ИЛИ своего канала и к соответствующей группе информационных входов коммутатора, выход первого элмента ИЛИ в каждом канале подключен к первому входу первого элемента И своего канала, выход элемента И i-ro (,...,n; n - число заданий) канал подключен к инверсным входам первых элементов И канала с (i+l)-ro по п-й и к соответствующему входу коммутатора, i-й вход первой группы сигнальных входов устройства подключен к первому входу второго элемента И, i-ro канала, вьтход которого подключен к первому входу второго элемента ИЛИ своего канала, выход которого подключен к входу сброса регистра своего канала, первый вход синхронизации устройства подключен к первому входу синхронизации блока регистров и к первым входам третьих и четвертых элементов И всех каналов в каждом канале выход третьего элемента И подключен к синхронизирующем входу регистра своего канала, выход первого элемента И в каждом канале подключен к второму входу четвертого э.лемента И своего канала, второй вход синхронизации устройства под- ключей.к второму входу синхронизации блока регистров и к вторым входам вторых элементов И всех каналов, группа выходов блока элементов И каждого канала является соответствующей группой выходов устройства, о т- личающ ееся тем, что, с целью сокращения объема оборудования, устройство содержит элемент ИЛИ-НЕ.

а каждый канал - элемент ИДИ-НЕ и одновибратор, причем группа информационных входов устройства подключена к группе информационных входов блока регистров, группа выходов блока элементов ИЛИ подключена к группе информационных входов блоков элементов И всех каналов, выход первого элемента ШШ в каждом канапе подключен к соответствующему входу элемента ИЛИ- НЕ своего канала, выход которого подключен к управляющему входу блока элемента Ник второму входу третьего элемента И своего канала и к соответствующему входу элемента ИЛИ, выход элемента, ИЛИ подключен к первому управляющему входу блока регистров и к вторым входам первых элементов И всех каналов, выход элемента ИЛИ- НЕ i-ro канала подключен к соответствующим входам элементов ИЛИ-НЕ каналов с (i+l)-ro по п-й, в каждом канале соответствующий вход второй группы сигнальных входов устройства подключен к соответствующему входу первого элемента И и к соответствующему входу элемента ШШ-НЕ, группа выходов коммутатора подключена к второй группе входов блока элементов ИЛИ и к входам элемента ИЛИ-НЕ, выход которого подключен к управляющему входу блока элементов И и к второму управляющему входу блока регистров, в каждом канале выход четвертого элемента И подключен к входу одновибратора, выход которого подключен к второму входу второго элемента ИЛИ своего канала.

Фи.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1988 |

|

SU1569831A1 |

| Многопроцессорная система | 1987 |

|

SU1494005A1 |

| Многопроцессорная система | 1990 |

|

SU1783538A1 |

| Многопроцессорная система | 1989 |

|

SU1741144A1 |

| Устройство для обслуживания сообщений | 1986 |

|

SU1341638A1 |

| Устройство приоритета | 1990 |

|

SU1742820A1 |

| Многопроцессорная система | 1989 |

|

SU1735866A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1636846A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1277111A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1543404A1 |

Изобретение относится к вычислительной технике и может быть использовано в отказоустойчивых микропроцессорных системах. Цель изобретения - сокращение объема оборудования устройства. Устройство содержит элемент ИЛИ-НЕ, блок регистров, блок элементов ИЛИ, коммутатор, блок элементов И, а каждый канал-элемент ИЛИ-НЕ, одновибратор, регистр, блок элементов И, два элемента ИЛИ, четыре элемента И. В устройстве хранятся отказные заявки в регистрах каналов, а также изменяется дисциплина выдачи отказных заявок на обслуживание. 2 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1347081A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-23—Публикация

1988-03-24—Подача