с (i+l)-M входом, второй выход - с (i +2)-м входом, ,,,,. (р-1)-й вькод- с р-м входом, (р-1+1)-й выход - с первым входом,(р-1+2)-й выход - с вторым входом, р-й выход - с i -M вхо дом.

Структура устройства для цифровой фильтрации описывается выражением d-1

H(ZHl-Z )H( а, (1)

где

(-1

1 )

-mn

(2)

Изобретение относится к вычисли тельной технике и информационно-измерительным системам и может быть использовано в системах для цифровой обработки сигналов, в частности изображений ,

Цель изобретения -. повышение точности работы устройства.

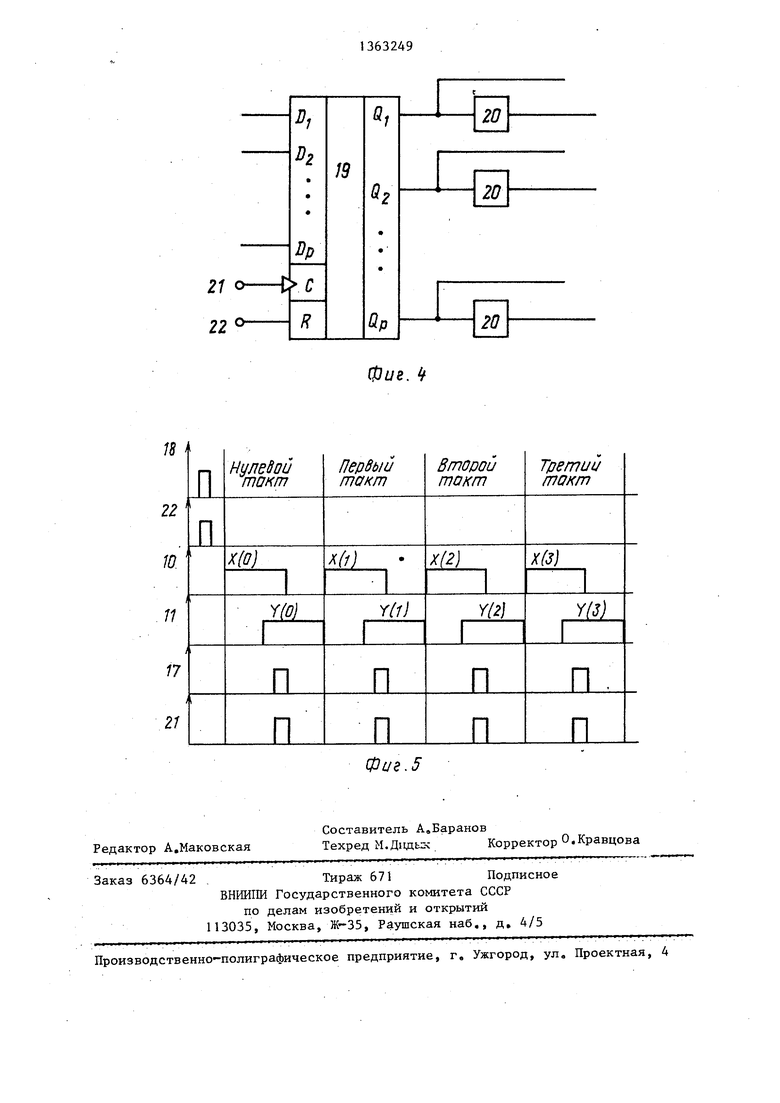

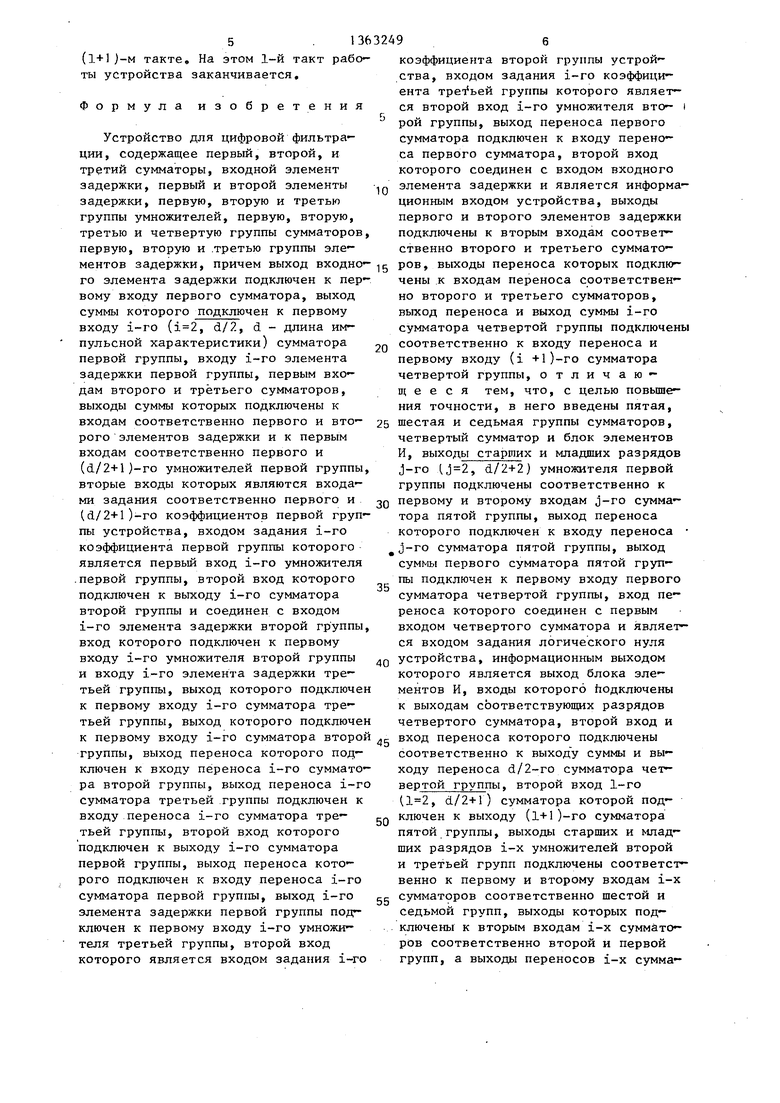

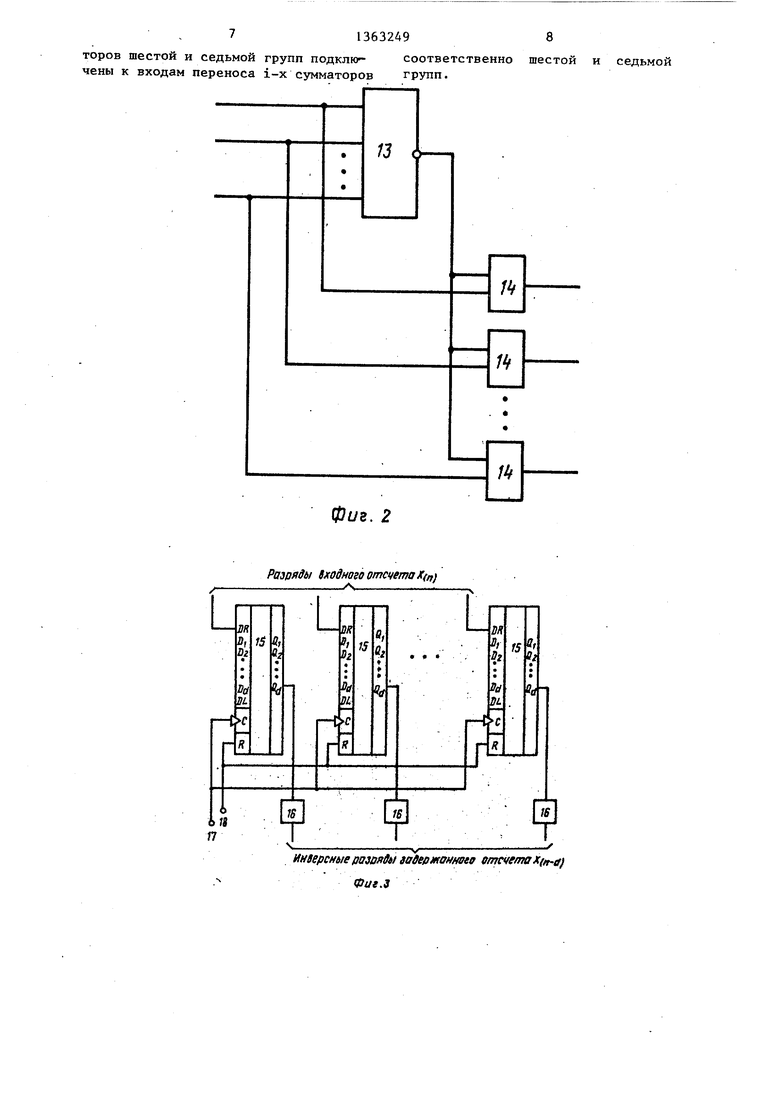

На фиг,1 представлена структурная Q схема устройства для цифровой фильтрации; на фиг,2 -, схема блока элементов И; на фиг,3 - элемент задержки; . на фиг,4 - элементы задержки группы;

на.фиг,5 - временные диаграммы, по-IK „ ° lo А (

„ „ Все вычисления в выражениях (2 )я (i )

ясняющие работу устройства,„ „

щгг t у у н , подстановке вместо переменной Z

Устройство (фиг,1) содержит первый

f v-f . / м 1- t- числа проводятся по модулю целого

числа 2-, Через X обозначен обратный к элементу X в кольце много-

ментов 4 задержки, группу умножите- ont г „„ .

членов от переменной Z над кольцом

леи 5, третью 6 и вторую 7 группы -1; d - длисумматоров, второй сумматор 8, блок „а .импульсной характеристики устройства; li(n) - промасштабированные и округленные до целых чисел отсчеты импульсной характеристики, В рассматриваемом случае -2,

Для того, чтобы на выходе устроитства Y(n) Xji(k) X(n-k) получалась

правильная арифметическая свертка, необходимо, исходя из возможных зна- чений Х(п) и h(n), выбрать соответствующий модуль М согласно вьгсумматор 1, элемент 2 задержки, первую группу сумматоров 3, группу эле-

9 элементов И, вход 10 отсчета, выход И отсчета, входы 12 задания коэффициентов ,25

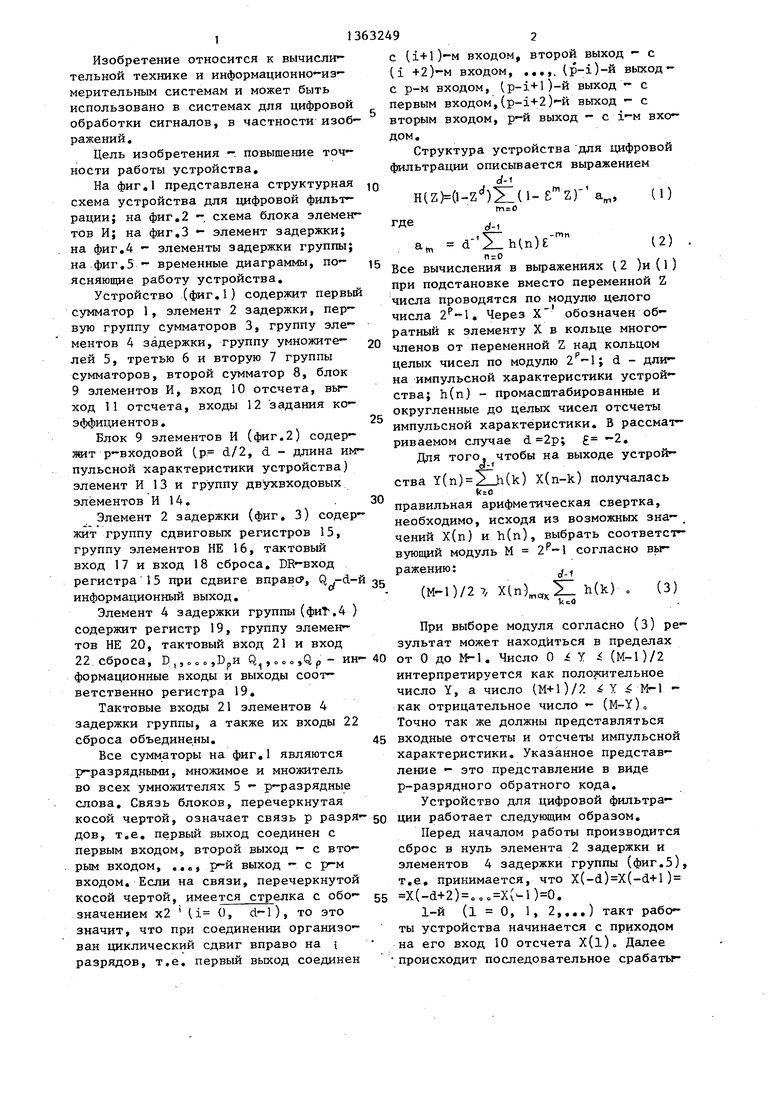

Блок 9 элементов И (фиг.2) содержит р-в кодовой (р. d/2, d - длина импульсной характеристики устройства) элемент И 13 и группу двухвходовых элементов И 14,.30

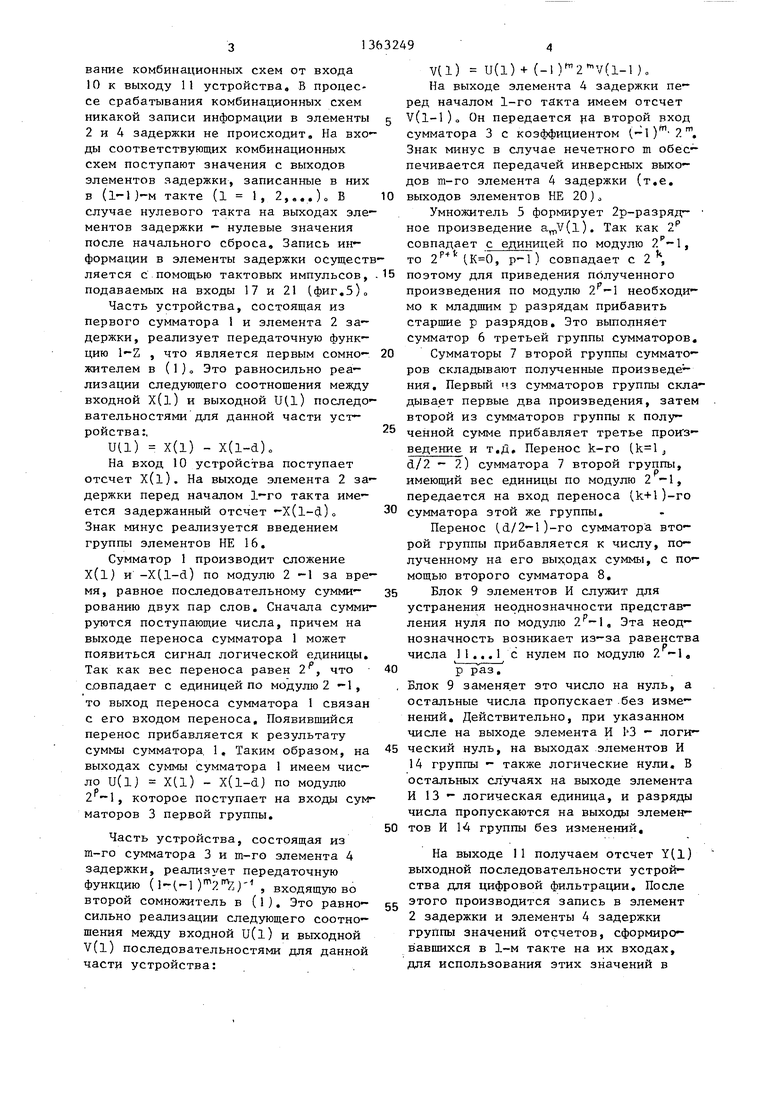

Элемент 2 задержки (фиг, 3) содержит группу сдвиговых регистров 15, группу элементов НЕ 16, тактовый вход 17 и вход 18 сброса, DR-вход

ражению:

регистра 15 при сдвиге вправе, Q ,-d-й 35 информационный выход.

При выборе модуля согласно (З) результат может находиться в пределах

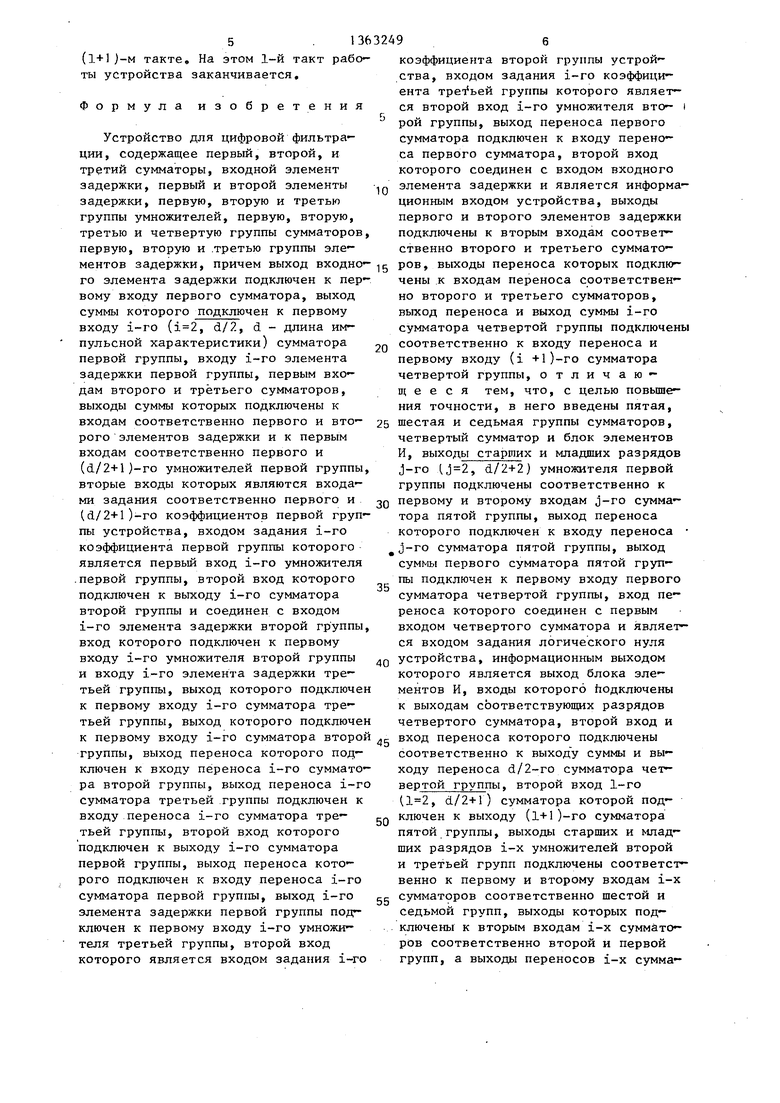

Элемент 4 задержки группы (фиТ,4 ) содержит регистр 19, группу элементов НЕ 20, тактовый вход 21 и вход 22,сброса, D, ,„„„,ВрИ Q,oco,Qp - ин- 40 от О до М-1, Число О Y (М-1)/2 формационные входы и выходы соот- интерпретируется как положительное ветственно регистра 19,

Тактовые входы 21 элементов 4 задержки группы, а также их входы 22 сброса объединены.

Все сумматоры на фиг,1 являются

р-разрядными, множимое и множитель во всех умножителях 5 - р-разрядные слова. Связь блоков, перечеркнутая

число Y, а число (М+1)/. Y - как отрицательное число - (M-Y), Точно так же должны представляться 45 входные отсчеты и отсчеты импульсной характеристики. Указанное представление - это представление в виде р-разрядного обратного кода.

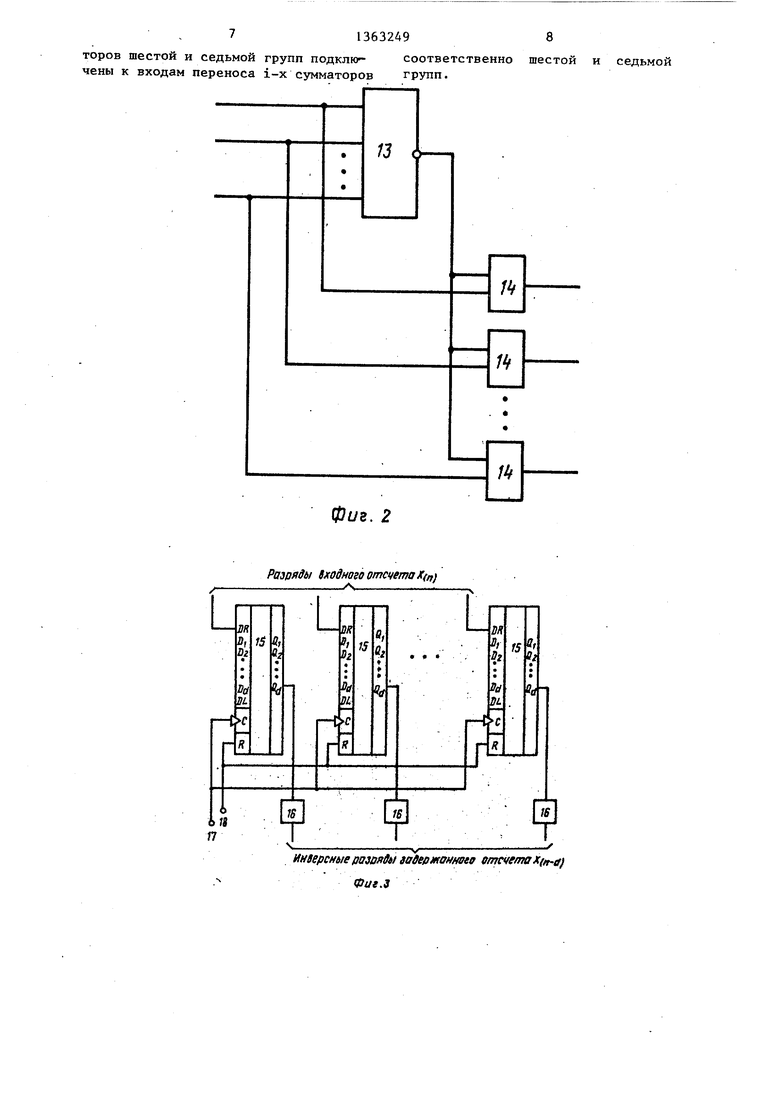

Устройство для цифровой фильтра- косой чертой, означает связь р разря- 50 Ции работает следующим образом, дов, т,е, первый выход соединен с Перед началом работы производится первым входом, второй выход - с вто- сброс в нуль элемента 2 задержки и рым входом, ,,,, р-й выход - с элементов 4 задержки группы (фиг,5), входом. Если на связи, перечеркнутой т,е, принимается, что X(-d)X(-d+l) косой чертой, имеется стрелка с обо- 55 X(-d+2) o , (-1 )0, значением х2 U О, d-l), то это 1-й (l О, 1, 2,,,,) такт рабо- значит, что при соединении организо- ты устройства начинается с приходом ван циклический сдвиг вправо на ( на его вход 10 отсчета X(l), Далее разрядов, т.е. первый выход соединен -происходит последовательное срабатьг632492

с (i+l)-M входом, второй выход - с (i +2)-м входом, ,,,,. (р-1)-й вькод- с р-м входом, (р-1+1)-й выход - с первым входом,(р-1+2)-й выход - с вторым входом, р-й выход - с i -M вхо дом.

Структура устройства для цифровой фильтрации описывается выражением d-1

H(ZHl-Z )H( а, (1)

где

(-1

1 )

-mn

(2)

Q

ражению:

С/-1

(М-1)/2 7, XU)

мах

h(k)

(3)

от О до М-1, Число О Y (М-1)/2 интерпретируется как положительное

При выборе модуля согласно (З) результат может находиться в пределах

от О до М-1, Число О Y (М-1)/2 интерпретируется как положительное

комбинационных схем от входа 10 к выходу 11 устройства. В процессе срабатывания комбинационных схем никакой записи информации в элементы 2 и 4 задержки не происходит. На входы соответствующих комбинационных схем поступают значения с выходов элементов задержки, записанные в них

в

(1-и-м такте (l 1, 2,...) о В

случае нулевого такта на выходах элементов задержки - нулевые значения после начального сброса. Запись информации в элементы задержки осущестляется с помощью тактовых импульсов, подаваемых на входы 17 и 21 (фиг,5)о

Часть устройства, состоящая из первого сумматора 1 и элемента 2 задержки, реализует передаточную функцию 1-Z , что является первым сомножителем в (1 ) о Это равносильно реализации следующего соотношения между входной X(l) и выходной U(l) последовательностями для данной части устройства:,

Uil) Х(1) - X(l-d).

На вход 10 устройства поступает отсчет X(l). На выходе элемента 2 задержки перед началом 1-го такта имеется задержанный отсчет -X(l-cL)o Знак минус реализуется введением группы элементов НЕ 16.

Сумматор 1 производит сложение X(l) и -X(l-d) по модулю 2 -1 за время, равное последовательному суммированию двух пар слов. Сначала суммируются поступающие числа, причем на выходе переноса сумматора 1 может появиться сигнал логической единицы. Так как вес переноса равен 2, что совпадает с единицей по модулю 2 -1, то выход переноса сумматора 1 связан с его входом переноса. Появившийся перенос прибавляется к результату суммы сумматора. 1, Таким образом, на выходах суммы сумматора 1 имеем число и(1) Х(1) - X(l-d) по модулю 2 - 1, которое поступает на входы сум маторов 3 первой группы.

Часть устройства, состоящая из т-го сумматора 3 и т-го элемента 4 задержки, реализует передаточную функцию (l-l-l ) , входящую во второй сомножитель в (1). Это равносильно реализации следующего соотношения между входной U(l) и выходной V(l) последовательностями для данной части устройства:

0

0

15

V(l) U(l) + (-1)(1-1 )„ На выходе элемента 4 задержки перед началом 1-го такта имеем отсчет V(l-l)o Он передается ра второй вход сумматора 3 с коэффициентом (-1). Знак минус в случае нечетного m обеспечивается передачей инверсных выходов т-го элемента 4 задержки (т.е. выходов элементов НЕ 20)

Умножитель 5 формирует 2р-разряд- ное произведение (l). Так как 2 совпадает с единицей по модулю

30

35

45

50

55

2(, p-l)

совпадает с 2

Г- то

поэтому для приведения полученного произведения по модулю 2-1 необходимо к младшим р разрядам прибавить старшие р разрядов. Это выполняет сумматор 6 третьей группы сумматоров.

Сумматоры 7 второй группы сумматоров складывают полученные произведения. Первый 43 сумматоров группы складывает первые два произведения, затем второй из сумматоров группы к полу- ченной сумме прибавляет третье прои з- ведение и т.д. Перенос k-ro ( d/2 - 2) сумматора 7 второй группы, имеющий вес единицы по модулю 2-1, передается на вход переноса (k+1)-го сумматора этой же группы.

Перенос (,d/2-l)-ro сумматор а второй группы прибавляется к числу, полученному на его выходах суммы, с помощью второго сумматора 8.

Блок 9 элементов И служит для устранения неоднозначности представления нуля по модулю , Эта неоднозначность возникает из-за равенства числа 1 1 ... 1 с нулем по модулю 2 -1«

Р раз.

Блок 9 заменяет это число на нуль, а остальные числа пропускает без изменений. Действительно, при указанном числе на выходе элемента И 13 - логический нуль, на выходах элементов И 14 группы - также логические нули. В остальных случаях на выходе элемента И 13 - логическая единица, и разряды числа пропускаются на выходы элементов И 14 группы без изменений.

На выходе 11 получаем отсчет Y(l) выходной последовательности устройства для цифровой фильтрации. После этого производится запись в элемент 2 задержки и элементы 4 задержки группы значений отсчетов, сформировавшихся в 1-м такте на их входах, для использования этих значений в

40

(l+lj-M такте. На этом 1-и такт работы устройства заканчивается.

Формула изобретения

Устройство для цифровой фильтрации, содержащее первый, второй, и третий сумматоры, входной элемент задержки, первый и второй элементы задержки, первую, вторую и третью группы умножителей, первую, вторую, третью и четвертую группы сумматоров, первую, вторую и .третью группы элементов задержки, причем выход входно- g ров, выходы переноса которых подклю-

го элемента задержки подключен к первому входу первого сумматора, выход суммы которого подключен к первому входу 1-го (, d/2, d - длина импульсной характеристики) сумматора первой группы, входу i-ro элемента задержки первой группы, первым входам второго и третьего сумматоров, выходы суммы которых подключены к входам соответственно первого и второго элементов задержки и к первым входам соответственно первого и (d/2+l)-го умножителей первой группы, вторые входы которых являются входами задания соответственно первого и (d/2+l)-го коэффициентов первой группы устройства, входом задания i-ro коэффициента первой группы которого является первый вход i-ro умножителя .первой группы, второй вход которого подключен к выходу i-ro сумматора второй группы и соединен с входом i-ro элемента задержки второй группы, вход которого подключен к первому входу i-ro умножителя второй группы и входу i-ro элемента задержки третьей группы, выход которого подключен к первому входу i-ro сумматора третьей группы, выход которого подключен

к первому входу i-ro сумматора второй вход переноса которого подключены

группы, выход переноса которого подключен к входу переноса i-ro сумматора второй группы, выход переноса i-ro сумматора третьей группы подключен к входу переноса i-ro сумматора третьей группы, второй вход которого подключен к выходу i-ro сумматора первой группы, выход переноса которого подключен к входу переноса i-ro сумматора первой группы, выход i-ro элемента задержки первой группы подключен к первому входу i-ro умножителя третьей группы, второй вход которого является входом задания i-ro

50

55

соответственно к выходу суммы и вы ходу переноса d/2-го сумматора чет вертой группы, второй вход 1-го (, d/2+l) сумматора которой под ключен к выходу (1+1)-го сумматора пятой группы, выходы старших и мла ших разрядов i-x умножителей второ и третьей групп подключены соответ венно к первому и второму входам i сумматоров соответственно шестой и седьмой групп, выходы которых подключены к вторым входам i-x суммат ров соответственно второй и первой групп, а выходы переносов i-x сумм

коэффициента второй группы устройства, входом задания i-ro коэффициента трет ьей группы которого является второй вход i-ro умножителя вто- i рой группы, выход переноса первого сумматора подключен к входу переноса первого сумматора, второй вход которого соединен с входом входного элемента задержки и является информационным входом устройства, выходы первого и второго элементов задержки подключены к вторым входам соответственно второго и третьего суммато-

чены к входам переноса соответственно второго и третьего сумматоров, выход переноса и выход суммы i-ro сумматора четвертой группы подключены соответственно к входу переноса и первому входу (i +1)-го сумматора четвертой группы, отличающееся тем, что, с целью повьппе- ния точности, в него введены пятая, шестая и седьмая группы сумматоров, четвертый сумматор и блок элементов И, выходы старших и младших разрядов j-ro , d/2+2) умножителя первой группы подключены соответственно к первому и второму входам j-ro сумматора пятой группы, выход переноса которого подключен к входу переноса j-ro сумматора пятой группы, выход суммы первого сумматора пятой группы подключен к первому входу первого сумматора четвертой группы, вход переноса которого соединен с первым входом четвертого сумматора и является входом задания логического нуля устройства, информационным выходом которого является выход блока элементов И, входы которого Ьодключены к выходам соответствующих разрядов четвертого сумматора, второй вход и

0

5

соответственно к выходу суммы и выходу переноса d/2-го сумматора чет- вертой группы, второй вход 1-го (, d/2+l) сумматора которой подключен к выходу (1+1)-го сумматора пятой группы, выходы старших и младших разрядов i-x умножителей второй и третьей групп подключены соответственно к первому и второму входам i-x сумматоров соответственно шестой и седьмой групп, выходы которых подключены к вторым входам i-x сумматоров соответственно второй и первой групп, а выходы переносов i-x сумматоров шестой и седьмой групп подключены к входам переноса i-x сумматоров

фиг. 2

Разряды 1ходного omcwmo Х(1г)

у.

инверсные разояОы аадеотонноео шсчета Х() Фиг.З

соответственно групп.

8 шестой и седьмой

Редактор А.Маковская

Составитель А Баранов

Техред М.Додык Корректор О.Кравцова

Заказ 6364/42 .Тираж 671Подписное

ВНИИ11И Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.

Фие.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой фильтрации | 1985 |

|

SU1363248A1 |

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

| Устройство для вычисления свертки | 1989 |

|

SU1679502A1 |

| Устройство для цифровой фильтрации с автоматической регулировкой усиления | 1988 |

|

SU1509935A1 |

| Устройство для вычисления быстрого преобразования Фурье с основанием 3 | 1985 |

|

SU1302292A1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1987 |

|

SU1418745A1 |

| Цифровой фильтр | 1989 |

|

SU1693613A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Устройство для вычисления рекуррентных соотношений | 1989 |

|

SU1683032A1 |

Изобретение относится к в.ычис- лительной технике и информационно- измерительным системам и может быть использовано в системах для цифровой обработки сигналов, в частности изображений. Цель изобретения - повышение точности работы устройства Поставленная цель достигается за счет того, что в состав устройства входят сумматоры 1, 8, элемент задержки. 2, группы сумматоров 3, 6,7, группа элементов задержки 4, группа умножителей 5 и блок элементов И 9. 5 ил. CR Д71 , Л 1/7. 00 o со ю со yinf -ю 11

| Авторское свидетельство СССР № 758166, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Rabiner L.R, Schafer R,Wo Recursive and nonrecursive realization of digital filters designed Ъу frequency sampling technigues | |||

| - IEEE Trans, audio and electro-acoustics, 1971, V AU-19, № 3, p | |||

| Мяльно-трепальный станок для обработки тресты лубовых растений | 1922 |

|

SU200A1 |

Авторы

Даты

1987-12-30—Публикация

1985-11-20—Подача