ft

Йд о

fD

ОО

сд

Изобретение относится к цифровой обработке сигналов, в частности цифровой фильтрации, и может быть использовано в различных цифровых устройствах, например, для обработки случайных процессов.

Цель изобретения - повьппение быстродействия устройства.

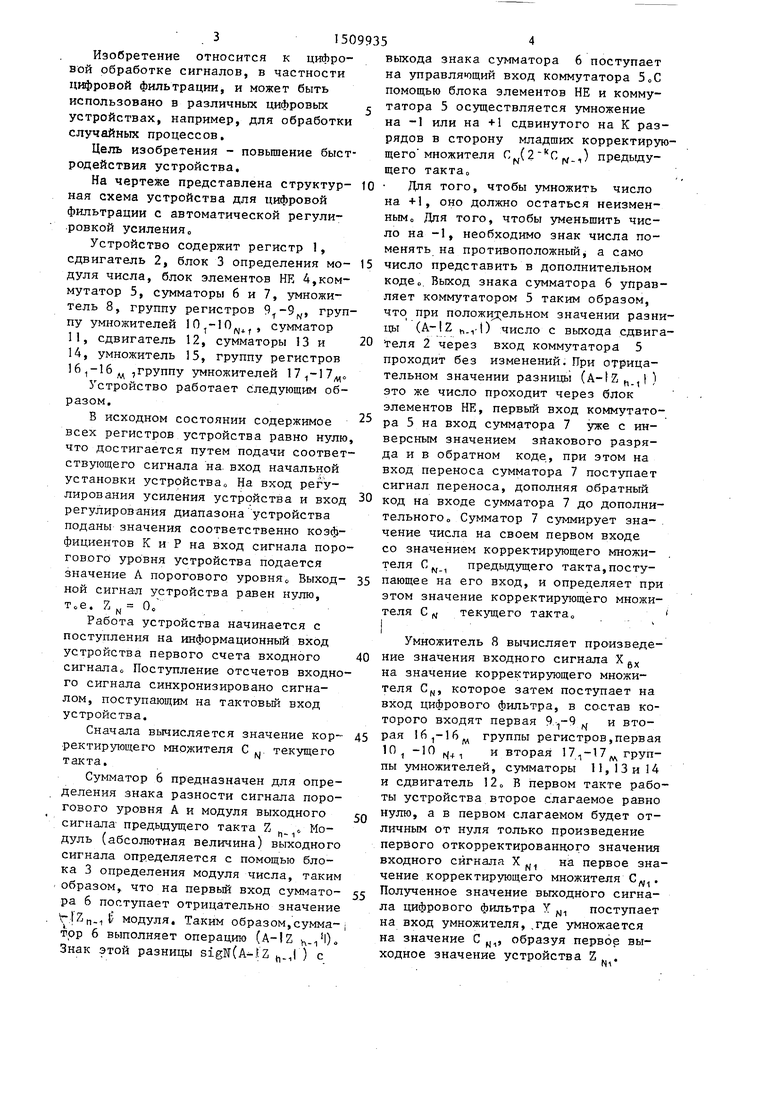

На чертеже представлена структур- ная схема устройства для цифровой фильтрации с автоматической регулировкой усиленияо

Устройство содержит регистр 1, сдвигатель 2, блок 3 определения мо- дуля числа, блок элементов НК 4,коммутатор 5, сумматоры 6 и 7, умножитель 8, группу регистров , группу умножителей , сумматор 11, сдвигатель 12, сумматоры 13 и 14, умножитель 15, группу регистров 16,-16 ,группу з ножителей 17,-17,o

З стройство работает следующим образом,

В исходном состоянии содержимое всех регистров устройства равно нулю что достигается путем подачи соответствующего сигнала на. вход начальной установки устройства На вход регулирования усиления устройства и вход регулирования диапазона устройства поданы значения соответственно коэффициентов К и Р на вход сигнала порогового уровня устройства подается значение А порогового уровнЯо Выход- ной сигнал устройства равен нулю, Тое, Z О/ .

Работа устройства начинается с поступления на информационный вход устройства первого счета входного сигнала Поступление отсчетов входного сигнала синхронизировано сигналом, поступающим на тактовый вход устройства.

ректирующего множителя С . текущего такта.

Сумматор 6 предназначен для определения знака разности сигнала порогового уровня А и модуля выходного сигнала предыдущего такта Z Мо50

Сначала вычисляется значение кор- 45 Р группы регистров,первая

10 -10 и вторая группы умножителей, сумматоры 11, 13и 4 и сдвигатель 12„ В первом такте работы устройства второе слагаемое равно нулю, а в первом слагаемом будет отличным от нуля только произведение первого откорректированного значения входного сигнала X на первое значение корректирующего множителя С, Полученное значение выходного сигнала цифрового фильтра Y , поступает на вход умножителя, .где умножается на значение С ,, образуя первое выходное значение устройства Z .

дуль (абсолютная величина) выходного сигнала определяется с помощью блока 3 определения модуля числа, таким образом, что на первый вход суммато- 55 ра б поступает отрицательно значение . ,Zf,.it модуля. Таким образом,сумма-j тор 6 выполняет операцию (A-IZ h-i 0. Знак этой разницы sigN(A-{Z n-J ) с

выхода знака сумматора 6 поступает на управляющий вход коммутатора 5„С помощью блока элементов НЕ и коммутатора 5 осуществляется умножение на -1 или на +1 сдвинутого на К разрядов в сторону младщих корректирующего множителя С( р,) предыдущего такта

Для того, чтобы умножить число на +1, оно должно остаться неизменным Для того, чтобы уменьщить число на -1, необходимо знак числа поменять на противоположный, а само число представить в дополнительном коде о. Выход знака сумматора 6 управляет коммутатором 5 таким образом, что при положиз ельном значении разницы (A-IZ n,vt) число с выхода сдвига- теля 2 через вход коммутатора 5 проходит без изменений. При отрицательном значении разницы (A-IZ (,.,() это же число проходит через блок элементов НЕ, первый вход коммутатора 5 на вход сумматора 7 уже с инверсным значением зйакового разряда и в обратном коде., при этом на вход переноса сумматора 7 поступает сигнал переноса, дополняя обратный код на входе сумматора 7 до дополнительного Сумматор 7 суммирует зна- . чение числа на своем первом входе со значением корректирующего множи- , теля С предыдущего такта,поступающее на его вход, и определяет при этом значение корректирующего множителя GN текущего такта

Умножитель 8 вычисляет произведение значения входного сигнала X на значение корректирзтощего множителя С|, которое затем поступает на вход цифрового фильтра, в со-став которого входят первая и втоНа этом первый такт работы устройства заканчивается. Во втором такте на информационный вход устройства поступает значение второго отсчета входного сигнала, значение корректирующего множителя Cfj , предьщущего такта заносится в регистр .1 и начинается процесс вычисления текущего а также значений X.

значения С

N

N

Ч.

И

-м«

Формула

изобретения Устройство для цифровой фильтрации с автоматической регулировкой усиления,содержащее первый сумматор, первый умножитель, коммутатор и блок элементов НЕ, выход которого подключен к первому информационному входу коммутатора, выход которого подключен к первому информационному входу первого сумматора, отличающееся тем, что, с целью повышения быстродействия, в него введены второй, третий,, четвертый и пятый сумматоры, второй умножитель,первый и второй сдвигатели, блок определения модуля числа, первая группа из N регистров, вторая группа из М регистров (N,M - целые числа, определяющие порядок фильтра), первая группа из N+1 умножителе-й, вторая группа из М умножителей, регистр, выход которого подключен к второму информационному входу первого сумматора и информа ционному входу первого сдвигателя,выход которого подключен к входу блока элементов НЕ и второму информационному входу коммутатора, управляющий

25

jj вторые входы

выход которого подключен к первому входу третьего сумматора, выход кото- рого подключен к информационному вхо- ду второго сдвигателя, выход которого подключен к первому входу четвертого сумматора, выход которого подключен к информационному входу первого регистра второй группы и второму

0 входу второго умножителя, выход которого является выходом устройства,информационным входом которого является второй вход первого умножителя, выход li-ro (i Г, -i) регистра, первой

15 группы подключен, к информационному входу (i+l)ro регистра первой группы и первому входу (i+l)-ro умножителя первой группы, выход которого подключен к (i+l)-My входу третьего

20 сумматора, (N4-1 )-й вход которого подключен к выходу (N+l)-ro умножителя первой группы, первый вход которого подключен к выходу N-ro регистра первой группы, выход j-ro (,M-l) регистра второй группы подключен к информационному входу (j+l)-ro регистра второй группы и первому входу j-ro умножителя первой грзтпы,выход которого подключен к j-му входу пятого сумматора, выход которого подключен к второму входу четвертого сумматора, выход М-го регистра второй группы подключен к первому вхо- .ду М-го умножителя второй группы,

1-го () и К-го

30

(к 1, М) умножителей первой и

вторые входы

второй групп являются соответственно 1-м и Км входами задания коэффициентов соответственно первой и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для умножения по модулю М=2 @ -1 | 1986 |

|

SU1383339A1 |

| Устройство для цифровой фильтрации с регулируемым коэффициентом передачи | 1990 |

|

SU1734106A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Арифметическое устройство для цифровой фильтрации с автоматической регулировкой усиления | 1979 |

|

SU881987A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Цифровое устройство для преобразования координат | 1981 |

|

SU960808A1 |

| Устройство для умножения | 1990 |

|

SU1789981A1 |

Изобретение относится к цифровой обработке сигналов , в частности, цифровой фильтрации, и может быть использовано в различных цифровых устройствах, например, для обработки случайных процессов. Цель изобретения - повышение быстродействия. Поставленная цель достигается за счет того, что в состав устройства входят регистр 1, сдвигатель 2, блок 3 определения модуля числа, блок 4 элементов НЕ, коммутатор 5, сумматоры 6 и 7, умножитель 8, группа регистров 91...9N, группа умножителей 101...10N+1, сумматор 11, сдвигатель 12, сумматоры 13 и 14, умножитель 15, группа регистров 161...16M и группа умножителей 171...17M. 1 ил.

вход которого соединен с входом пере- 40 второй групп устройства, входами заноса первого сумматора и подключен к выходу знака второго сумматора,первый вход которого подключен к выходу блока вычисления модуля числа,выход которого подключен к выходу второго умножителя, первый вход которого сое- дргаен с информационным входом регистра, первым входом первого умножителя и подключен к выходу первого сумматора, выход первого умножителя подключен к информационному входу первого регистра первой группы и первому входу первого умножителя первой группы.

Дания усиления и диапазона которого являются управляющие входы соответственно первого и второго сдвигате- лей, тактовые входы регистров первой

45 и второй групп и регистра соединены между собой и являются тактовым входом устройства, входом начальной установки которого являются соединенные между собой установочные входы

50 регистров первой и второй групп и регистра, а второй вход второго сумматора является входом задания порогового уровня устройства

40 второй групп устройства, входами заДания усиления и диапазона которого являются управляющие входы соответственно первого и второго сдвигате- лей, тактовые входы регистров первой

45 и второй групп и регистра соединены между собой и являются тактовым входом устройства, входом начальной установки которого являются соединенные между собой установочные входы

50 регистров первой и второй групп и регистра, а второй вход второго сумматора является входом задания порогового уровня устройства

| Цифровой фильтр с регулируемым коэффициентом передачи | 1978 |

|

SU734711A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство для цифровой фильтрации с автоматической регулировкой усиления | 1979 |

|

SU881987A1 |

Авторы

Даты

1989-09-23—Публикация

1988-01-19—Подача