Изобретение относится к импульсной технике и может быть использовано в аналого-цифровых преобразователях и цифровых измерительных приборах.

Цель изобретения - повышение быстродействия и расширение области применения устройства.

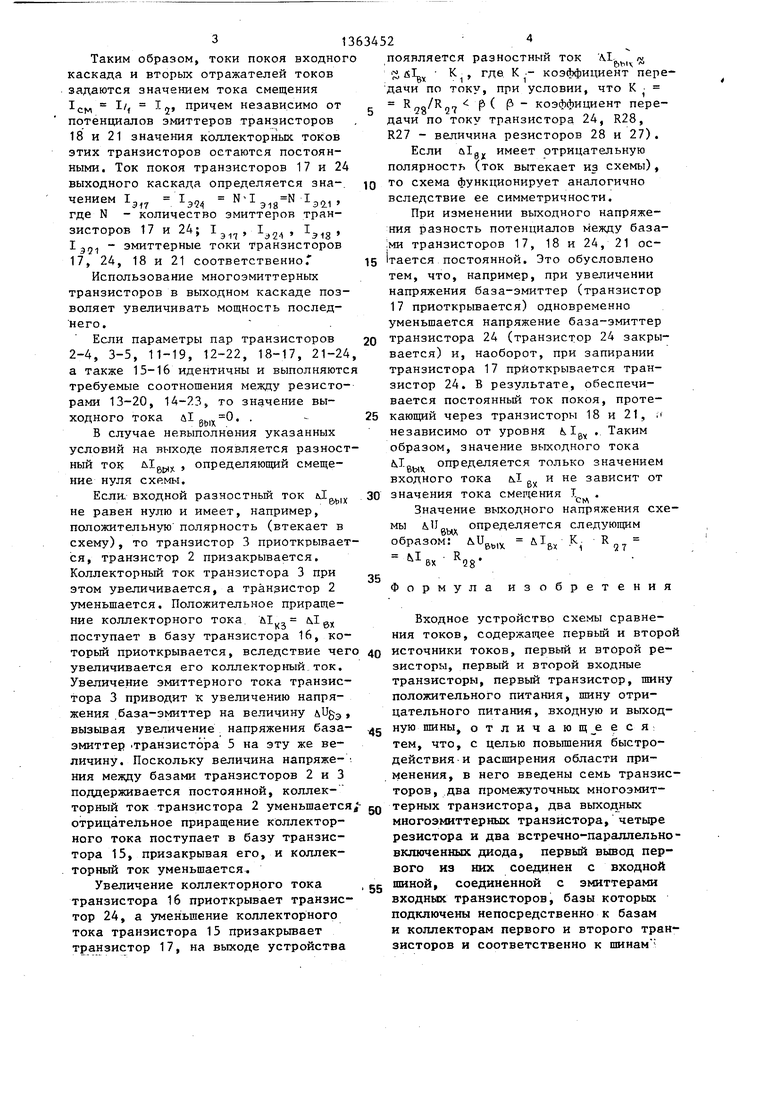

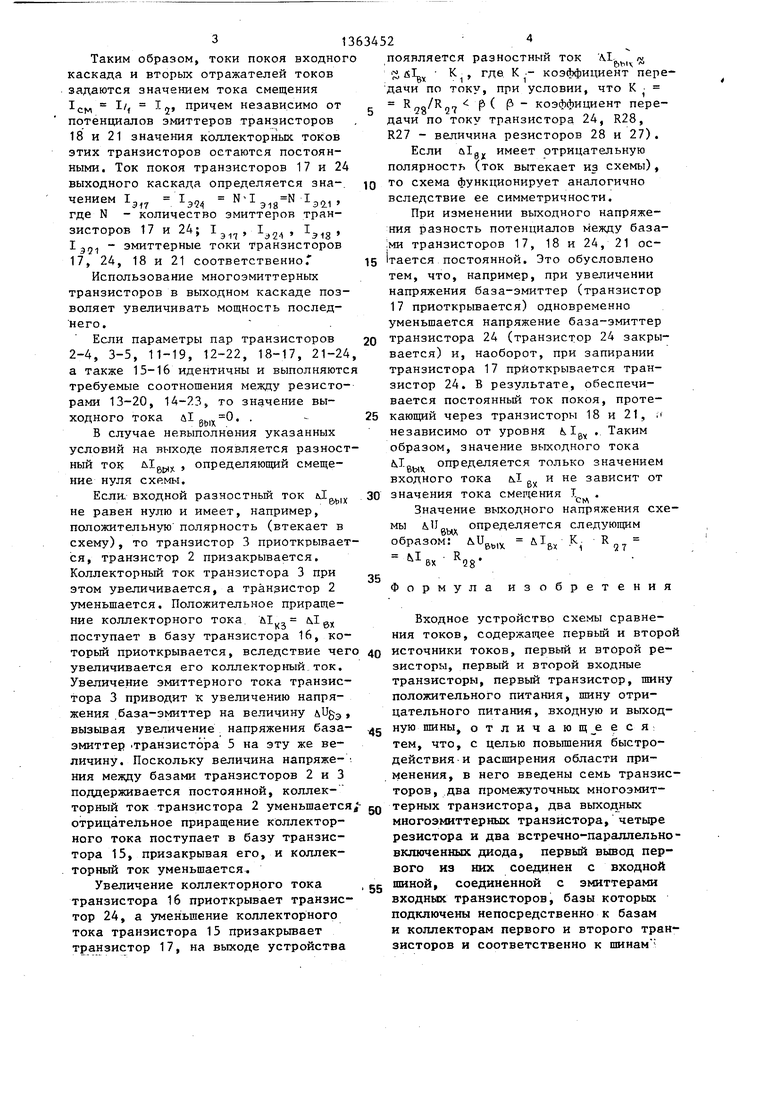

На чертеже представлена принципиальная схеме входного устройства схемы сравнения токов.

Входное устройство схемы сравнения токов содержит входную шину 1, соединенную с эмиттерами входных транзисторов 2 и 3, базы которьпс .подключены непосредственно к базам и коллекторам первого 4 и второго 5 транзисторов и соответственно к шинам 6 и 7 положительного и отрицательного

питания. через первый 8 и второй 9 ис- 20 , то через коллекторы входных транзисторов 2 и 3 протекают соответственно токи 1-,2 ; I rilgj. .Данные токи поступают на входы схем первых отражателей токов. Ток 1 поступает

25 на вход отражателя тока, собранного на третьем транзисторе 11, третьем резисторе 13, промежуточном много- эмиттерном транзисторе 19, третьем резисторе 20 и пятом транзисторе 15,

30 а ток 1 - на вход отражателя тока, собранного на четвертом транзисторе 12, втором резисторе 14, промежуточ- . ном многоэмиттерном транзисторе 22, четвертом резисторе 23 и шестом тран35 зисторе 16, Резисторы 13, 20 и 14, 13 используются для уменьшения влияния температурного дрейфа напряжения база - эмитгер транзисторов 11, 19 и 12, 22 соответственно. Через коллек-

40 торы транзисторов 15 и 16 протекают токи I и 1, поступающие соотточники тока а эмиттеры подключены к шине 10 нулевого потенциала, при этом коллекторы входных транзисторов 2 и 3 подключены соответственно к коллекторам третьего 11 и четвертого 12 транзисторов, эмиттеры которых подключены соответственно через первьй резистор 13 к пшне 6 положительного питания и второй резистор 14 к шине 7 отрицательного питания, и базам пятого 15 и шестого 16 транзисторов, причем коллектор пятого транзистора 15 соединен с базой первого выходного многоэмиттерного транзистора 17, коллектором соединенного с шиной 6 положительного питания, и базой седьмого транзистора 18, коллектор которого соединен с эмиттером пятого транзистора 15, базой третьего транзистора 11 и базой первого промежуточного многозмиттерного транзистора 19, эмиттеры которого подсоединены к шине 6 положительного потенциала через третий резистор 20, а эмиттер седь.ветственно в базы транзисторов 18 и-21, являющиеся вторыми отражателями токов, а также в базы транзисто- мого транзистора 18 подключен к эмит- 45 Р и 24, образующих двухтактный теру восьмого транзистора 21, кол- выходной каскад. Через коллекторы лектор которого соединен с эмиттером транзисторов 18 и 21 цротекают токи шестого транзистора 16, базой четвер- I g и поступающие соответственно на тра:нзисторы 20 и 22 в диодном 5Q вк:1ючении.

того транзистора 12, базой и коллектором второго промежуточного многоэмиттерного транзистора 22, эмиттеры которого подключены к шине 7 отрицательного питания через четвертый резистор 23, при этом коллектор шесИспользование такого принципа построения схемы позволяет за счет действия местной отрицательной обраттого транзистора 16 соединен с база- gg ной связи по постоянному току полуми восьмого транзистора 21 и второго выходного многоэмиттерного транзистора 2А, коллектор которого соединен с шиной 7 отрицательного питания, а

чить следующее значение: 1, эг

эз 320/- сга laiJ где k - количество эмиттеров транзисторов 20 и 22.

эмиттеры непосредственно подсоединены к эмиттерам первого выходного многоэмиттерного транзистора 17 и аы- ходной шине, через пятый резистор 27 - к шине 10 нулевого потенциала и через параллельно включенные .шестой резистор 28 и параллельно-встречно включенные диоды 29 и 30 - к входной шине 1,

Входное устройство схемы сравнения токов работает следующим образом.

Если входной разностный ток , 1„

ВХ

равен нулю, то через эмиттеры вход- ных транзисторов 2 и 3 протекает ток, значение которого I 1 oil , .где 1/1, токи первого и второго

источников ток-аГ Iсм смещения. Так как токи баз пренебрежимо маИспользование такого принципа построения схемы позволяет за счет действия местной отрицательной обратной связи по постоянному току получить следующее значение: 1, эг

эз 320/- сга laiJ где k - количество эмиттеров транзисторов 20 и 22.

31

Таким образом, токи покоя входног каскада и вторых отражателей токов задаются значением тока смещения -см I/, I , причем независимо от потенциалов эмиттеров транзисторов 18 и 21 значения коллекторных токов этих транзисторов остаются постоянными. Ток покоя транзисторов 17 и 24 выходного каскада определяется зна-. чением 1.„ .„. . N I

ЭП . Э74 Э18 32.1

где N - количество эмиттеров транзисторов 17 и 24; 1э,т, 1з2.1 Э18 -391 эмиттерные токи Транзисторов 17, 24, 18 и 21 соответственно.

Использование многоэмиттерных транзисторов в выходном каскаде позволяет увеличивать мощность послед- него.

Если параметры пар транзисторов 2-4, 3-5, 11-19, 12-22, 18-17, 21-24 а также 15-16 идентичны и выполняютс требуемые соотношения между резисторами 13-20, 14-7.3, то значение выходного тока ul

В случае невыполнения указанных условий на выходе появляется разностный ток определяюпщй смещение нуля схемы.

Есла входной разностный ток Ip,,| не равен нулю и имеет, например, положительную полярность (втекает в схему), то транзистор 3 приоткрывается, транзистор 2 призакрывается. Коллекторный ток транзистора 3 при этом увеличивается, а транзистор 2 уменьшается. Положительное приращение коллекторного тока ul.,

Ко 5

поступает в базу транзистора 16, который приоткрывается, вследствие чег увеличивается его коллекторный.ток. Увеличение эмиттерного тока транзистора 3 приводит к увеличению напряжения база-эмиттер на величину л%э вызывая увеличение напряжения база- эмиттер .транзистора 5 на эту же величину. Поскольку величина напряже- ния между базами транзисторов 2 и 3 поддерживается постоянной, коллекторный ток транзистора 2 уменьшаетсяотрицательное приращение коллекторного тока поступает в базу транзистора 15, призакрывая его, и коллекторный ток уменьшается.

Увеличение коллекторного тока транзистора 16 приоткрывает транзистор 24, а уменьшение коллекторного тока транзистора 15 призакрывает транзистор 17, на выходе устройства

0

0

появляется разностный ток лЬ /v И filg К, где К - коэффициент пере дачи по току, при условии, что К R „/R Р ( Р коэффициент передачи по току транзистора 24, R28, R27 - величина резисторов 28 и 27). Если al

gj, имеет отрицательную полярность (ток вытекает из схемы), то схема функционирует аналогично вследствие ее симметричности.

При изменении выходного напряжения разность потенциалов между база- ;Ми транзисторов 17, 18 и 24, 21 ос5 тается постоянной. Это обусловлено тем, что, например, при увеличении напряжения база-эмиттер (транзистор 17 приоткрывается) одновременно уменьшается напряжение база-эмиттер транзистора 24 (транзистор 24 закрывается) и, наоборот, при запирании транзистора 17 приоткрывается транзистор 24. В результате, обеспечивается постоянный ток покоя, проте5 кающий через транзисторы 18 и 21, и независимо от уровня Таким образом, значение выходного тока

М

бых

определяется только значением

входного тока &.I „„ и не зависит от

6х значения тока смещения I

с (Л

Значение выходного напряжения схе5

мы 4.U-. , определяется следующим

оиЛ

образом: &и„

М

6Х

R,

BblX

&1с. к, R

бх

97

Q8 Формула

изобретения

Входное устройство схемы сравнения токов, содержащее первый и второй

источники токов, первый и второй резисторы, первый и второй входные транзисторы, первый транзистор, шину положительного питания, шину отрицательного питания, входную и выход шины, отличающ ееся; тем, что, с целью повьшения быстродействия -и расширения области применения, в него введены семь транзисторов, два промежуточных многоэмиттерных транзистора, два выходных многоэмиттерных транзистора, четыре резистора и два встречно-параллельно- включенных диода, первый вывод первого из них соединен с входной

шиной, соединенной с эмиттерами входных транзисторов, базы которых подключены непосредственно к базам и коллекторам первого и второго транзисторов и соответственно к шинам

положительного и отрицательного питания через первый и второй источники тока, а эмиттеры подключены к шине

. нулевого потенциала, при этом коллекторы входных транзисторов подключены соответственно к коллекторам третьего и четвертого транзисторов, эмиттеры которых подключены соответственно через первый резистор к шине положительного питания и второй резистор к шине отрицательного питания и базам пятого и шестого транзисторов, причем коллектор пятого транзистора соединен с базой первого выходного многоэмиттерного транзистора, коллектором соединенного с шиной положительного питания и базой

.седьмого транзистора, коллектор которого соединен с эмиттером пятого транзистора, базой третьего транзистора и базой первого промежуточного многоэмиттерного транзистора, эмиттеры которого подсоединены к шине

Редактор А.Огар

Составитель Н.Маркин

Техред М.Дидык Корректор И.Муска.

Заказ 6379/53 Тираж .900 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва Ж-35, Раушская наб. д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

положительного потенциала через третий резистор, а эмиттер седьмого транзистора подключен к эмиттеру восьмого транзистора, коллектор которого соединен с эмиттером шестого транзистора, базой четвертого тран- зистора, базой и коллектором второго промежуточного многоэмиттерного транQ зистора, эмиттеры которого подключены к шине отрицательного питания через четвертый резистор, при этом коллектор шестого транзистора соединен с базой восьмого транзистора и

5 базой второго выходного многоэмиттерного транзистора, коллектор которого соединен с шиной отрицательного питания, а эмиттеры непорредственно подсоединены к эмиттерам первого вы0 родного многоэмиттерного транзистора и выходной шине и через лятый резистор - к шине нулевого потенциала и второму вьгооду первого диода, параллельно которому подключен шестой.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования разрядных токов записи | 1988 |

|

SU1550581A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Входное устройство схемы сравнения токов | 1988 |

|

SU1554128A1 |

| Входное устройство схемы сравнения токов | 1989 |

|

SU1626360A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Троичный триггер на ТТЛ-инверторах | 1989 |

|

SU1727197A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324103A1 |

| Многофункциональный пороговый модуль | 1973 |

|

SU493030A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ ЗВУКОВОЙ ЧАСТОТЫ | 1993 |

|

RU2115224C1 |

| Генератор задержанных импульсов | 1990 |

|

SU1750037A1 |

Изобретение относится к импульсной технике и может быть использовано в аналого-цифровых преобразоватеj лях и в цифровых измерительных приборах .цель изобретения - повышение быстродействия и расширение области применения достигается за счет введения в устройство семи транзисторов, двух промеясуточных многоэмиттерных транзисторов, двух многоэмиттерных транзисторов, четьфех резисторов и двух встречно-параллельно включенных диодов. Использование многозмиттерных транзисторов в выходном каскаде позволяет существенно увеличить его мощность. Устройство содержит входную шину 1, входные транзисторы 2 и 3, тины 6 и 7 положительного и отрицательного питания, источник тока 8 и 9, шину 10 нулевого потенциала, промежуточные многоэмиттерные транзисторы 19 и 22, выходные многоэмиттерные транзисторы 17 и 24, выходную .шину 26, транзисторы, резисторы и диоды. 1 йп. i (Л

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| IEEE JOURNAL OF SOLID-STATE CIRCUITS, vol | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

Авторы

Даты

1987-12-30—Публикация

1985-07-08—Подача