1 1

Изобретение относится к импульсной технике и может быть использовано при построении выходных каскадов различных цифровых ИС.

Цель изобретения - повышение быст- родействия путем снижения межкаскадных задержек распространения сигнала

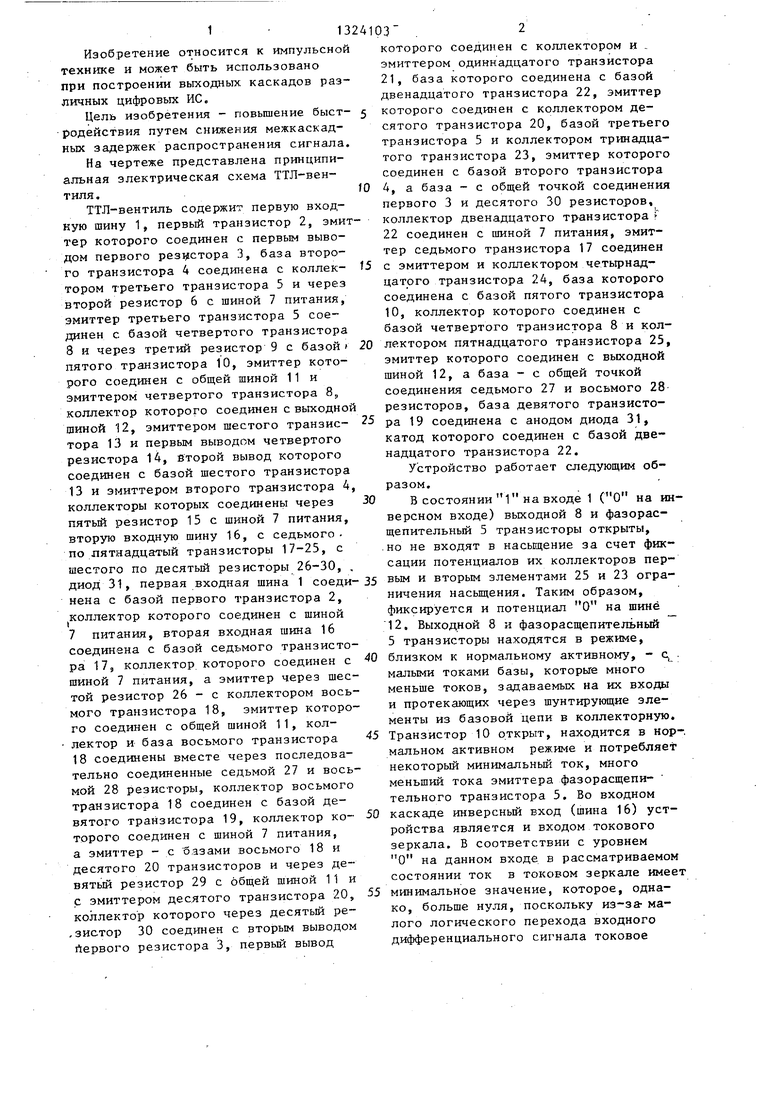

На чертеже представлена принципиальная электрическая схема ТТЛ-вентиля,

ТТЛ-вентиль содержит первую входную шину 1, первый транзистор 2, эмиттер которого соединен с первым выводом первого резистора 3, база второго транзистора 4 соединена с коллектором третьего транзистора 5 и через второй резистор 6 с шиной 7 питания, эмиттер третьего транзистора 5 соединен с базой четвертого транзистора 8 и через третий резистор 9 с базой пятого транзистора 10, эмиттер которого соединен с общей шиной 11 и эмиттером четвертого транзистора 8,, коллектор которого соединен с выходной шиной 12, эмиттером шестого транзис- тора 13 и первым выводом четвертого резистора 14, второй вывод которого соединен с базой шестого транзистора 13 и эмиттером второго транзистора 4 коллекторы которых соединены через пятьй резистор 15 с шиной 7 питания, вторую входную шину 16, с седьмого. по пятнадцатый транзисторы 17-25, с шестого по десятый резисторы 26-30, , диод 31, первая входная шина 1 соедииена с базой первого транзистора 2, коллектор которого соединен с шиной 7 питания, вторая входная шина 16 соединена с базой седьмого транзистора 17, коллектор, которого соединен с шиной 7 питания, а эмиттер через шестой резистор 26 - с коллектором восьмого транзистора 18, эмиттер которого соединен с общей шиной 11, коллектор и база восьмого транзистора 18 соединены вместе через последовательно соединенные седьмой 27 и восьмой 28 резисторы, коллектор восьмого транзистора 18 соединен с базой девятого транзистора 19, коллектор которого соединен с шиной 7 питания, а эмиттер - с базами восьмого 18 и десятого 20 транзисторов и через девятый резистор 29 с общей шиной 11 и с эмиттером десятого транзистора 20, коллектор которого через десятый ре- ,зистор 30 соединен с вторым выводом rtepBoro резистора 3, первый вывод

fO

t5

0

4

5

2535 0 5 5

0

0

103 2

которого соединен с коллектором и эмиттером одиннадцатого транзистора 21, база которого соединена с базой двенадцатого транзистора 22, эмиттер которого соединен с коллектором десятого транзистора 20, базой третьего транзистора 5 и коллектором тринадцатого транзистора 23, эмиттер которого соединен с базой второго транзистора 4, а база - с общей точкой соединения первого 3 и десятого 30 резисторов, коллектор двенадцатого транзистора Г 22 соединен с шиной 7 питания, эмиттер седьмого транзистора 17 соединен с эмиттером и коллектором четырнадцатого транзистора 24, база которого соединена с базой пятого транзистора 10, коллектор которого соединен с базой четвертого транзистора В и коллектором пятнадцатого транзистора 25, эмиттер которого соединен с выходной шиной 12, а база - с общей точкой соединения седьмого 27 и восьмого 28 резисторов, база девятого транзистора 19 соединена с анодом диода 31, катод которого соединен с базой двенадцатого транзистора 22.

Устройство работает следующим образом.

В состоянии 1 на входе 1 (О на инверсном входе) выходной 8 и фазорас- щепительный 5 транзисторы открыты,

.но не входят в насьщение за счет фиксации потенциалов их коллекторов первым и вторым элементами 25 и 23 ограничения насыщения. Таким образом, фиксируется и потенциал О на шине 12. Выходной 8 и фазорасщепительный 5 транзисторы находятся в режиме, близком к нормальному активному, - с. малыми токами базы, которые много меньше токов, задаваемых на их входы и протекающих через шунтирующие элементы из базоЕЮй цепи в коллекторную. Транзистор 10 открыт, находится в нормальном активном режиме и потребляет некоторый минимальный ток, много меньший тока эмиттера фазорасщепи- тельного транзистора 5. Во входном каскаде инверсный вход (шина 16) устройства является и входом токового зеркала. В соответствии с уровнем О на данном входе в рассматриваемом состоянии ток в токовом зеркале имеет минимальное значение, которое, однако, больше нуля, поскольку из-за- малого логического перехода входного дифференциального сигнала токовое

зеркало полностью не выключается. КИМ образом, минимальная часть тока ответвляется в выходной транзистор 20 токового зеркала, большая часть его поступает в базу фазорасщепитель- ного транзистора 5.

В состоянии.О на шине 1 (1 на шине 16), фазорасщепительный 5 и выходной 8 транзисторы заперты. Высокий

Та-

потенциал коллектора запертого фазо- Ш осуществляется положительным фронтом

расщепительного транзистора 5 задает через выходной эмиттерный повторитель (транзисторы 4 и 13) выходной уровень 1. Во входном каскаде токовое зеркало включено за счет уровня 1 на своем входе. Выходной ток токового зеркала при этом увеличивается за счет падения напряжения на резисторе 30.

импульса на шине 1. Работа каскада на транзисторе 23 аналогична, за исключением того, что, поскольку тре15

буется ускоряющий втекающий ток вместо вытекающего, то сигнал снимается не с коллектора транзистора, а с эмиттера. Ускорение включения фазорасщепительного транзистора 5 приводит к ускорению включения и входного В динамическом режиме при переклю-20 транзистора 2: ток эмиттера фазорас- 1 „ л ..„ „,.„- щепительного транзистора 5 полностью

поступает в базу выходного 8, не ответвляясь в нагрузочньш элемент, в качестве которого в предлагаемом устройстве служит каскад на транзисторе 10, потребляющий пренебрежимо малый статический ток.

Таким образом, предлагаемое уст 0 на шине ti t II

чении из состояния 1 в 1 (соответственно из О в 1 на шине 16) запираются транзисторы 5 и 8. Для ускорения запирания при управлении по их базовым цепям требуется 25 увеличение токов, вытекающих из их баз. Для фазорасщепительного транзистора 5 такой ток обеспечивается включением токового зеркала входного каскада положительным фронтом импульса 30 действие по сравнению с прототипом на шине 16. Для выходного транзистора при одинаковой потребляемой мощности.

ройство имеет более высокое быстро8 ускоряющий ток включения обеспечивается запуском транзистора 25 за счет того же положительного фронта импульса на шине 16. Положительный 35 фронт передается через эмиттерный повторитель (транзистор 18) и емкостный элемент (на транзисторе 24) на базу транзистора tO и включает его. благодаря емкостной связи ускоряющий 40 ток протекает импульсно, что повьш1а- ет быстродействие без затрат статической мощности. Транзистор 10 работает без принудительного насыщения благодаря использованию резистора 9 45 в качестве фиксирующего элемента: данный резистор по мере спада импуль- са ускоряющег о тока позволяет быстро выключить ненасьш1енный транзистор 10 по базовой цепи и устранить затяги- 50 вание фронта нарастания импульса в коллекторной цепи фазорасщепительного транзистора 5, который, в свою очередь, определяет фронт импульса переключения из О в 1 на шине 12,-55

При переключении из состояния О в 1 на шине 1 (из 1 в О на шине 16) фазорасщепигельный 5 и выg

/ИОЗ4

ходной 8 транзисторы включаются.

Для ускорения их включения требуется увеличение тока, втекающего в их базы. Для фазорасщепительного транзистора это достигается уменьшением тока токового зеркала- на счет отрицательного фронта импульса на инверсном входе (шина 16), а также за счет включения транзистора 23, Запуск его

импульса на шине 1. Работа каскада на транзисторе 23 аналогична, за исключением того, что, поскольку тредействие по сравнению с прототипом при одинаковой потребляемой мощности

ройство имеет более высокое быстрочто достигается благодаря повьш5ению эффективности цепочек ускорения за счет более раннего запуска их от входного каскада. Такой запуск цепочек ускорения реализован благодаря построению входного каскада с управлением дифференциальным входным сигналом на эмиттерных повторителях с источником тока на токовом зеркале. Указанный входной каскад позволяет без введения дополнительных цепочек, потребляющих ток, реализовать цепи смещения для шунтирующих элементов. Это.обеспечивает возможность использования предлагаемого ТТЛ-вентиля в качестве выходного каскада (для которого в отличие от внутренних вентилей допускается увеличение числа элементов, но требуется эффективное переключение значительной внешней нагрузки),

Формула изобретения

ТТЛ-вентиль, содержащий первую входную шину, первый транзистор,эмиттер которого соединен с первым выводом первого резистора, база второго

транзистора соединена с коллектором третьего транзистора и через второй резистор с шиНой питания, эмиттер третьего транзистора соединен с базой четвертого тразистора и через третий резистор с базой пятого транзистора, эмиттер которого соединен с общей шиной и эмиттером четвертого транзистора, коллектор которого соединен с выходной шиной, эмиттером шестого транзистора и первым выводом четвертого резистора, второй вывод которого соединен с базой шестого транзистора и эмиттером второго транзистора, кол- пекторы которых соединен;ы через пя- тЫй резистор с шиной питания, о т .л и ч а ю щ и и с я тем, что, с целью повышения быстродействия, в него введены вторая входная шина, седьмой., восьмой, девятый, десятый,

одиннадцатый, двенадцатый, тринадца- тьй, четырнадцатый и пятнадцатый Транзисторы, шестой, седьмой, восьмой, девятый и десятый резисторы, диод, первая входная шина соединена с базой первого транзистора, коллектор которого соединен с шиной питания, вторая входная шина соединена с базой седьмого транзистора, коллектор которого соединен с шиной питания, а эмиттер через шестой резистор - с коллектором восьмого транзистора, эмиттер которого соединен с общей шиной, коллектор и база восьмого транзистор соединены вместе через последовательно соединенные седьмой

Редактор А.Огар Заказ 2972/56

Составитель А.Кабанов

Техред Л.Олнйнык Корректор М.Демчик

Тираж 901Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

и восьмой резисторы, коллектор восьмого транзистора соединен с базой девятого транзистора, коллектор которого соединен с шиной питания, а эмиттер - с базами восьмого и десятого транзисторов и через девятый резистор с общей шиной и с эмиттером десятого транзистора, коллектор которого через десятый резистор соединен с вторым выводом первого резистора, первый вывод которого соединен с коллектором и эмиттером одиннадцатого транзистора, база которого соединена с базой двенадцатого транзистора, эмиттер которого соединен с коллектором десятого транзистора, базой третьего транзистора и коллектором тринадцатого транзистора, эмиттер которого соединен с базой второго транзистора, а база - с общей точкой соединения первого и десятого резисторов, коллектор двенадцатого транзистора соединен с шиной питания, эмиттер седьмого транзистора соединен с эмиттером и коллектором четырнадцатого транзистора, база которого соединена с базой пятого транзистора, коллектор которого соединен с базой четвертого транзистора и с коллектором пятнадцатого транзистора, эмиттер которого соединен с выходной шиной, а база - с общей точкой соединения седьмого и восьмого резисторов, база девятого транзистора соединена с анодом диода, катод которого соединен с базой двенадцатого транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТТЛ-вентиль | 1985 |

|

SU1324104A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324105A1 |

| Входное устройство схемы сравнения токов | 1988 |

|

SU1554128A1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2349024C1 |

| Стереодекодер для системы стереофонического радиовещания с полярной модуляцией | 1991 |

|

SU1748269A1 |

| Входное устройство схемы сравнения токов | 1988 |

|

SU1529434A1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Инверторная схема с минимальной асимметрией | 1985 |

|

SU1311016A1 |

| Устройство для резервного энергоснабжения блока оперативного запоминающего устройства | 1985 |

|

SU1336154A1 |

Изобретение относится к области импульсной техники, может быть использовано при построении выходных каскадов различных цифровых ИС. Цель изобретения - повышение быстродействия - достигается путем снижения межкаскадных задержек распространения сигнала. Устройство содержит транзисторы 2, 4, 5, 8, 10, 13, резисторы 3, 6, 9, 14, 15. Для достижения поставленной цели в устройство введены транзисторы 17-25, резисторы 26-30, диод 31. 1 ип. /о (Л с 00. to ijlik О Од -L ff

| Зарубежная электроника, 1984, 6, с | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| Патент США № 4321490, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-07-15—Публикация

1985-09-20—Подача