Изобретение относится к вычислительной технике и автоматике и может быть использовано в качестве устройств для формирования двухполяр- ных разрядных токов записи оперативного запоминающего устройства.

Целью изобретения является повышение быстродействия устройства.

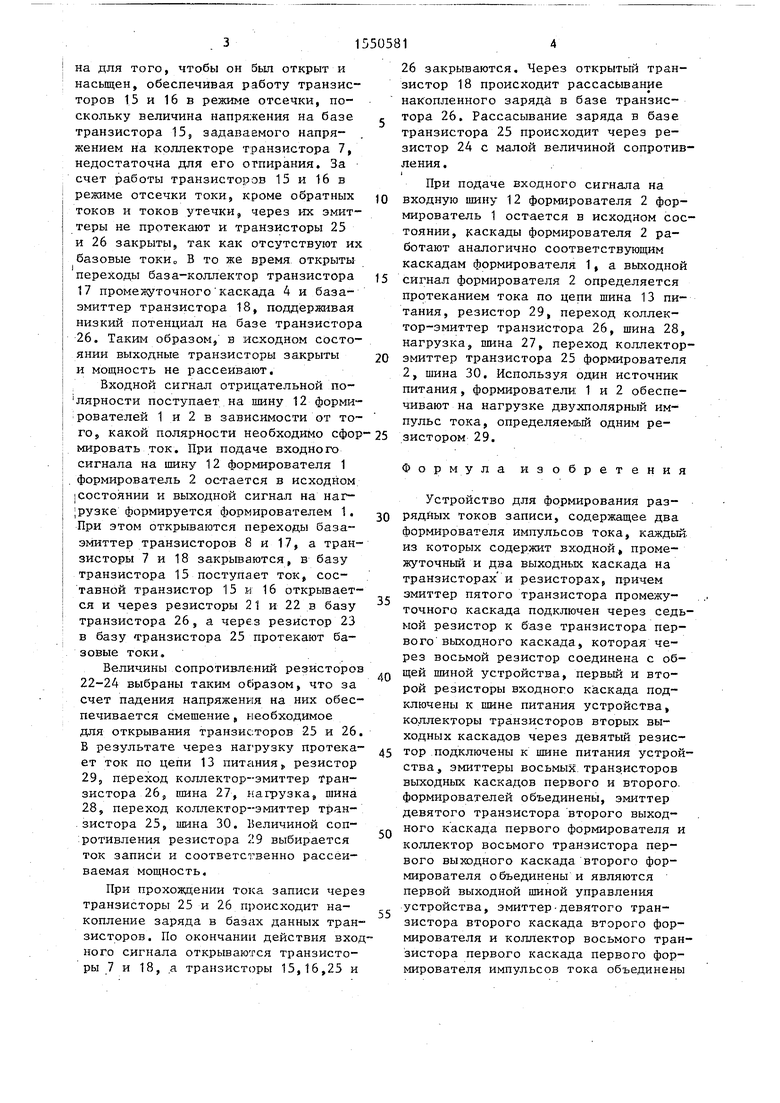

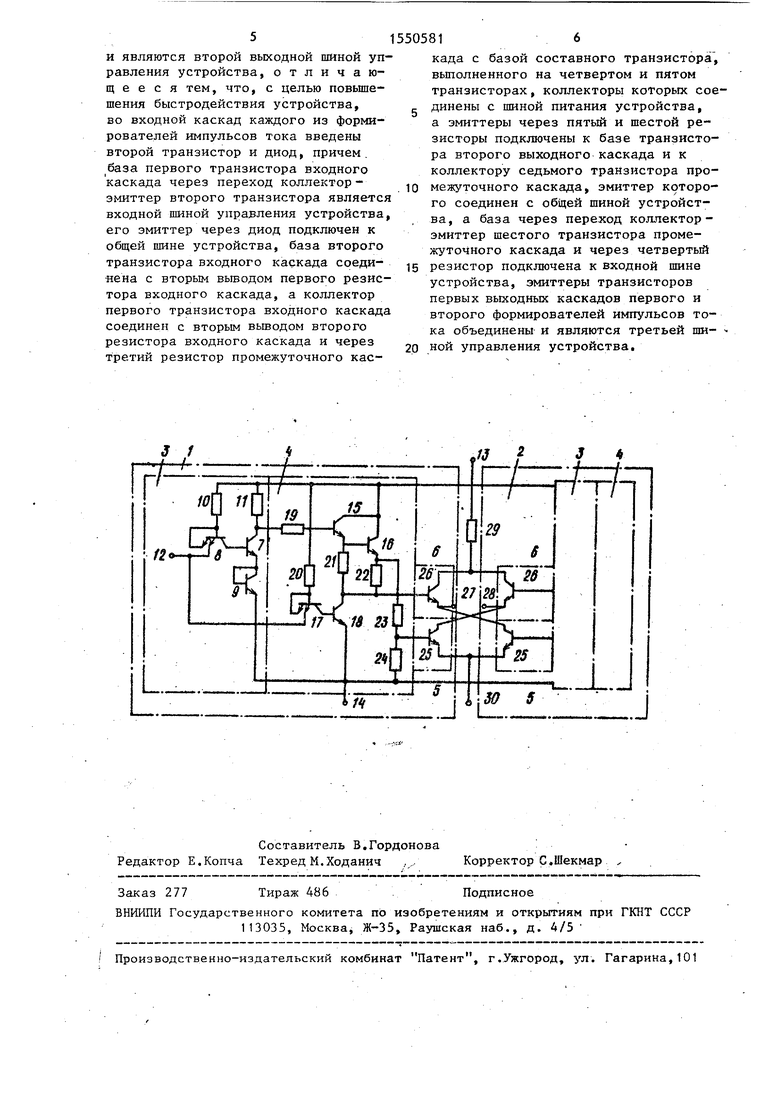

На чертеже представлена электрическая схема устройства для формирования разрядных токов записи.

Устройство содержит два идентичных формирователя 1 и 2 импульсов тока. Каждый формирователь 1 и 2 содержит одинаковые входной каскад 3, промежуточный каскад 4, первый 5 и второй 6 выходные каскады. Входной каскад 3 содержит первый транзистор

7,второй многоэмиттерный транзистор

8,транзистор 9 в диодном включении, первый 10 и второй 11 резисторы, входную шину 12 управления устройства, шину 13 питания и общую шину 14

устройства. Промежуточный каскад 4 содержит составной транзистор, выполненный на четвертом 15 и пятом 16 транзисторах, многоэмиттерный шестой транзистор 17, ключевой седьмой транзистор 18, третий 19, четвертый 20, пятый 21, шестой 22, седьмой 23 и восьмой 24 резисторы.

Первый 5 и второй 6 выходные каскады содержат восьмой 25 и девятый 26 транзисторы. Устройство также имеет первую выходную шину 27 управления, вторую выходную шину 28, резистор 29 и выходную шину 30 уп- равления.

i

Устройство работает следующим образом.

В исходном состоянии при отсутствии входных сигналов на шине 12 формирователей 1 и 2 открыт переход база-коллектор транзистора 8, величина базового тока транзистора 7 достаточ§

(Л

ел ел

ел

эо

на для того, чтобы он был открыт и насыщен, обеспечивая работу транзисторов 15 и 16 в режиме отсечки, поскольку величина напрякения на базе транзистора 15, задаваемого напряжением на коллекторе транзистора 7, недостаточна для его отпирания. За счет работы транзисторов 15 и 16 в режиме отсечки токи, кроме обратных токов и токов утечки, через их эмиттеры не протекают и транзисторы 25 и 26 закрыты, так как отсутствуют их базовые токи0 В то же время открыты переходы база-коллектор транзистора 17 промежуточного каскада 4 и база- эмиттер транзистора 18, поддерживая низкий потенциал на базе транзистора 26. Таким образом, в исходном состоянии выходные транзисторы закрыты и мощность не рассеивают.

Входной сигнал отрицательной по- лярности поступает на шину 12 форми- рователей 1 и 2 в зависимости от того, какой полярности необходимо сформировать ток. При подаче входного сигнала на шину 12 формирователя 1 формирователь 2 остается в исходном Состоянии и выходной сигнал на нагрузке формируется формирователем 1. При этом открываются переходы база- эмиттер транзисторов 8 и 17, а транзисторы 7 и 18 закрываются, в базу транзистора 15 поступает ток, составной транзистор 15 и 16 открывается и через резисторы 21 к 22 в базу транзистора 26, а через резистор 23 в базу транзистора 25 протекают базовые токи.

Величины сопротивлений резисторов 22-24 выбраны таким образом, что за счет падения напряжения на них обеспечивается смешение, необходимое для открывания транзисторов 25 и 26. В результате через нагрузку протекает ток по цепи 13 питания,, резистор 299 переход коллектор-эмиттер транзистора 26, шина 27, нагрузка8 шина 28, переход коллектор-эмиттер транзистора 25, шина 30. Величиной сопротивления резистора 29 выбирается ток записи и соответственно рассеиваемая мощность.

При прохождении тока записи через транзисторы 25 и 26 происходит накопление заряда в базах данных транзисторов . По окончании действия входного сигнала открываются транзисторы 7 и 18, а транзисторы 15,16,25 и

26 закрываются. Через открытый транзистор 18 происходит рассасывание накопленного заряда в базе транзис- тора 26. Рассасывание заряда в базе транзистора 25 происходит через резистор 24 с малой величиной сопротивления .

При подаче входного сигнала на

входную шину 12 формирователя 2 формирователь 1 остается в исходном состоянии, каскады формирователя 2 работают аналогично соответствующим каскадам формирователя 1, а выходной

5 сигнал формирователя 2 определяется протеканием тока по цепи шина 13 питания, резистор 29, переход коллектор-эмиттер транзистора 26, шина 28, нагрузка, шина 27, переход коллектор0 эмиттер транзистора 25 формирователя 2, шина 30. Используя один источник питания, формирователи 1 и 2 обеспечивают на нагрузке двухполярный импульс тока, определяемый одним ре5 зистором 29.

Формула изобретения

Устройство для формирования раз- 0 рядных токов записи, содержащее два формирователя импульсов тока, каждый из которых содержит входной промежуточный и два выходных каскада на транзисторах и резисторах, причем

5

эмиттер пятого транзистора промежуточного каскада подключен через седьмой резистор к базе транзистора первого выходного каскада, которая через восьмой резистор соединена с обQ щей шиной устройства, первый и второй резисторы входного каскада подключены к шине питания устройства, коллекторы транзисторов вторых выходных каскадов через девятый резис5 тор подключены к шине питания устройства, эмиттеры восьмых транзисторов выходных каскадов первого и второго формирователей объединены, эмиттер девятого транзистора второго выход0 ного каскада первого формирователя и коллектор восьмого транзистора первого выходного каскада второго формирователя объединены и являются первой выходной шиной управления устройства, эмиттер девятого транзистора второго каскада второго формирователя и коллектор восьмого транзистора первого каскада первого формирователя импульсов тока объединены

и являются второй выходной шиной управления устройства, отличающееся тем, что, с целью повыше- шения быстродействия устройства, во входной каскад каждого из формирователей импульсов тока введены второй транзистор и диод, причем

база первого транзистора входного каскада через переход коллектор- эмиттер второго транзистора является входной шиной управления устройства, его эмиттер через диод подключен к общей шине устройства, база второго транзистора входного каскада соеди- нена с вторым выводом первого резистора входного каскада, а коллектор первого транзистора входного каскада соединен с вторым выводом второго резистора входного каскада и через третий резистор промежуточного каскада с базой составного транзистора, выполненного на четвертом и пятом транзисторах, коллекторы которых соединены с шиной питания устройства, а эмиттеры через пятый и шестой резисторы подключены к базе транзистора второго выходного каскада и к коллектору седьмого транзистора промежуточного каскада, эмиттер которого соединен с общей шиной устройства, а база через переход коллектор - эмиттер шестого транзистора промежуточного каскада и через четвертый резистор подключена к входной шине устройства, эмиттеры транзисторов первых выходных каскадов первого и второго формирователей импульсов тока объединены и являются третьей шиной управления устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Входное устройство схемы сранения токов | 1985 |

|

SU1363452A1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| Устройство формирования импульсов | 1986 |

|

SU1347170A1 |

| Импульсный стабилизатор постоянного напряжения | 1990 |

|

SU1777129A1 |

| Формирователь импульсов | 1990 |

|

SU1746519A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324103A1 |

| Логический элемент | 1988 |

|

SU1554136A1 |

| Транзисторный ключ | 1985 |

|

SU1283957A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324104A1 |

Изобретение относится к вычислительной технике и автоматике. Целью изобретения является повышение быстродействия устройства. Устройство содержит два идентичных формирователя импульсов тока, каждый из которых содержит одинаковые входной каскад, промежуточный каскад, два выходных каскада. Используя один источник питания, формирователи обеспечивают на нагрузке двухполярный импульс тока, определяемый одним резистором. 1 ил.

П

/J

У 4

| Специальные элементы запоминающих устройств ЭВМ на полупроводниковых приборах/Под ред | |||

| Е.И.Гальперина и А,Ю.Гордонова | |||

| М.: Советское радио, 1971, с | |||

| Ленточный тормозной башмак | 1922 |

|

SU337A1 |

| Устройство для формирования разрядных токов записи | 1975 |

|

SU546016A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-03-15—Публикация

1988-02-01—Подача