(54) СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для деления чисел | 1981 |

|

SU970356A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО МОДУЛЮ ТРИ | 1991 |

|

RU2011215C1 |

| Последовательный сумматор | 1983 |

|

SU1149248A1 |

| Накапливающий сумматор | 1990 |

|

SU1829031A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в арифметических устдойстеах ЭВМ и устройствах обработки цифровой информации.

Известен сумматор последовательного действия, состоящий из двух комбинационных полусумматоров, двух элементов задержки и трех элементов И 1 .

Недостатком его является большой объем оборудования.

Известен также сумматор последовательного действия, содержащий два комбинационных полусумматора, элемент задержки, элемент И и элемент ИЛИ 2 .

Недостатками его являются большой объем оборудования и низкое быстродействие, так как длительность одно- го такта сложения в нем определяется временем прохождения сигнала через четыре уровня логических схем и линию задержки.

Цель изобретения - изменение :аппаратурных затрат и повышение быстродействия сумматора.

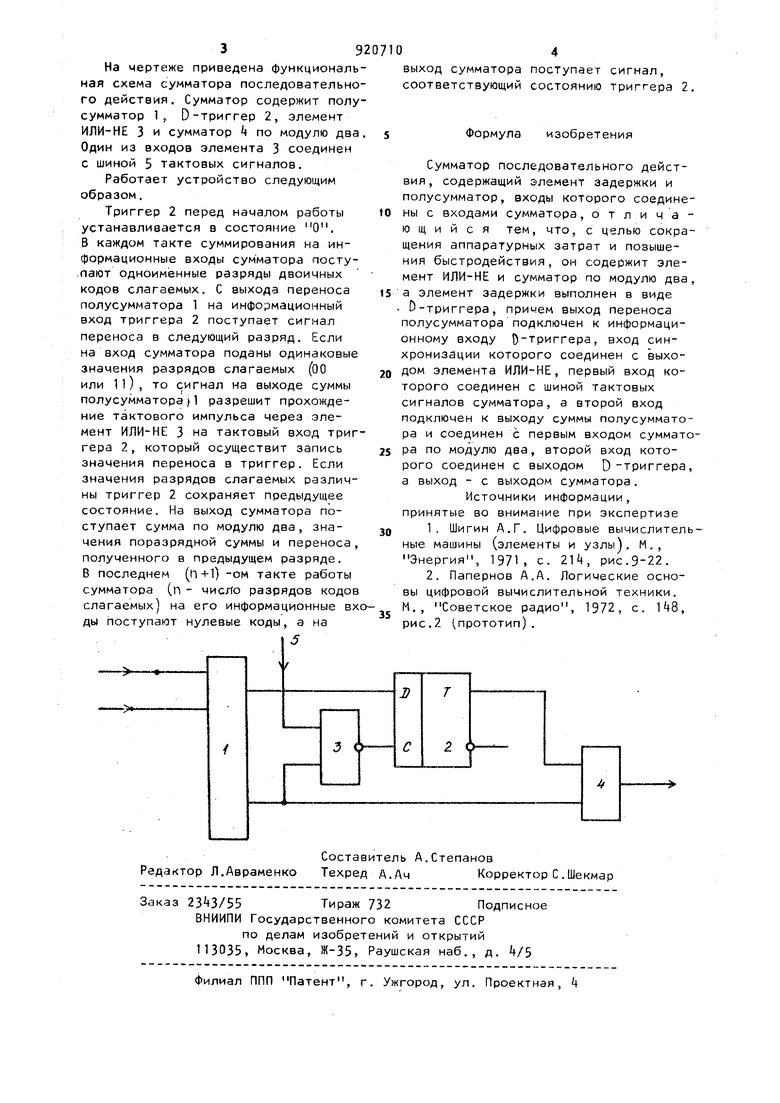

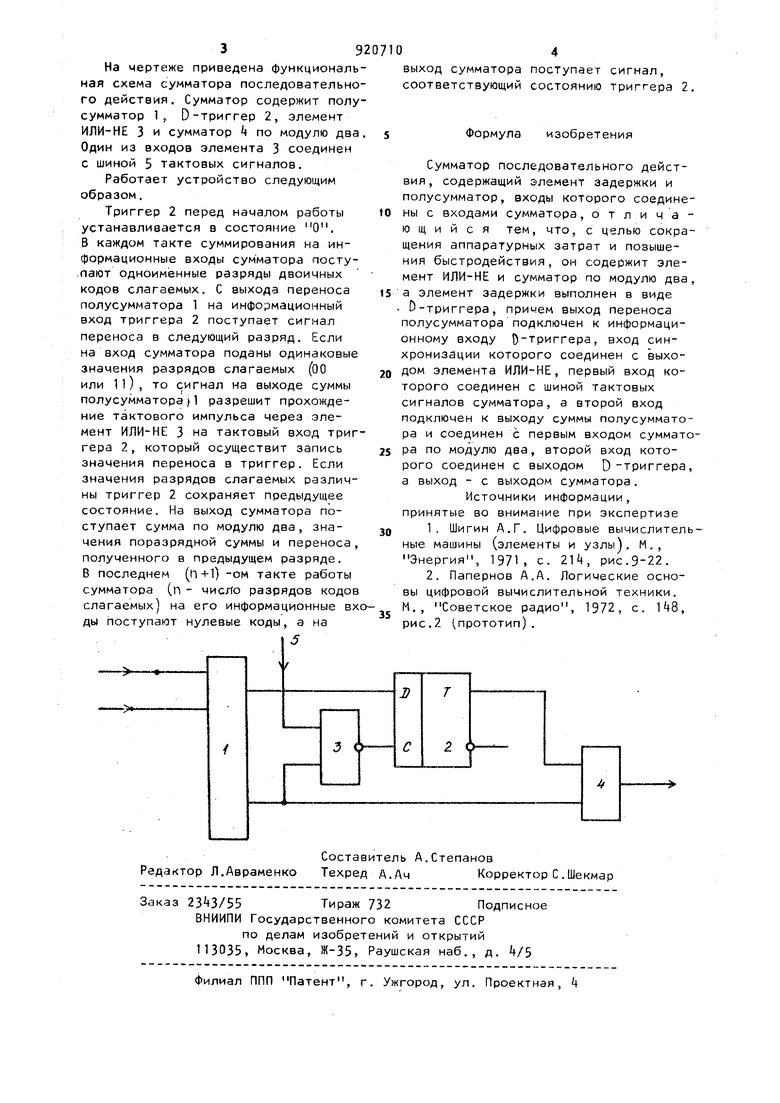

Указанная цель достигается тем, что сумматор последовательного действия, содержащий элемент задержки и полусумматор, входы которого соединены со входами сумматора, содержит также элемент ИЛИ-НЕ и сумматор по

10 модулю два, а элемент задержки выполнен в виде D-триггера, причем выход переноса полусумматора подключен к информационному входу О-триггера, вход синхронизации которого

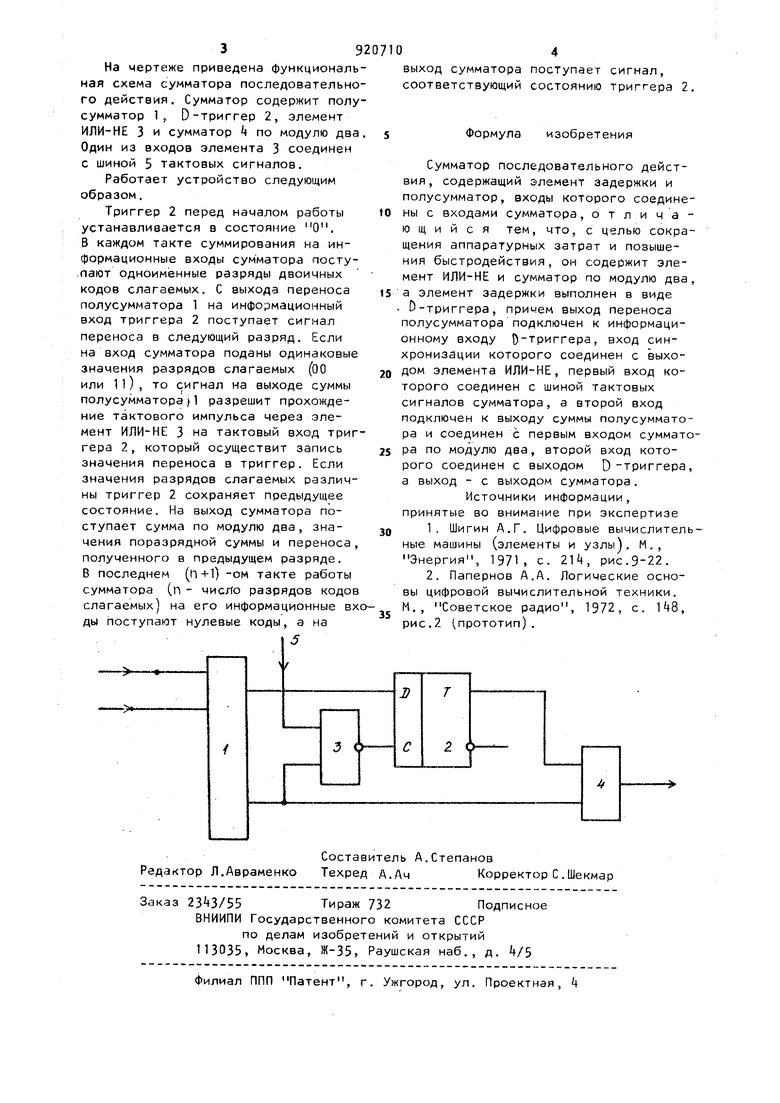

15 соединен с выходом элемента ИЛИ-НЕ первый вход которого соединен с шиной тактовых сигналов сумматора, а второй вход подключен к выходу суммы полусумматора и соединен е первым вхо20дом сумматора по модулю два, второй вход которого соединен с выходом D-триггера, а выход - с выходом сум.мато)а. 3 На чертеже приведена функциональ ная схема сумматора последовательно го действия. Сумматор содержит полу сумматор 1,, D-триггер 2, элемент ИЛИ-НЕ 3 и сумматор 4 по модулю два Один из входов элемента 3 соединен с шиной 5 тактовых сигналов. Работает устройство следующим образом. Триггер 2 перед началом работы устанавливается в состояние О, В каждом такте суммирования на информационные входы сумматора посту,пают одноимённые разряды двоичных кодов слагаемых, С выхода переноса полусумматора 1 на информационный вход триггера 2 поступает сигнал переноса в следующий разряд. Если на вход сумматора поданы одинаковые значения разрядов слагаемых (ОО или 11), то сигнал на выходе суммы полусумматора 11 разрешит прохождение тактового импульса через элемент ИЛИ-НЕ 3 на тактовый вход три гера 2, который осуществит запись значения переноса в триггер. Если значения разрядов слагаемых различ ны триггер 2 сохраняет предыдущее состояние. На выход сумматора поступает сумма по модулю два, значения поразрядной суммы и переноса полученного в предыдущем разряде, В последнем (П+1) -ом такте работы сумматора (п - число разрядов кодо слагаемых) на его информационные в ды поступают нулевые коды, а на 4 выход сумматора поступает сигнал, соответствующий состоянию триггера 2, Формула изобретения Сумматор последовательного действия, содержащий элемент задержки и полусумматор, входы которого соединены с входами сумматора, отличающийся тем, что, с целью сокращения аппаратурных затрат и повышения быстродействия, он содержит элемент ИЛИ-НЕ и сумматор по модулю два, а элемент задержки выполнен в виде D-триггера, причем выход переноса полусумматора подключен к информационному входу |)-триггера, вход синхронизации которого соединен с выходом элемента ИЛИ-НЕ, первый вход которого соединен с шиной тактовых сигналов сумматора, а второй вход подключен к выходу суммы полусумматора и соединен с первым входом сумматора по модулю два, второй вход которого соединен с выходом D Триггера, а выход - с выходом сумматора. Источники информации, принятые во внимание при экспертизе 1,Шигин А,Г. Цифровые вычислительные машины (элементы и узлы), М,, Энергия, 1971, с. 2U, рис,9-22, 2,Папернов А,А, Логические основы цифровой вычислительной техники, М,, Советское радио, 1972, с, U8, рис,2 (прототип),

Авторы

Даты

1982-04-15—Публикация

1980-07-18—Подача