Изобретение относится к автоматике и эычислительной технике и может быть использовано при построении преобразователей кода Грея, аналого-цифровых преобразователей и узлов контроля по четности.

Известно устройство для преобразования кода Грея в двоичный код, содержащее ряд последовательно соединенных полусумматоров 1.

Н остаток этого преобразователя сотоит в низком быстродействии.

Наиболее близким к предлагаемому изобретению по технической сущности и схемному решению является преобразователь кода Грея в двоичный код, содержащий входной регистр и группу полусумматоров, прямле и инверсные входы первых слагаемых которых соединен1| с прямыми и инверсны1«1 выходами соответствующих разрядов входного регистра, прямой и инверсный выходы переноса 1-го (1 2 -f п) полусумматора (где п - число разрядов кода Грея) соединены со входами второго слагаемого (1-1)-го полусумматора 2.

Недостаток известного преобразователя также состоит в низком быстродействии.

Цель изобретения - повыиение быстродействия преобразователя.

Поставленная цель достигается за счет того, что в преобразователь кода Грея в двоичный код, содержащий входной регистр и группу полусумматоров, прямые и инверсные входы первых слагаемых которых соединены с прямыми и- инверсными выходами соот0ветствующих разрядов входного регистра, прямой и инверсный выходы переноса 1-го (i 2 - п) полусумматора, где п - число разрядов кода Грея, соединены со входами второго слагаемого

5 (i-l)-oro полусумматора, введены источники логической единицы и логического нуля, два нагрузочных резистора и группа дифференциальных усилителей, первый и второй входы каждого из ко- .

0 торых сое данены с прягллми и инверсными выходам переноса соответствующего полусумматора, а выходы дифференциальных усилителей являются выходами преобразователя, выходы полусумматора

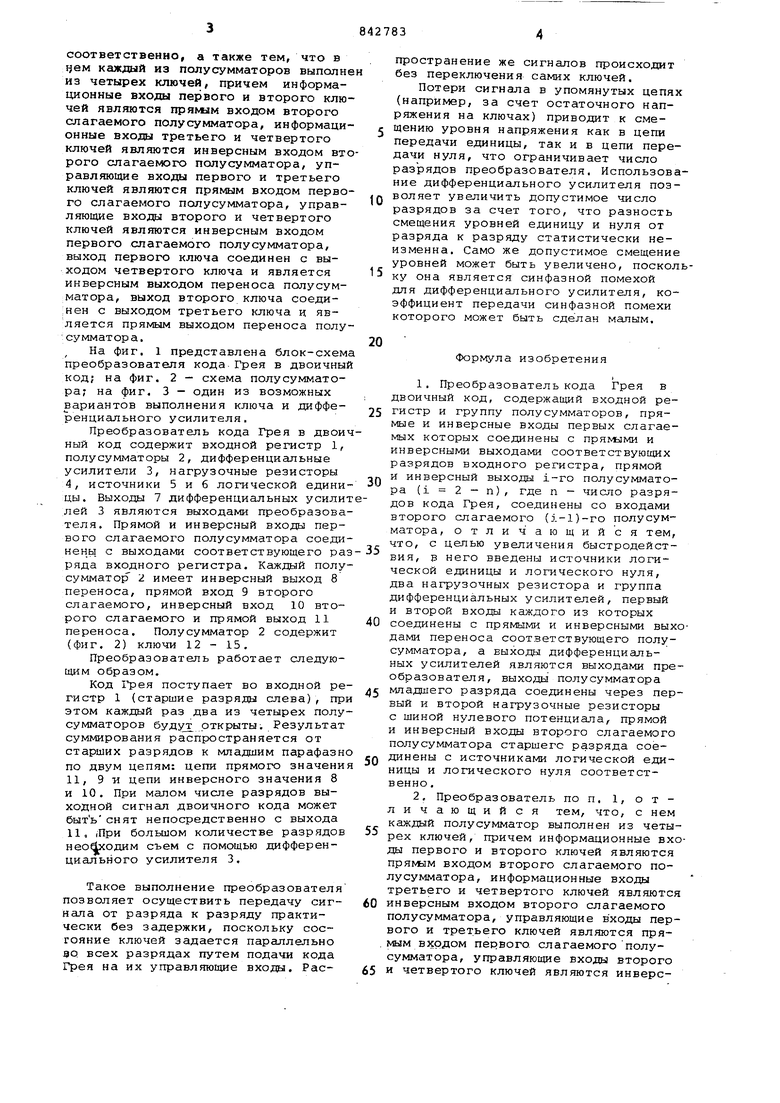

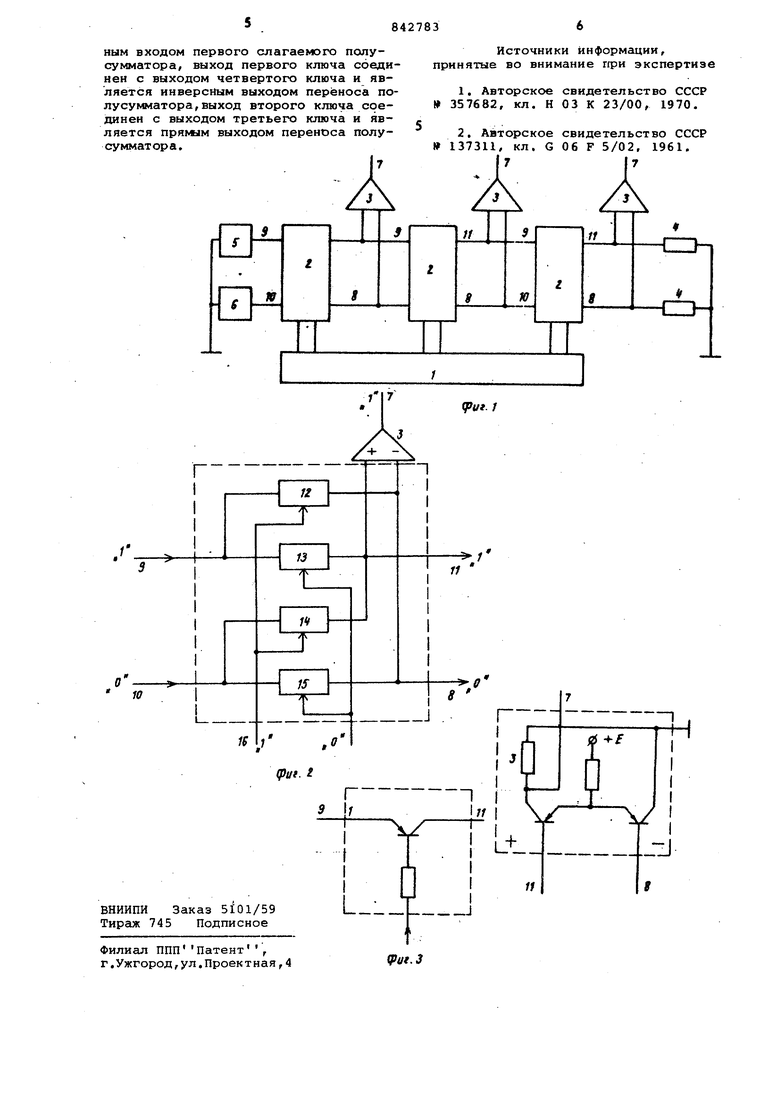

5 младшего разряда соединены через первый и второй резисторы с шиной нулевого потенциала, прямой и инверсный вход второго слагаемого полусумматора старшего разряда соединены со входами 0 логической единицы.и логического нуля соответственно, a также тем, что в (jeM каждый из полусумматоров выполне из четырех ключей, причем информационные входы первого и второго клю чей являются прямым входом второго слагаемого полусумматора, информационные входы третьего и четвертого ключей являются инверсным входом вто рого слагаемого полусумматора, управляющие входы первого и третьего ключей являются прямым входом перво го слагаемого полусумматора, управляющие входы второго и четвертого ключей являются инверсным входом первого слагаемого полусумматора, выход первого ключа соединен с выходом четвертого ключа и является инверсным выходом переноса полусумматора, выход второго ключа соединен с выходом третьего ключа и является прямЕлм выходом переноса полу сумматора. На фиг. 1 представлена блок-схем преобразователя кода Грея в двоичны код; на фиг. 2 - схема полусумматора; на фиг. 3 - один из возможных вариантов выполнения ключа и дифференциального усилителя. Преобразователь кода Грея в двои ный код содержит входной регистр 1, полусумматоры 2, дифференциальные усилители 3, нагрузочные резисторы 4, источники 5 и б логической едини цы. Выходы 7 дифференциальных усили лей 3 являются выходами преобразова теля. Прямой и инверсный входы первого слагаемого полусумматора соеди нены с выходами соответствующего ра ряда входного регистра. Каждый полу сумматор i имеет инверсный выход 8 переноса, прямой вход 9 второго слагаемого, инверсный вход 10 второго слагаемого и прямой выход 11 переноса. Полусумматор 2 содержит (фи г. 2) ключи 12 - 15. Преобразователь работает следующим образом. Код Грея поступает во входной ре гистр 1 (старшие разряды слева), пр этом каждый раз два из четырех полу сумматоров будуз ртк рыты i Результат суммирования распространяется от старших разрядов к младшим парафазн по двум цепям: цепи прямого значени 11, 9 и цепи инверсного значения 8 и 10. При малом числе разрядов выходной сигнал двоичного кода может бытьснят непосредственно с выхода 11. Щри большом количестве разрядов неофсодим съем с помощью дифференциального усилителя 3. Такое выполнение преобразователя позволяет осуществить передачу сигнала от разряда к разряду практически без задержки, поскольку состояние ключей задается паргшлельно эо. всех разрядах путем подачи кода Грея на их управляющие входы. Распространение же сигналов происходит без переключения самих ключей. Потери сигнала в упомянутых цепях (например, за счет остаточного напряжения на ключах) приводит к смещению уровня напряжения как в цепи передачи единицы, так и в цепи передачи нуля, что ограничивает число разрядов преобразователя. Использование дифференциального усилителя позволяет увеличить допустимое число разрядов за счет того, что разность смещения уровней единицу и нуля от разряда к разряду статистически неизменна. Само же допустимое смещение уровней может быть увеличено, поскольку она является синфазной помехой для дифференциального усилителя, ко- . эффициент передачи синфазной помехи которого может быть сделан малым. Формула изобретения 1.Преобразователь кода Грея в двоичный код, содержащий входной регистр и группу полусумматоров, прямые и инверсные входы первых слагаемых которых соединены с прямыми и инверсными выходами соответствующих разрядов входного регистра, прямой и инверсный выходы i-ro полусумматора (i 2 - п), где п - число разрядов кода Грея, соединены со входами второго слагаемого (i-l)-ro полусумматора, отличающийся тем, что, с целью увеличения быстродействия, в него введены источники логической единицы и логического нуля, два нагрузочных резистора и группа дифференциальных усилителей, первый и второй входы каждого из которых соединены с прямыми и инверсными выходами переноса соответствующего полусумматора, а выходы дифференциальных усилителей являются выходами преобразователя, выходы полусумматора младшего разряда соединены через первый и второй нагрузочные резисторы с шиной нулевого потенциала, прямой и инверсный входы второго слагаемого полусумматора старшего разряда соединены с источниками логической единицы и логического нуля соответственно. 2.Преобразователь по п. 1, отличающийся тем, что, с нем каждый полусумматор выполнен из четырех ключей, причем информационные входы первого и второго ключей являются прямлм входом второго слагаемого полусумматора, .информационные входы третьего и четвертого ключей являются инверсным входом второго слагаемого полусумматора, управляющие входы первого и третьего ключей являются прямым входом первого, слагаемогополусумматора, управляющие входы второго и четвертого ключей являются инверсным входом первого слагаемого полусумматора, выход первого ключа соединен с выходом четвертого ключа и является инверсным выходом переноса полу сукматора, выход второго ключа соединен с выходом третьего ключа и является прямым выходом переноса полусумматора.

Источники информации, принятые во внимание гфи экспертизе

1.Авторское свидетельство СССР 357682, кл. Н 03 К 23/00, 1970.

2.Авторское свидетельство СССР 137311, кл. G 06 Р 5/02, 1961.

|7

Авторы

Даты

1981-06-30—Публикация

1973-11-26—Подача