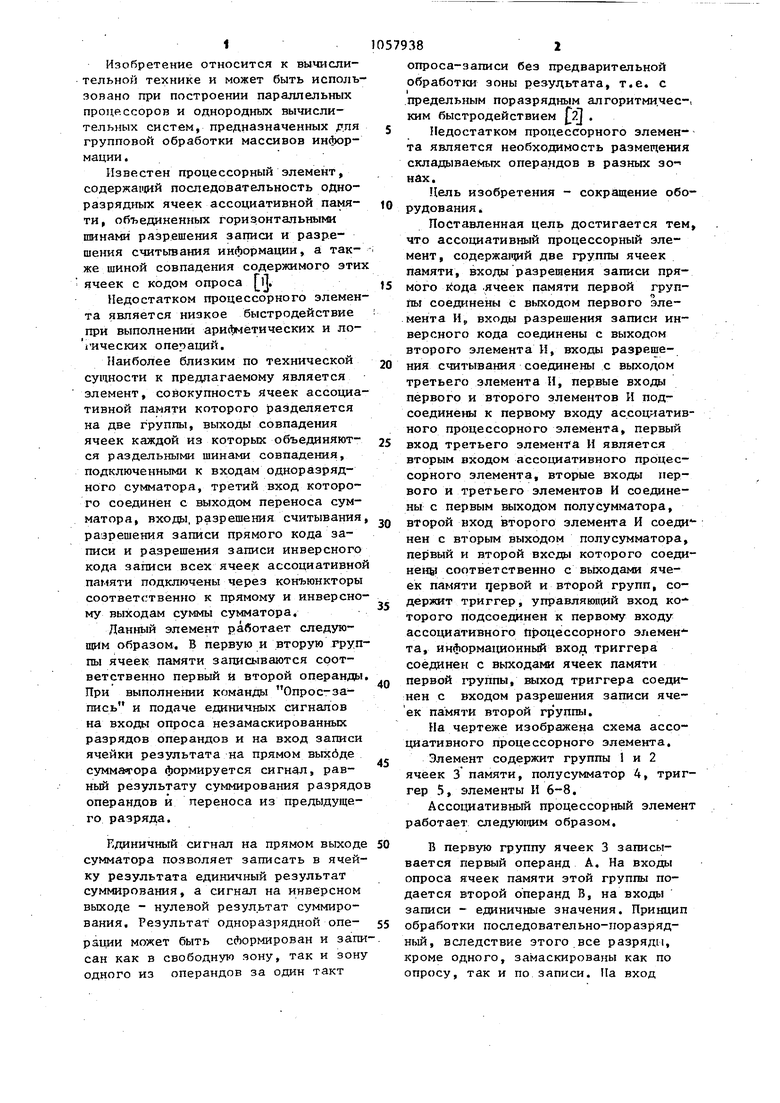

Изобретение относится к вычислительной технике и может быть исполь зовано при построении параллельных процр.ссоров и однородных вычислительных систем, предназначенных для групповой обработки массивов информации. Известен процессорный элемент, содержа1ций последовательность одноразрядных ячеек ассоциативной памяти , объединенных горизонтальными шинами разрешения записи и разрешения считьгаания информации, а также шиной совпадения содержимого эти ячеек с кодом опроса . Недостатком процессорного элемен та является низкое быстродействие при выполнении арифметических и логических операций. Наиболее близким по технической сущности к предлагаемому является элемент, совокупность ячеек ассоциа тивной памяти которого разделяется на две группы, выходы совпадения ячеек каждой из которых объединяются раздельными шинами совпадения, подключенными к входам одноразрядного сумматора, третий вход которого соединен с выходом переноса сумматора, входы, разрешения считывания разрешения записи прямого кода записи и разрешения записи инверсного кода записи всех ячеек ассоциативно памяти подключены через конъюнкторы соответственно к прямому и инверсно му выходам суммы сумматора. Данный элемент работает следуюш 1м образом. В первую и вторую груп пы ячеек памяти записываются соответственно первый и второй операнды При выполнении команды Опрос-запись и подаче единичных сигналов на входа.1 опроса незамаскированных разрядов операндов и на вход записи ячейки результата на прямом выхбде суммая ора формируется сигнал, равный результату суммирования разрядо операндов и переноса из предыдущего разряда. Единичный сигнал на прямом выход сумматора позволяет записать в ячейку результата единичный результат суммирования, а сигнал на инверсном выходе - нулевой результат суммирования. Результат одноразрядной операции может быть сформирован и запи сан как в свободную зону, так и зону одного из операндов за один такт 382 опроса-записи без предварительной обработ1си зоны резудьтата, т.е. с предельным поразрядным алгоритми.чес-, КИМ быстродействием Л . Недостатком процессорного элемента является необходимость размещения складываемых операндов в разных зо-нах. Цель изобретения - сокращение оборудования. Поставленная цель достигается тем, что ассоциативный процессорный элемент, содержа ций две группы ячеек памяти, входы разрешения записи прямого кода .ячеек памяти первой группы соединены с выходом первого элемента И„ входы разрешения записи инверсного кода соединены с выходом второго элемента И, входы разрешения считывания соединены с вьрсодом третьего элемента И, первые входа первого и второго элементов И подсоединены к первому входу ассоциативного процессорного элемента, первый вход третьего элемента И является вторым входом ассоциативного процессорного элемента, вторые входы первого и третьего элементов И соединены с первым выходом полусумматора, второй вход второго элемента И соеди нен с вторым выходом полусумматора, первый и второй входы которого соединень соответственно с выходами ячеек памяти цервой и второй групп, со- держит триггер, управляюп(ий вход ко- торого подсоединен к первому входу ассоциативного процессорного эх1емен та, информационный вход триггера соединен с выходами ячеек памяти первой 1Т)уппы, выход триггера соединен с входом разрешения записи ячеек памяти второй группы. На ч€ ртеже изображена схема ассоциативного процессорного элемента. Элемент содержит группы 1 и 2 ячеек 3 памяти, полусумматор 4, триггер 5, элементы И 6-8. Ассоциативный процессорный элемент работает следующим образом. в первую группу ячеек 3 записывается первый операнд А. На входы опроса ячеек памяти этой группы поается второй операнд В, на входы записи - единичные значения. Принцип обработки последовательно-поразрядый, вследствие этого все разряди, роме одного, замаскированы как по опросу, так и по записи. На вход

пррса ячейки переноса Р подается ну. значение, на вход записи - соответствуйщий, не маскируемый , разряд операнда В-Ь,

В таблице показана истинность одноразрядного сложения,

Опрос разряда Р производится по О, а на входа записи ячеек суммы и переноса подаются соответственно единичный сигнал и значение немаскируемого разряда операнда В.

При совпадении значений а и b на входе полусумматора 4, соединенном с выходами ячеек памяти первой группы, будет единичный сигнал, а на выходе совпадения ячейки переноса (на втором входе полусумматора) единичное значение будет при , В 3iTOM случае на прямом выходе полусумматора будет нулевое значение, на инверсном и на выходе триггера 5 единичные значения, что обеспечит запись О в ячейку результата и запись значений b в ячейку переноса. В случае на выходе совпадения

ячейки переноса будет нулевое значение, что обеспечит егшничное. значение сигнала на прямом выходе полу-, сумматора и запись 1 в разряд результата,

В случае несовпадения значений а и b на первом входе полусумматора 4 будет нулевое значение сигнала, а на втором входе полусумматора

в зависимости от значения Р будет единичное () или нулевое (). В первом случае с прямого выхода полусумматора на вход разрешения записи прямого кода ячейки результата поступит единичный сигнал, что

обеспечит запись единичного значеi ния в разряд cyMNbt, во втором случае - единичный сигнал поступит с инверсного выхода полусумматора 4

на вход разрешения записи инверсного кода, что обеспечит запись нулевого значения в разряд результата, В обоих случаях на выходе триггера 5 отсутствует единичный сигнал - содержимое ячейки переноса остается без изменения.

Таким образом, результат одноразрядной операции может быть сформирован и записан в зону результата одной

командой опроса-записи, т.е. с предельным алгоритмическим быстродействием, причем второй операнд подается непосредственно на входа опроса ячеек памяти, хранягаих значе ше

первого операнда, т.е. для его размещения не требуется зоны ассоциативной памяти.

Применение предлагаемого ассоциативного процессорного элемента

позволяет сократить на 30% разрядность специализированного accoiwaтивного решаю1цего поля вследствие экономичного выполнения операций типа вектор-скаляр.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессорный элемент | 1980 |

|

SU881757A1 |

| Процессорный модуль | 1978 |

|

SU700863A1 |

| Ассоциативный процессорный модуль | 1981 |

|

SU1015390A1 |

| Запоминающее устройство | 1989 |

|

SU1711229A1 |

| Ассоциативный процессорный элемент | 1980 |

|

SU879593A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для поиска информации в ассоциативной памяти | 1988 |

|

SU1617460A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU924754A1 |

АССОЦИАТИВНЫЙ ПРОЦЕССОРНЬП ЭЛЕМ1::НТ, содержащий две группы ячеек памяти, входы разрешения записи прямого кода ячеек памяти первой группы соединены с выходом первого элемента И, входы разрешения записи инверсного кода соединены с выходом второго элемента И, входы разрешения считывания соединены с выходом третьего элемента И, первые входы первого и второго элементов И подсоединены к первому входу ассоциативного процессорного элемента, первый вход третьего элемента И является вторым входом ассоциативного процессорного элемента, вторые входы первого и третьего элементов И соединены с первым выходом полусумматора, второй вход второго элемента И соединен с вторым выходом полусумматора, первый и второй которо- го соединены соответственно с выхо-. дами ячеек памяти первой и второй i групп, отличающийся тем, что, с целью сокраг(ения оборудова(Л ния, он содержит триггер, управляющий вход которого подсоединен к пер;вому входу ассоциативного процессорного элемента, инсЪормационный вход триггера соединен с вьпсодами ячеек памяти первой группы, выход триггера соединен с входом разрешения записи ячеек памяти второй группы. ел со : 00

Авторы

Даты

1983-11-30—Публикация

1982-09-29—Подача