Изобретение относится к технике связи и может быть использовано в аппаратуре контроля достоверности передаваемой информации и проверки качества канала передачи без перерыва сеанса связи для однополярных сигналов в кодах CMI, DMI, BIF и т.п., передаваемых по волоконно-оптическим, проводным или радиоканалам связл.

Целью изобретения является повышение быстродействия устройства и уменьшение его- структурной сложности.

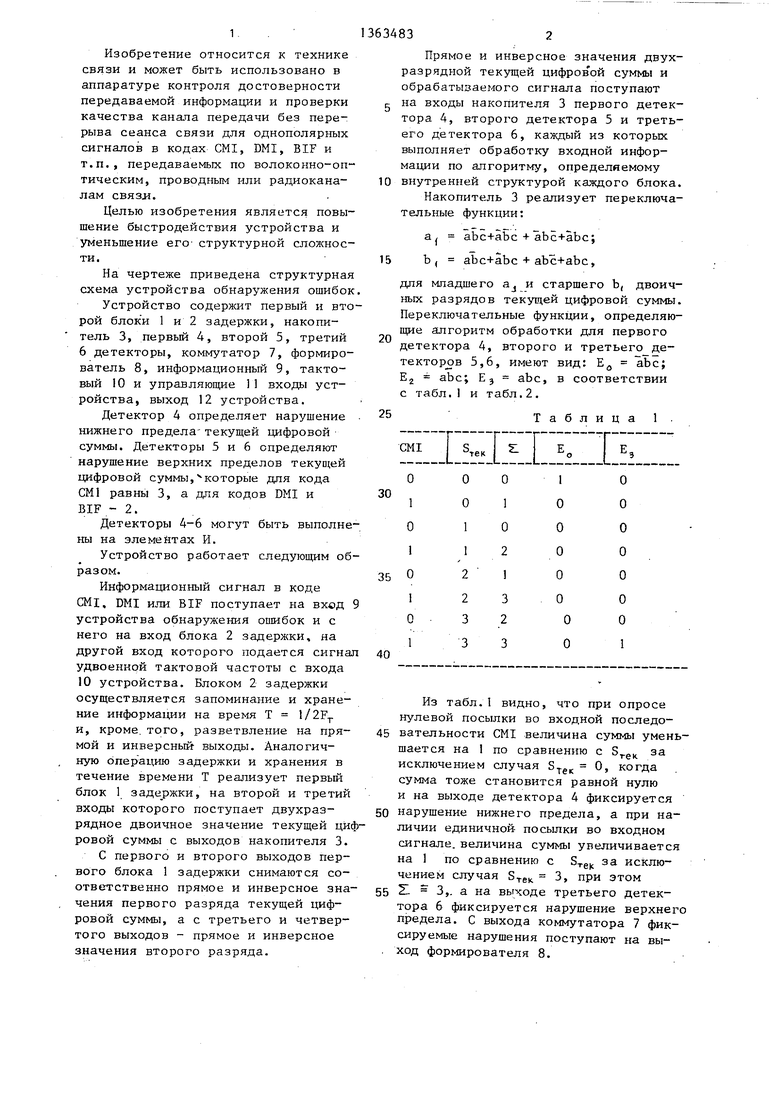

На чертеже приведена структурная схема устройства обнаружения ошибок

Устройство содержит первый и второй блок и 1 и 2 задержки, накопитель 3, первый 4, второй 5, третий 6 детекторы, коммутатор 7, формирователь 8, информационный 9, тактовый 10 и управляющие 11 входы устройства, выход 12 устройства.

Детектор 4 определяет нарушение нижнего предела текущей цифровой суммы. Детекторы 5 и 6 определяют нарушение верхних пределов текуп;ей цифровой суммы, которые для кода СМ1 равны 3, а для кодов DMI и BIF - 2.

Детекторы 4-6 могут быть выполнены на элементах И.

Устройство работает следующим образом.

Информационный сигнал в коде CMI, DMI или BIF поступает на вход устройства обнаружения ошибок и с него на вход блока 2 задержки, на другой вход которого подается сигна удвоенной тактовой частоты с входа 10 устройства. Блоком 2 задержки осуществляется запоминание и хранение информации на время Т 1/2F и, кроме, того, разветвление на прямой и инверсный выходы. Аналогичную операцию задержки и хранения в течение времени Т реализует первый блок 1 задержки, на второй и третий входы которого поступает двухразрядное двоичное значение текущей цировой суммы с выходов накопителя 3.

С первого и второго выходов первого блока 1 задержки снимаются соответственно прямое и инверсное значения первого разряда текущей цифровой суммы, а с третьего и четвертого выходов - прямое и инверсное значения второго разряда.

Прямое и инверсное значения двухразрядной текущей цифровой суммы и обрабатываемого сигнала поступают на входы накопителя 3 первого детектора 4, второго детектора 5 и третьего детектора 6, каждый из которых выполняет обработку входной информации по алгоритму, определяемому внутренней структурой каждого блока.

Накопитель 3 реализует переключательные функции:

а, abc+abc+аЬс+аЬс; Ь, abc+abc- аЪс+аЬс,

дня младшего aj и старшего Ь, двоичных разрядов текущей цифровой суммы. Переключательные функции, определяющие алгоритм обработки для первого детектора 4, второго и третьего де- тектор в 5,6, имеют вид: Е аЬс; Ej abc; Ej abc, в соответствии с табл.1 и табл.2.

25

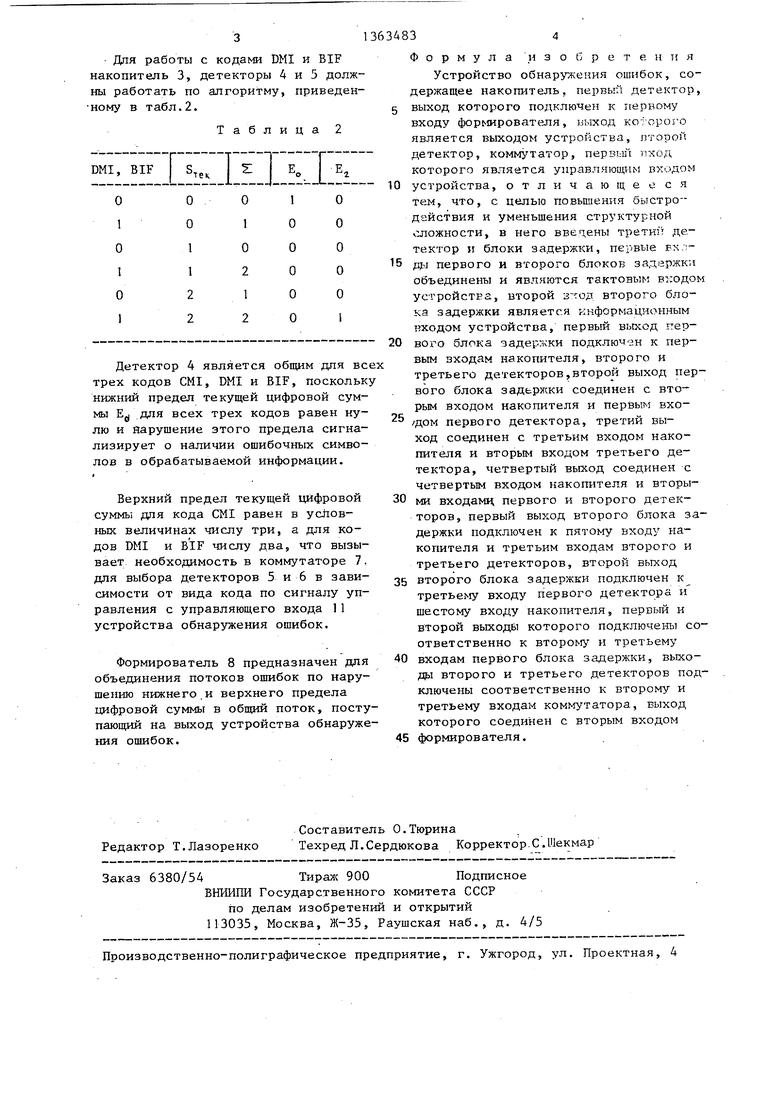

Таблица 1

Из табл. видно, что при опросе нулевой посылки во входной последо- вательности CMI величина суммы уменьшается на I по сравнению с ., за

rt;K

исключением случая О, когда сумма тоже становится равной нулю и на выходе детектора 4 фиксируется

нарушение нижнего предела, а при наличии единичной посылки во входном сигнале, величина суммы увеличивается на 1 по сравнению с за исключением случая Втек 3, при этом

21 3,- а на выходе третьего детектора 6 фиксируется нарушение верхнего предела. С выхода коммутатора 7 фиксируемые нарушения поступают на вы- ход формирователя 8.

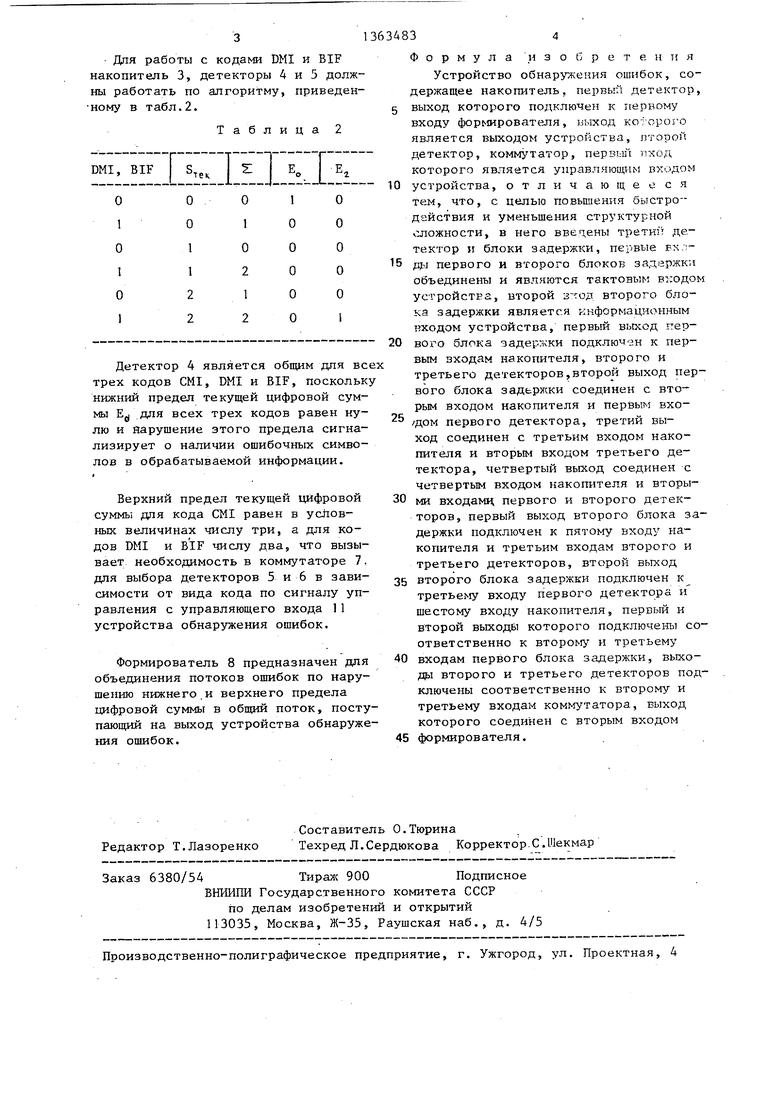

Для работы с кодами DMI и BIF накопитель 3, детекторы 4 и 5 должны работать по алгоритму, приведен- ному в табл.2.

Таблица 2

Детектор 4 является общим для всех трех кодов CMI, DMI и BIF, поскольку нижний предел текущей цифровой суммы Е для всех трех кодов равен нулю и Нарушение этого предела сигнализирует о наличии ошибочных символов в обрабатываемой информации.

Верхний предел текущей цифровой суммы для кода CMI равен в условных величинах числу три, а для кодов DMI и BIF числу два, что вызывает необходимость в коммутаторе 7. для выбора детекторов 5 и 6 в зависимости от вида кода по сигналу управления с управляющего входа 11 устройства обнаружения ошибок.

Формирователь 8 предназначен для объединения потоков ошибок по нарушению нижнего,и верхнего предела цифровой суммы в общий поток, поступающий на выход устройства обнаружения ошибок.

Редактор Т.Лазоренко Заказ 6380/54

Составитель О.Тюрина

Техред Л.Сердюкова Корректор.С.Шекмар

Тиралс 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

0

0

Формула изобретения

Устройство обнаружения ошибок, содержащее накопитель, первый детектор, выход которого подключен к первому входу формирователя, ьыход которого является выходом устройства, пторой детектор, комментатор, первый пход которого является управляющим входом устройства, отличающее с я тем, что, с целью повышения быстродействия и уменьшения структурной олтожности, в него введены третшт детектор л блоки задержки, первые ЕХЛ5 ды первого и второго блоков задержки объединены и являются тактовым в содом устройства, второй з:тод второго блока задержки является информационным входом устройства, первый выход первого блока задержки подключ зн к первым входам накопителя, второго и третьего детекторов,второй выход первого блока задержки соединен с вторым входом накопителя и первым вхо /дом первого детектора, третий выход соединен с третьим входом накопителя и вторым входом третьего детектора, четвертый выход соединен с Четвертым входом накопителя и вторыми входами первого и второго детекторов, первый выход второго блока задержки подключен к пятому входу накопителя и третьим входам второго и третьего детекторов, второй выход

5 второго блока задержки подключен к третьему входу первого детектора и шестому входу накопителя, первый и второй выходб которого подключеш соответственно к BTOpoNsy и третьему

0 входам первого блока задержки, выходы второго и третьего детекторов подключены соответственно к второму и третьему входам коммутатора, выход которого соединен с вторым входом

5 формирователя.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок цифрового сигнала | 1985 |

|

SU1334377A1 |

| Устройство для обнаружения ошибок цифрового сигнала в контролируемых кодах | 1988 |

|

SU1656688A1 |

| Устройство для обнаружения ошибок цифрового сигнала | 1981 |

|

SU1012451A1 |

| Система передачи телевизионного сигнала с помощью дифференциальной импульсно-кодовой модуляции | 1983 |

|

SU1107342A2 |

| Система контроля качества прохождения телеграфных сигналов | 1986 |

|

SU1540023A1 |

| Система передачи и приема телевизионного сигнала с помощью дифференциальной импульсно-кодовой модуляции | 1982 |

|

SU1104690A1 |

| Устройство приема телевизионного сигнала с дифференциальной импульсно-кодовой модуляцией | 1987 |

|

SU1434563A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| СПОСОБ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107334C1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

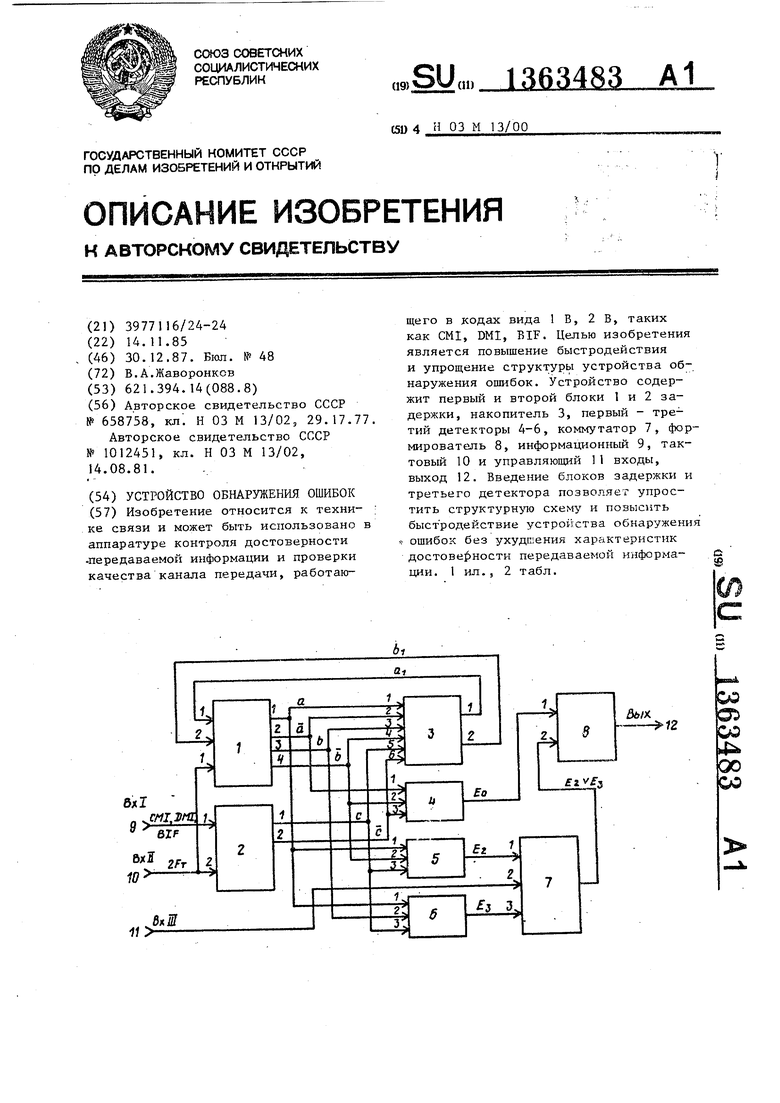

Изобретение относится к техни- ; ке связи и может быть использовано в аппаратуре контроля достоверности -передаваемой информации и проверки качества канала передачи, работающего в кодах вида 1 В, 2 В, таких как CMI, DM1, BIF. Целью изобретения является повышение быстродействия и упрощение структуры устройства обнаружения ошибок. Устройство содержит первый и второй блоки 1 и 2 задержки, накопитель 3, первый - третий детекторы 4-6, коммутатор 7, формирователь 8, информационный 9, тактовый 10 и управляющий 11 входы, выход 12. Введение блоков задержки и третьего детектора позволяет упростить структурную схему и повысить быст родействие устройства обнаружения ошибок без ухудшения характеристик достове ности передаваемой информации. I ил., 2 табл. с SS дых. со 05 со 4 оо оэ

| Устройство обнаружения ошибок при приеме псевдотроичного сигнала | 1977 |

|

SU658758A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для обнаружения ошибок цифрового сигнала | 1981 |

|

SU1012451A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-12-30—Публикация

1985-11-14—Подача