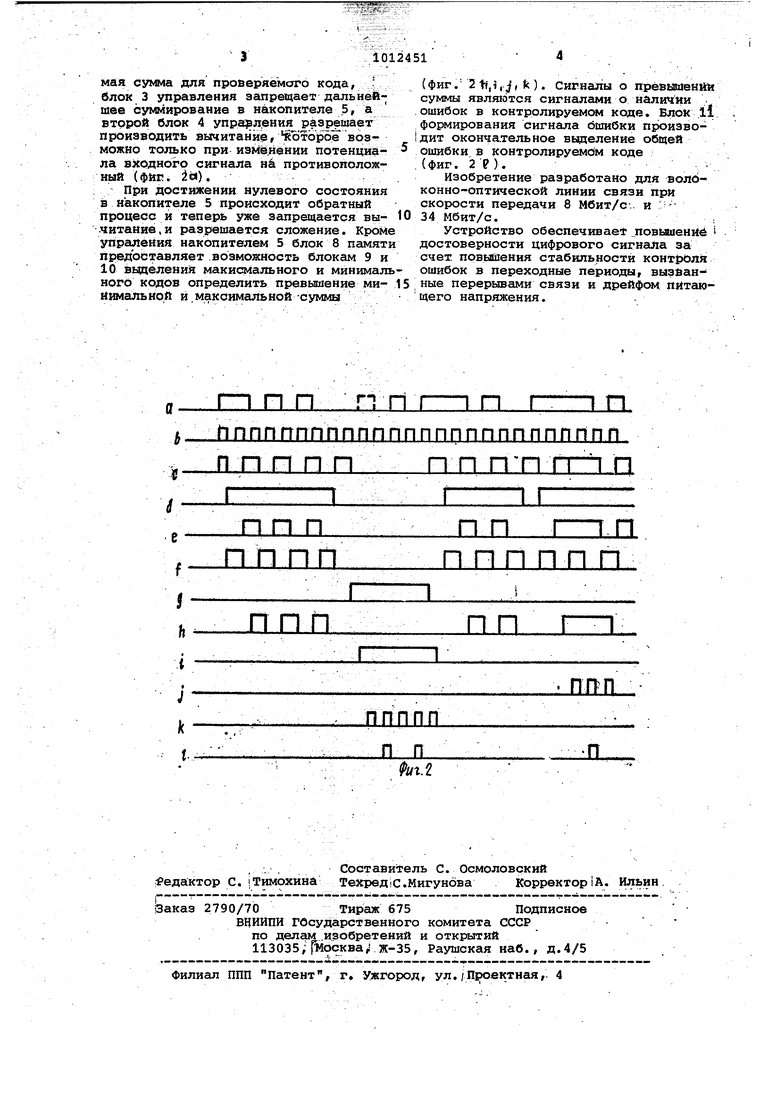

Изобретение относится к техникесв зи и может быть использовано в цифровых ;линиях связи для контроля линейного сигнала, передаваемого в кодах В I Р,ДМ1 и CMJ . Извесно устройство для обнаружения ошибок цифрового сигнала, содер жащее блок управления, выход которо го подключен к первому входу накопи теля, а также блок памяти, первый вход которого является первым входо устройства Cl. Однако известное устройство хара теризуется недостаточной достоверностью цифрового сигнала. Цель изобретения - повышение дос товерности цифрового сигнала. Поставленная цель достигается .. тем, что в устройство для обнаружен ошибок цифрового сигнала, содержаиде первый блок управления, выход которого подключен к первому входу нако пителя, а также блок памяти, первый ,. вход которого является первым вхо, дом устройства, введены первый и второй преобразователи, второй блок управления, дешифратор, коммутатор, блоки выделения максшлального и минимального кодов, выходы которьах. подключены к входам блока формирова ния сигнала ошибки, при этом выход первого преобразователя вход которо го соединен с первым входом устройства, подключен к второму входу накопителя и к первым входам блоков вьщеления максимального и минимальн го кодов, Kt вторым входам которых подключены первый и второй выходы накопителя, третий и четвертый выходы которого подключены к первым входам первого и второго блоков управления, выход второго преобразо вателя подключен к второму входу первого блока управления и к третьему входу блока вьщеления минимального кода, а вход второго преоб разователя объединен с третьим входом блока выделения максимального кода и вторым входом второго блока управления и является вторым входом устройства, при этом выход второго блока управления подключен к третье му входу накопителя, выходы которог подключены к входам дешифратора, выходы которого непосредственно и через коммутатор подключены к второ и третьему входам блока памяти, а третий вход коммутатора является третьим входом устройства. На фиг, 1 представлена структурная схема устройства для обнаружения ошибок цифрового сигнала; на фиг. 2 - временные диаграммы, иллюстрирующие работу устройства. Устройство для обнаружения ошибо цифрового сигнала содержит первый преобразов,атель 1, второй преобразователь 2, первый блок 3 управления, второй блок 4 управления)накопитель 5, дешифратор б, коммутатор 7,. блок 8 памяти, блок 9 выделения максимального кода, блок Ю.вьвделенрш минимального кода, блок 11 формирования сигнала ошибки; 1, О I Ш входы устройства. Обнаружение ошибки в цифровом сигнале основано на контроле наруша- ния закона максимальной суммы импульсов полут жтовых интервалов. Для кодов В IfF и ДМ1 сугима шлпульсов в любой MONJfeHT времен не должна превышать величину два, для кода СМ1максимальная сумма не превышает трех. Устройство работает следующий образом. На вход I подается последовательность импульсов с частотой следования, равной двойной тактовой частоте (фиг. 2 ё ) , на вход iT подается информационная последовательность цифровых сигналов (фиг. 2«). С выхода первого преобразователя 1 на второй вход накопителя 5 поступают импульсы двойной тактовой частоты в инверсном виде, а на первый и третий входы накопителя 5 поступают разрешающие сигналы. При наличии положительного потенциала на первом входе накопителя 5 в ней происходит процесс сложения поступающих на второй вход импульсов. При наличии положительного потенциала на третьем входе накопителя 5 в нем идет обратный процесс - вычитание из записанной сутлы импульсов, поступающих на третий вход Ш устройства. Итоги работы накопителя 5 отражаются на его выходах с первого по четвертый (фиг. 2 с и-3). Дешифратор б предназначен для определения состояния накопителя 5, в частности сигнал на втором выходе (фиг.2е) свидетельствует о наличии в накопителе 5 суммы, равной трем. Третий выход дешифратора б свидетельствует о наличии- , равной двум (фиг. 2-f) « Первый выход дешифратора б свидетельствует о наличии нуля (фиг. 2ог} , Вся эта информация поступает в блок памяти 8 для последующего анализа. На третий вход блока 8 памяти поступает один из двух сигнсшов дешифратора б в зависимости от состояния входа Ш устройства,При наличии прложительного потенциала на входе Ш коммутатор 7 пропускает сигнал-co второго выхода дешифратора б, что соответствует анализу кодаСМ, ПриЪалйчйи отрицательного потенциала на входёПГ когимутатор 7 пропускает сигнал стретьего выхода дешифратора б, что соответствует режшлу проверни кодов СМ1 и BIF. .После того, как в блоке 8 памяти зафиксирована максимально допустимая сумма для проверяемого кода, блок 3 зтравления запрещает дальнейшее суммирование в накопителе 5, а второй блок 4 упрафления производить вычитание, RoToipoe возможно только при изменении потенциала входного сигнала н4 противоположный (фЙЕ. ЙЙ).: .

При достижении нулевого состояния в накопителе 5 происходит обратный процесс и теперь уже запрещается вы- 10 .читание.и разрешается сложение. Кроме упраления накопителем 5 блок 8 памяти предоставляет возможность блокам 9 и 10 вьщеления макисмального и минимального кодов определить превышение ми- 15 Нимальной и.максимальной -суммы

(фиг. 2 tf,i,,( k ). Сигналы о превышений суммы явлшотся сигналами о ИИ ошибок в контролируемом коде. Блок 11 формирования сигнала бшибки произво1дит окончательное выделение общей ошибки в контролируемом коде

: (фиг. 2р).

Изобретение разработано для волоконно-оптической линии связи при скорости передачи 8 Мбит/с-, и -

34 Мбит/с.;

Устройство обеспечивает повышение достоверности цифрового сигнала за счет повышения стабильности ошибок в переходные периоды, вызванные перерьшами связи и дрейфом пйтающего напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок цифрового сигнала | 1985 |

|

SU1334377A1 |

| Устройство для обнаружения ошибок цифрового сигнала в контролируемых кодах | 1981 |

|

SU959289A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для сбора аналоговой информации с сеточной электромодели | 1980 |

|

SU974377A2 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство телеконтроля линейных трактов цифровых систем передачи | 1985 |

|

SU1241494A1 |

| СПОСОБ ХРАНЕНИЯ ДАННЫХ С АВТОНОМНЫМ КОНТРОЛЕМ И УСТРОЙСТВО ДЛЯ ИХ ХРАНЕНИЯ | 2003 |

|

RU2259606C2 |

| Модульное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1320848A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК ЦИФРОВОГО СИГНАЛА, содержащее первый блок управления, выход которого подключен к первсялу входу накопителя, а также блок памяти, первый вход которого является первшл входом устройства, отличающее с я тем, что, с целью повышения достоверности цифрового сигнала, введены первый и второй преобразователи, второй блок управления, дешифратор, коммутатор, блоки ввщеления максимального и минимального кодолё, выходы которых подключены к входам блока формирования сигнала ошибки, при этом выход первого преобразова- Теля, вход которого соединен с первым входом устройства, подключен к второму входу накопителя и к первым входам блоков вьщеления максимального и минимального кодов, к вторьм входам которых подключены первый и второй выходы накопителя, третий и четвертый выходы которого подключены к первым входам первого и второго блоков управления, выход второго преобразователя подключен к второму входу первого блока управления и третьему входу блока выделения минимального кода, а вход-. второго преобразователя объединен с третьим входом блока, вьщеления максимального кода и вторым входом g второго блока управления и является торьии входом устройства, при этом выход второго блока управления подключен к третьему входу накопителя, выходы которого подключены к входам дешифратора, выходы которого непосредственно и через коммутатор подключены к второму и третьему входам блока памяти, а третий вход ; коммутатора является третьим входом устройства. ISD 4 сл 0

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ИЗВЛЕЧЕНИЯ РЕДКОЗЕМЕЛЬНЫХ ЭЛЕМЕНТОВ ИЗ ЖИДКИХ СПЛАВОВ С ЦИНКОМ | 2012 |

|

RU2522905C1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-04-15—Публикация

1981-08-14—Подача