о ел о- а

00 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок цифрового сигнала | 1985 |

|

SU1334377A1 |

| Устройство для обнаружения ошибок | 1985 |

|

SU1363483A1 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2168270C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ КАНАЛЬНОГО КОДА | 2012 |

|

RU2521299C1 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| Устройство для приема относительного биимпульсного сигнала | 1989 |

|

SU1672578A1 |

| Преобразователь двоичной последовательности в дуобинарную | 1987 |

|

SU1450087A2 |

| Устройство для приема относительного биимпульсного сигнала | 1988 |

|

SU1614117A1 |

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ | 2002 |

|

RU2215369C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре контроля качества передачи кодированных цифровых сигналов. Цель изобретения - расширение функциональных возможностей за счет обнаружения ошибок в цифровых сигналах представленных в коде В IF, DMI или CMI. Устройство содержит первый-пятый D- триггеры 1-5, первый 6 и второй 7 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 8 и второй 9 элементы И, информационный вход 10, прямой 11 и инверсный 12 такУовые входы, выход 13 устройства. 3 ил.

Щиг.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре контроля качества передачи кодированных цифровых сигналов.

Цель изобретения - расширение функциональных возможностей за счет обнаружения ошибок в цифровых сигналах, представленных в коде BIF, DMI или CMI.

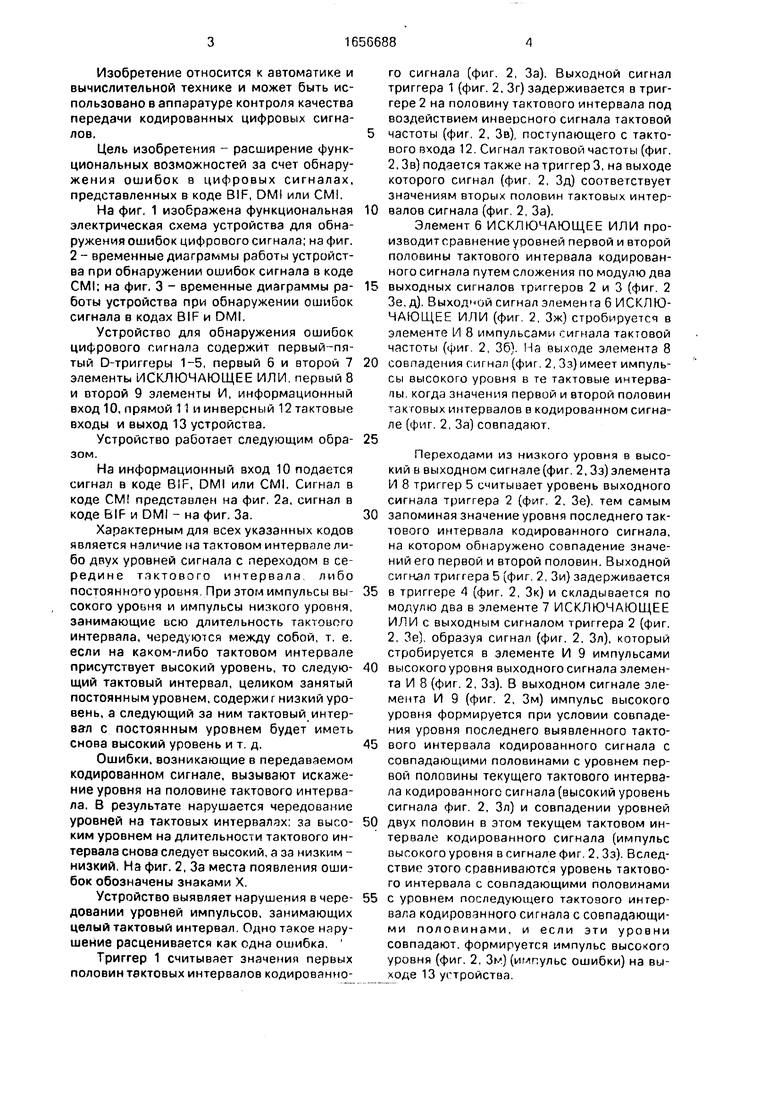

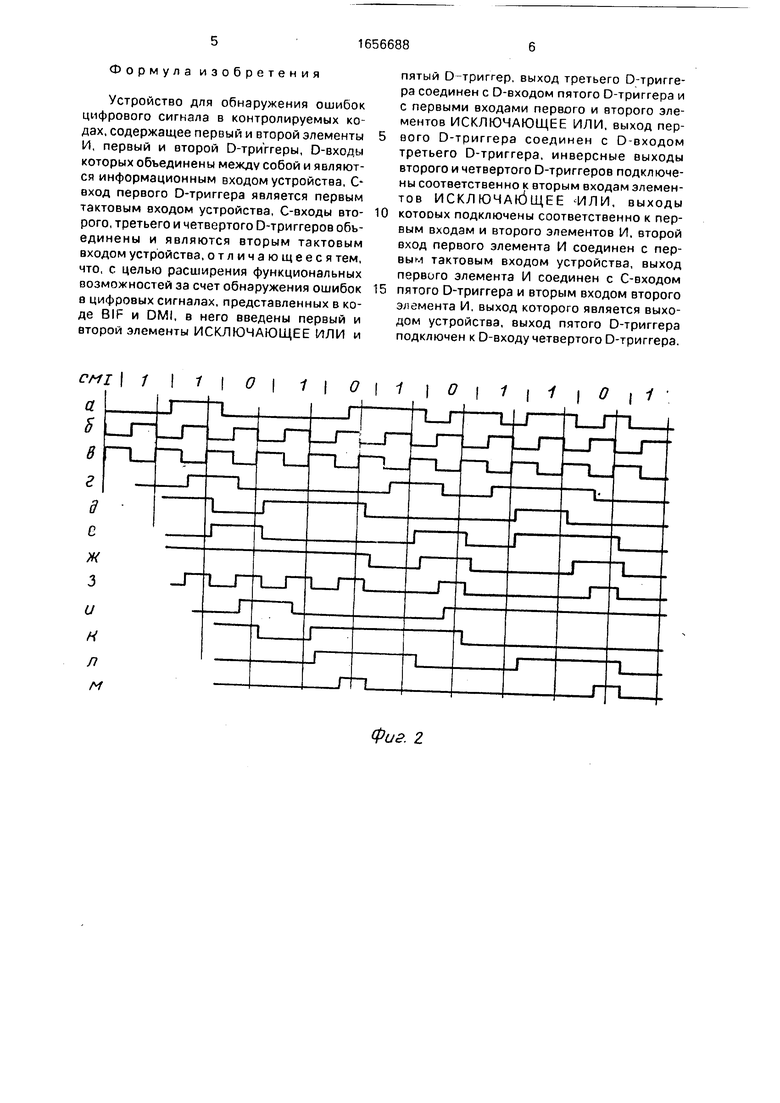

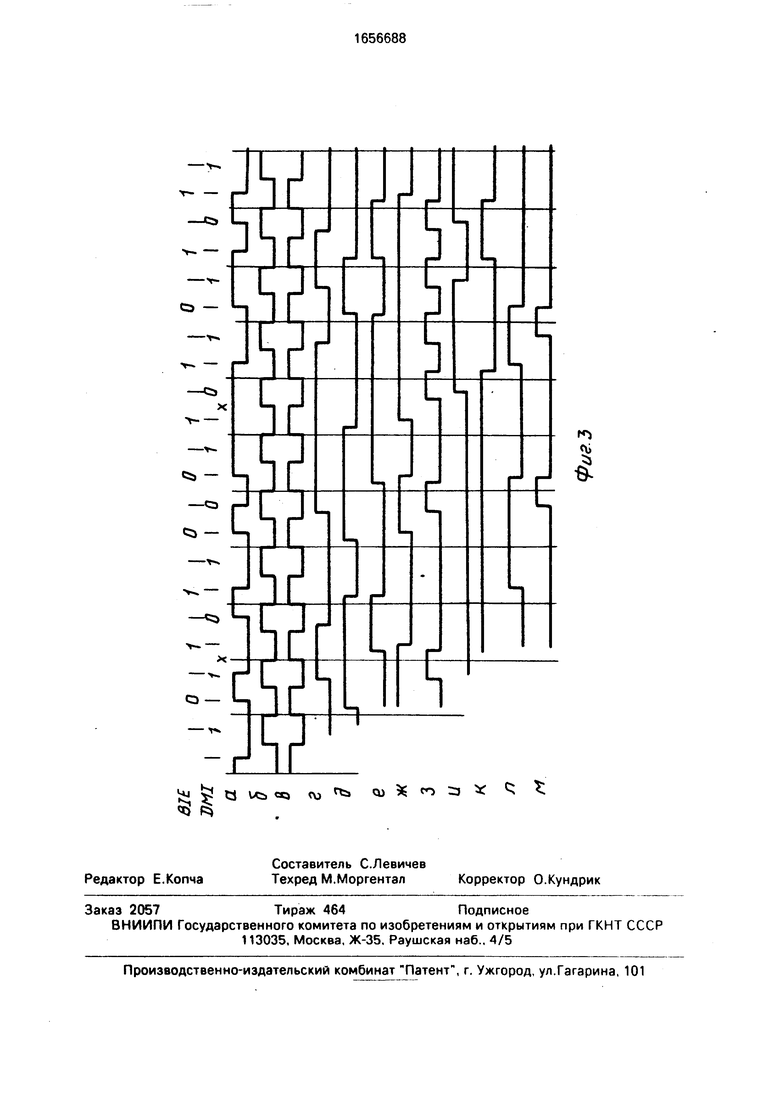

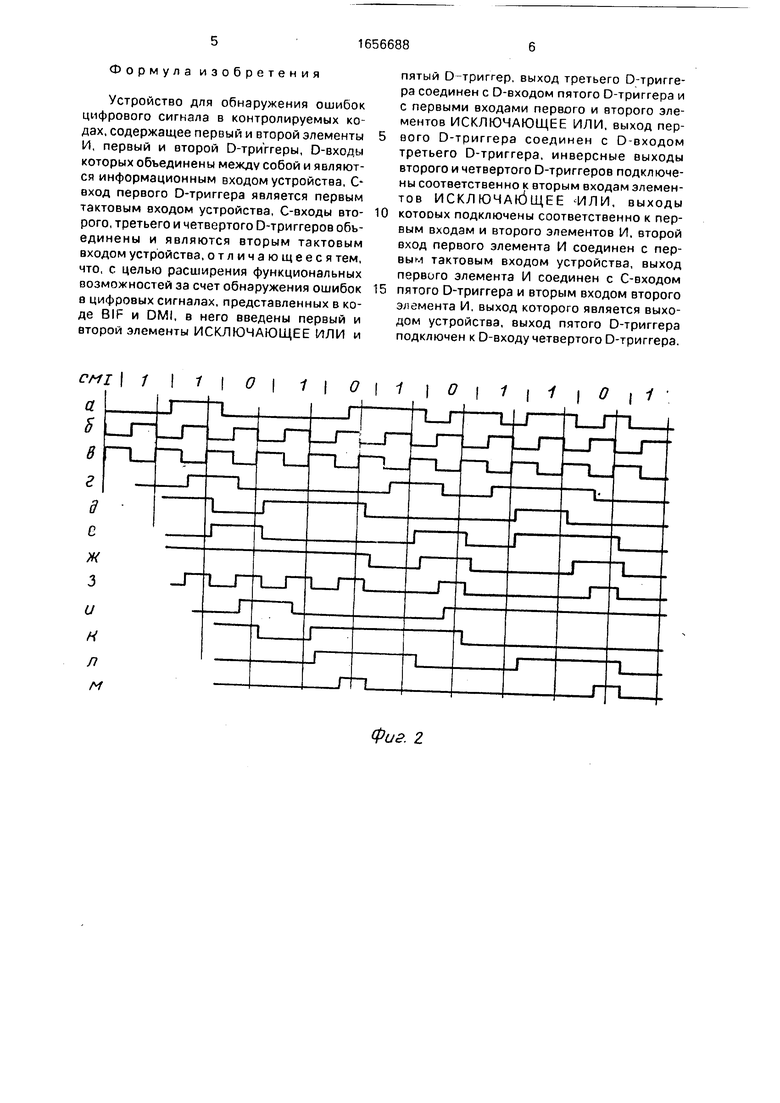

На фиг. 1 изображена функциональная электрическая схема устройства для обнаружения ошибок цифрового сигнала; на фиг. 2 - временные диаграммы работы устройства при обнаружении ошибок сигнала в коде CMI; на фиг. 3 - временные диаграммы работы устройства при обнаружении ошибок сигнала в кодах BIF и DMI.

Устройство для обнаружения ошибок цифрового сигнала содержит первый-пя- тый D-триггеры 1-5, первый 6 и второй 7 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 8 и второй 9 элементы И, информационный вход 10, прямой 11 и инверсный 12 тактовые входы и выход 13 устройства.

Устройство работает следующим образом.

На информационный вход 10 подается сигнал в коде BIF, DMI или CMI. Сигнал в коде СМ представлен на фиг. 2а, сигнал в коде BIF и DMI - на фиг. За.

Характерным для всех указанных кодов является наличие на тактовом интервале либо двух уровней сигнала с переходом в се- редине тактового интервала либо постоянного уровня. При этом импульсы высокого уровня и импульсы низкого уровня, занимающие всю длительность тактового интервала, чередуются между собой, т. е. если на каком-либо тактовом интервале присутствует высокий уровень, то следующий тактовый интервал, целиком занятый постоянным уровнем, содержит низкий уровень, а следующий за ним тактовый интер- ва-л с постоянным уровнем будет иметь снова высокий уровень и т. д.

Ошибки, возникающие в передаваемом кодированном сигнале, вызывают искажение уровня на половине тактового интервала. В результате нарушается чередование уровней на тактовых интервалах: за высоким уровнем на длительности тактового интервала снова следует высокий, а за низким - низкий, На фиг. 2, За места появления ошибок обозначены знаками X,

Устройство выявляет нарушения в чередовании уровней импульсов, занимающих целый тактовый интервал. Одно такое нарушение расценивается как одна ошибка.

Триггер 1 считывает значения первых половин тактовых интервалов кодированного сигнала (фиг. 2, За). Выходной сигнал триггера 1 (фиг. 2, Зг) задерживается в триггере 2 на половину тактового интервала под воздействием инверсного сигнала тактовой

частоты (фиг. 2, Зв), поступающего с тактового входа 12. Сигнал тактовой частоты (фиг. 2, Зв) подается также на триггер 3, на выходе которого сигнал (фиг. 2. Зд) соответствует значениям вторых половин тактовых интер0 валов сигнала (фиг. 2, За).

Элемент 6 ИСКЛЮЧАЮЩЕЕ ИЛИ про- изводитсравнение уровней первой и второй половины тактового интервала кодированного сигнала путем сложения по модулю два

5 выходных сигналов триггеров 2 и 3 (фиг. 2 Зе, д). Выходной сигнал элемента 6 ИСКЛЮЧАЮЩЕЕ ИЛИ (фиг. 2, Зж) стробируется в элементе И 8 импульсами сигнала тактовой частоты (фиг. 2, 36). На выходе элемента 8

0 совпадения сигнал (фиг. 2, Зз) имеет импульсы высокого уровня в те тактовые интервалы, когда значения первой и второй половин актовых интервалов в кодированном сигнале (фиг. 2, За) совпадают.

5

Переходами из низкого уровня в высокий в выходном сигнале (фиг. 2, Зз) элемента И 8 триггер 5 считывает уровень выходного сигнала триггера 2 (фиг. 2. Зе). тем самым

0 запоминая значение уровня последнего тактового интервала кодированного сигнала, на котором обнаружено совпадение значений его первой и второй половин. Выходной сигнал триггера 5 (фиг. 2, Зи) задерживается

5 в триггере 4 (фиг. 2, Зк) и складывается по модулю два в элементе 7 ИСКЛЮЧАЮЩЕЕ ИЛИ с выходным сигналом триггера 2 (фиг. 2, Зе), образуя сигнал (фиг. 2. Зл), который стробируется в элементе И 9 импульсами

0 высокого уровня выходного сигнала элемента И 8 (фиг. 2, Зз). В выходном сигнале элемента И 9 (фиг. 2, Зм) импульс высокого уровня формируется при условии совпадения уровня последнего выявленного такто5 вого интервала кодированного сигнала с совпадающими половинами с уровнем первой половины текущего тактового интервала кодированного сигнала(высокий уровень сигнала фиг. 2, Зл) и совпадении уровней

0 двух половин в этом текущем тактовом интервале кодированного сигнала (импульс нысокого уровня в сигнале фиг. 2, Зз). Вследствие этого сравниваются уровень тактового интервала с совпадающими половинами

5 с уровнем последующего тактового интервала кодированного сигнала с совпадающими половинами, и если эти уровни совпадают, формируется импульс высокого уровня (фиг. 2, Зм) (импульс ошибки) на выходе 13 устройства.

Формула изобретения

Устройство для обнаружения ошибок цифрового сигнала в контролируемых кодах, содержащее первый и второй элементы И, первый и второй D-трштеры, 0-входы которых объединены между собой и являются информационным входом устройства, С вход первого D-триггера является первым тактовым входом устройства, С-входы второго, третьего и четвертого D-триггеров обь- единены и являются вторым тактовым входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обнаружения ошибок в цифровых сигналах, представленных в коде BIF и DMI, в него введены первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и

CHI

а 5

В г

д с ж

3

и

н

л

м

1

пятый D-триггер, выход третьего D-триггера соединен с D-входом пятого D-триггера и с первыми входами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого D-триггера соединен с D-входом третьего D-триггера, инверсные выходы второго и четвертого D-триггеров подключены соответственно к вторым входам элемен- тов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы

котооых подключены соответственно к первым входам и второго элементов И, второй вход первого элемента И соединен с первым тактовым входом устройства, выход первого элемента И соединен с С-входом

пятого D-триггера и вторым входом второго элемента И, выход которого является выходом устройства, выход пятого D-триггера подключен к D-входу четвертого D-триггера.

Фиг. 2

П X

Ј

| Авторское свидетельство СССР № 1295525 | |||

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для обнаружения ошибок цифрового сигнала в контролируемых кодах | 1984 |

|

SU1290539A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-06-15—Публикация

1988-07-11—Подача